图1 QVCO的两种耦合结构

戚玉华,何如龙

(海军工程大学电子工程学院,湖北武汉430033)

摘 要:基于标准0.18μm CMOS工艺,提出并验证了一种改进的用于多相位振荡器的耦合方法。将一种先进的自注入耦合(SIC)技术,用于耦合两个电流复用差分压控振荡器(VCO)。相比较于传统的并联耦合正交VCO(QVCO)而言,所提出的采用SIC技术的QVCO在没有增加功耗的前提下,表现出了更低的相位噪声。所提出的SIC-QVCO在16.41 GHz振荡频率下,相位噪声为-119.7 dBc/Hz@1 MHz,并且调谐范围高达1.66 GHz,直流电源电压和电流分别为1.8 V和5.28 m A,芯片尺寸为0.3 mm×0.9 mm。

关键词:相位噪声;自注入耦合;正交压控振荡器;振幅误差;相位误差

在过去数十年,正交压控振荡器(QVCO)得到了快速发展,尤其在直接下变频接收机中应用越加广泛。鉴于QVCO通常用于为特定的调制和混频操作提供正弦本振信号,这就要求QVCO的输出信号具有较低的相位噪声。迄今为止,出现了一些基于变压器反馈的QVCO[1-2]和差分VCO[3-4],由于此类结构输出摆幅得到了增加,进而降低了相位噪声。然而,在片变压器的芯片面积较大,并且随着频率的增加品质因数降低,限制了电路相位噪声的降低。由于电路易于实现,串联耦合QVCO(S-QVCO)和并联耦合QVCO(P-QVCO)也得到了广泛的应用[5-8],但是,由于S-QVCO需要叠加耦合晶体管,限制了其在低电压下的应用,而P-QVCO的相位噪声和功耗性能都较差。虽然源端注入P-QVCO(SIPC-QVCO)相比较于传统的P-QVCO而言,可以得到较低的相位噪声,但是SIPC-QVCO结构的功耗仍然很大[9]。

本文提出了一种采用改进自注入耦合技术(SIC)的电流复用拓扑结构,以降低电路的功耗。而且,鉴于没有耦合晶体管的闪烁噪声电流流经电感电容LC谐振回路,所提出的SIC-QVCO取得了-119.7 dBc/Hz@1 MHz的较低相位噪声。

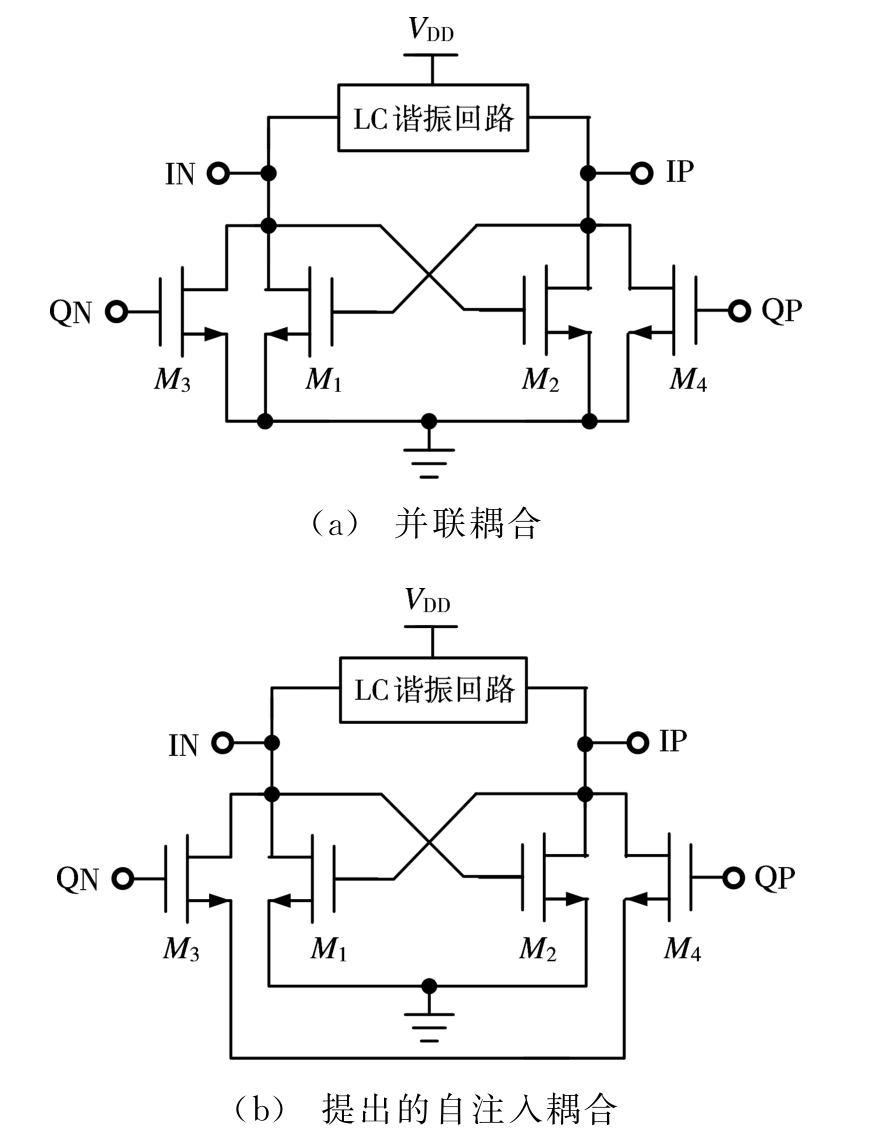

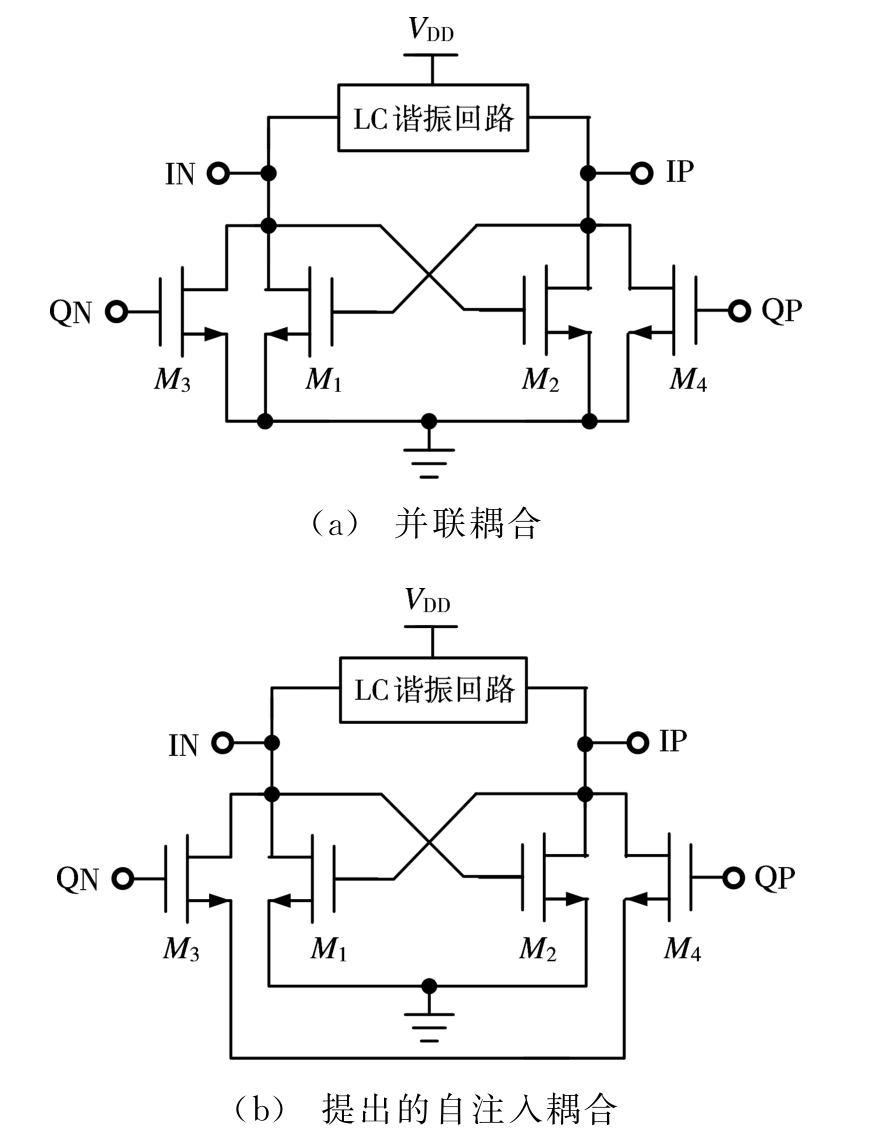

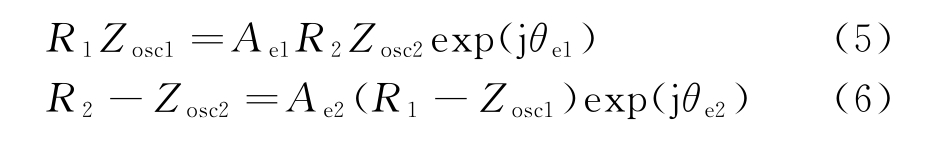

图1给出了两种QVCO的耦合拓扑结构:图1(a)为传统并联耦合结构;图1(b)为本文提出的SIC结构。SIC-QVCO的电路图由传统的P-QVCO改进而来,对于P-QVCO和SIPC-QVCO而言,由于耦合晶体管的源极端口与地相连,使得耦合晶体管消耗额外的直流电流。然而,本文所提出的SIC-QVCO中两个耦合晶体管的源极相连,代替与地的连接,没有到地的直流通路,因此SIC-QVCO消耗的功耗更低。

图1 QVCO的两种耦合结构

SIC-QVCO由两个相同的差分VCO组成,这两个VCO通过注入器件(M3和M4)实现两者之间的相互耦合,SIC-QVCO正弦信号产生的耦合机制与P-QVCO类似。所提出的SIC-QVCO的等效半边电路如图2所示,包含负阻-R、LC回路的等效阻抗Zosc,以及耦合晶体管的压控电流源。

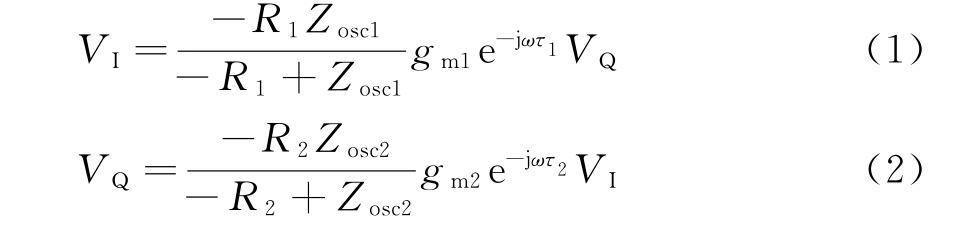

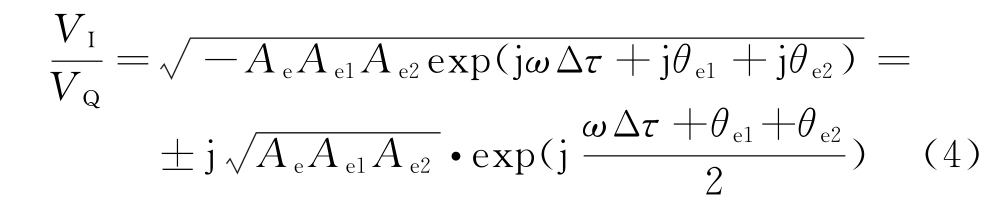

假设两个VCO同步输出相同的振荡频率,可得这两个差分VCO的输出电压为

式中,ω为振荡角频率,gm和τ分别为晶体管跨导和跨导延迟时间。由式(1)和式(2)可得

由于两个差分VCO交叉连接并且耦合晶体管的不匹配性,本文引入表达式gm1=-Aegm2和τ2-τ1=Δτ,其中Ae和Δτ分别为跨导器和跨导延迟时间的非匹配因子。进而,式(3)可重写为

式中,

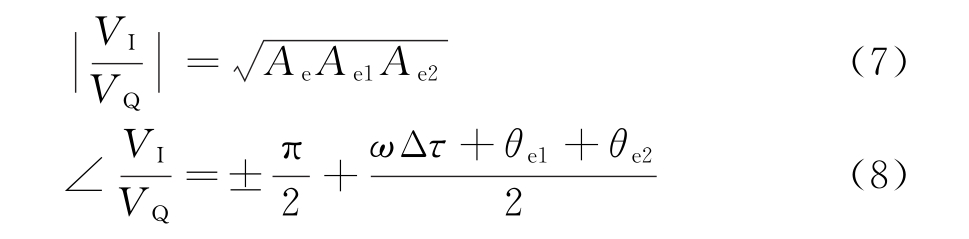

式中,Ae1,Ae2分别为负电阻-R1和-R2的振幅,θe1为负电阻-R1和LC谐振回路的相位失配量,θe2为负电阻-R2和LC谐振回路的相位失配量。进而,可由式(4)推得这两个VCO的幅度误差和相位误差分别为

由式(7)和式(8)可见,幅度误差较小,但是鉴于ωΔτ≪1°,相位误差受控于负电阻和LC谐振回路的非匹配因子θe1和θe2。

图2 本文提出的SIC-QVCO的等效半边电路

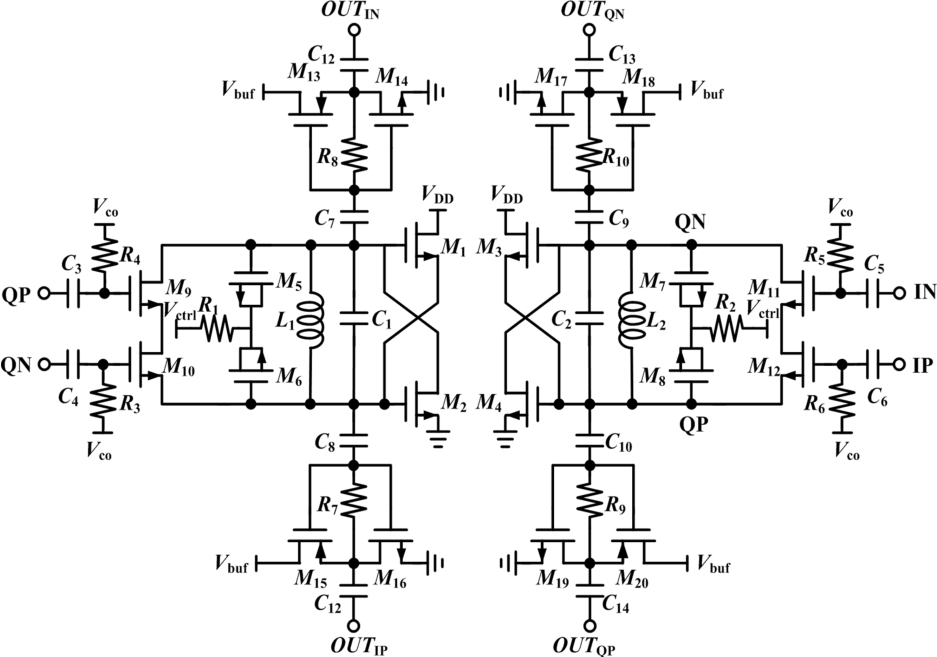

采用台湾的TSMC 0.18μm 1P6M CMOS工艺对本文的SIC-QVCO进行设计与流片,该工艺中的NMOS晶体管的最高振荡频率fmax为70 GHz,单位电流增益频率fT为20 GHz。另外该CMOS工艺所包含的无源元件有MIM电容、螺旋电感以及多晶硅薄膜电阻。为了进一步降低衬底损耗以及耦合效应,在版图设计中采用微带线连接,上层金属作为信号线,下层金属作为地平面。

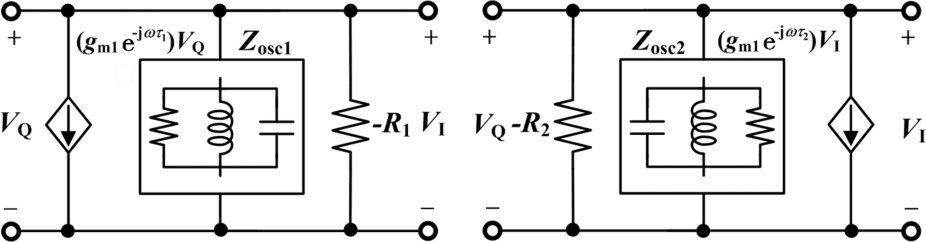

图3所示为本文提出的电流复用SIC-QVCO电路图,包含2个电流复用差分VCO、4个耦合晶体管和4个反向缓冲放大器。采用电流复用结构的交叉耦合晶体管对M1-M2和M3-M4产生负阻,以补偿LC谐振回路的损耗。正交输出信号由两个复用差分VCO之间的耦合产生,并且这两个VCO通过SIC晶体管对M9-M10和M11-M12耦合,此类结构中,没有耦合晶体管的闪烁噪声电流流经LC谐振回路,因而,相比较于传统的P-QVCO结果而言,所提出的SIC-QVCO具有更低的相位噪声。为了进一步降低该结构的正交相位误差,并且鉴于NMOS和PMOS晶体管两者之间的跨导不匹配,将PMOS晶体管的栅宽设置成NMOS晶体管栅宽的2.7倍大小。

图3 本文提出的电流复用SIC-QVCO

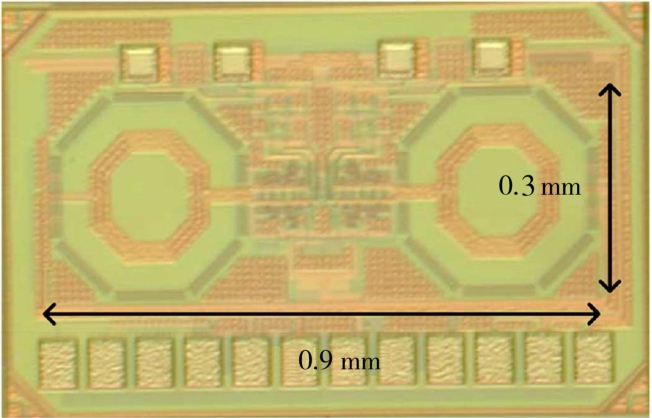

由于版图布局对SIC-QVCO的振幅和相位误差影响较大,因此需要认真布局,将耦合信号的连接考虑在内。在所有路径中,尽量保持差分信号线对称设计以确保等同的相位延迟,采用反向放大器放大正交输出信号以降低负载效应,在芯片输入输出端口插入旁路电容以增强射频信号和直流信号间的隔离度。版图中所有的无源元件包括传输线、MIM电容以及螺旋电感,都采用Sonnet软件对其进行全波电磁场仿真。图4给出了SIC-QVCO芯片的微照片,芯片大小为0.3 mm×0.9 mm。

图4 所提出SIC-QVCO的芯片微照片

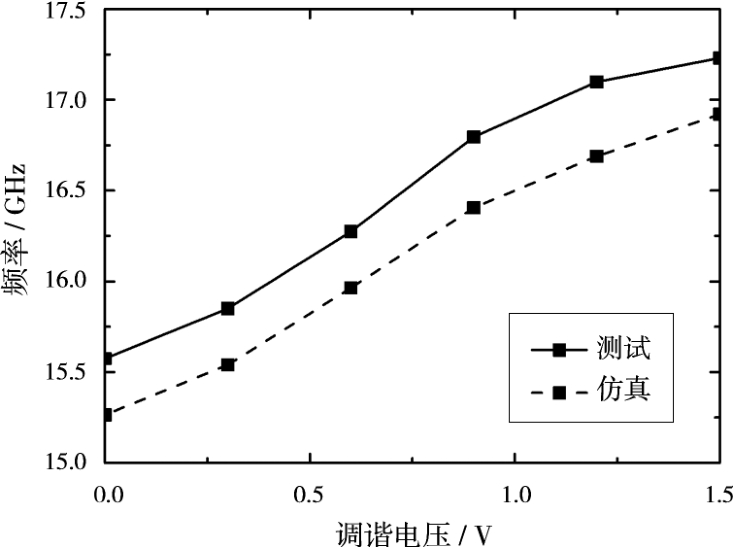

采取在片测试的方式对本文所设计的SIC-QVCO的性能进行评估,此芯片在1.8 V电压供电下,消耗的功耗为9.5 m W,采用Agilent N9030A频谱分析仪测试该芯片的输出频谱和相位噪声。图5给出了振荡频率的仿真结果和测试结果对比,振荡频率的测试结果(15.57~17.23 GHz)与仿真结果(15.26~16.72 GHz)相差较小,测试结果表明SIC-QVCO在16.4 GHz的中心振荡频率下,取得了10.1%的调谐范围。由图5可见,振荡频率的测试结果,比仿真结果整体略高,原因可能在于电感模型的仿真结果相比较于实测结果略大,导致仿真得到的振荡频率略低。

图5 振荡频率的仿真和测试结果

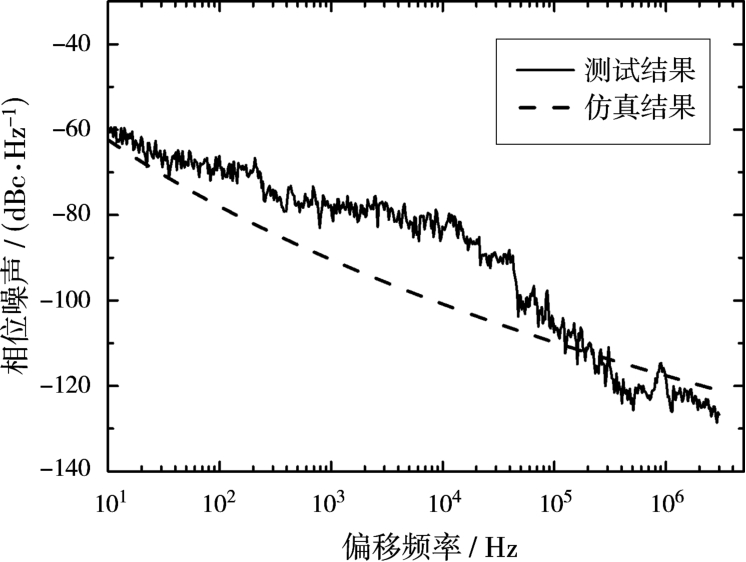

图6为输出功率的测试结果,可见输出功率在整个振荡频率范围内,均大于-6 dBm,可有效地驱动收发机中的下一级混频器电路。图7给出了在振荡频率16.41 GHz处相位噪声的测试结果与仿真结果,可见测试得到的相位噪声低至-119.7 dBc/Hz@1 MHz,并且仿真结果与测试结果基本保持一致,但是也存在些许的偏差,这可能是由于MOS晶体管的噪声模型不够精确导致的结果。

图6 输出功率的测试结果

图7 相位噪声的仿真和测试结果

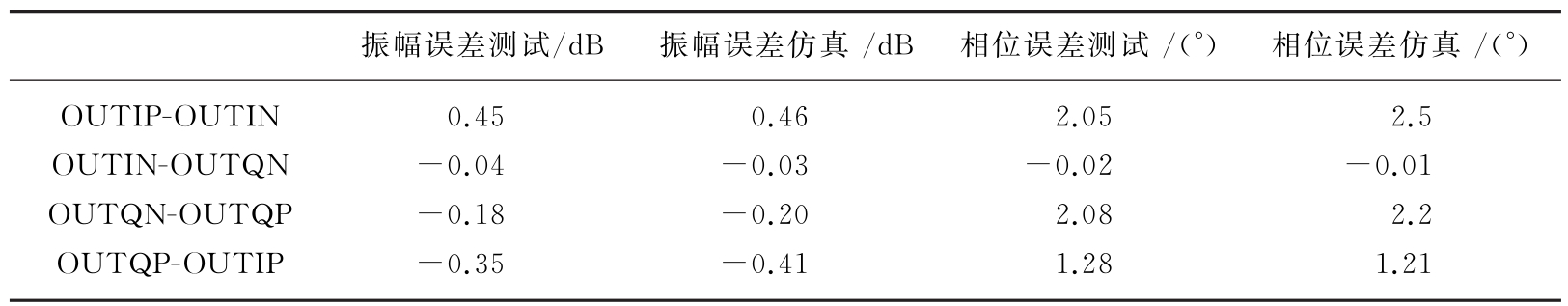

采用操作于接收模式下的Agilent N5245A PNA-X网络分析仪对振幅和相位误差进行测试。表1总结了测试得到的振幅和相位误差的结果,并且增加了相应的仿真结果对比,可见测试得到的振幅误差的最小值和最大值分别为0.04 d B和0.45 d B,相位误差的最小值和最大值分别为0.02°和2.08°,实现了较低的振幅和相位误差值,取得了较优良的正交输出信号。

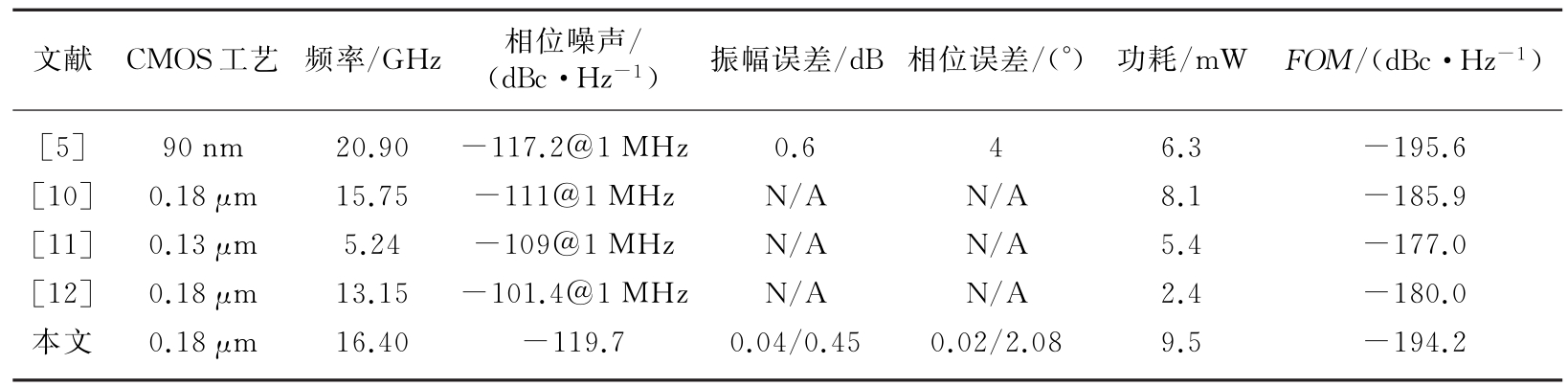

为了验证本文所提出电路结构的有效性,表2给出了本文所设计的QVCO与先前报道的QVCO的对比结果[5,10-12]。通常,可以采用品质因数FOM指标对QVCO的性能进行综合评估,本文采用式(9)所示的FOM表达式。由比较可见,本文所提出并实现的QVCO取得了最低的相位噪声以及较优的FOM性能。

式中,PN为相位噪声,fosc为中心振荡频率,Δf为偏移频率,PVCO为VCO所消耗的功耗。

表1 振幅和相位误差测试结果与仿真结果总结

表2 本文所设计的QVCO与先前报道的QVCO的比较结果

本文基于标准的0.18μm CMOS工艺,提出并实现了一种新颖的SIC-QVCO电路结构。所提出的QVCO采用一种改进的SIC方法,该改进方法具有较低的功耗以及较优的相位噪声等优点。在1 MHz频偏频率下,所提出的SIC-QVCO取得了-119.7 dBc/Hz的低相位噪声,比先前报道的QVCO的相位噪声更低,综合性能较优。可见,本文所提出的SIC方法非常适合用于高性能QVCO的设计当中。

参考文献:

[1]VIGILANTE M,REYNAERT P.Analysis and Design of an E-Band Transformer-Coupled Low-Noise Quadrature VCO in 28-nm CMOS[J].IEEE Trans on Microwave Theory and Techniques,2016,64(4):1122-1132.

[2]RYU H,HA K W,BAEK D.Low-Power Quadrature Voltage-Controlled Oscillator Using Current-Reuse and Transformer-Based Armstrong Topologies[J].Electronics Letters,2016,52(6):462-464.

[3]白杨,张万荣,江之韵,等.一种低抖动电荷泵锁相环的设计[J].电子器件,2015,38(3):516-520.

[4]HA K W,RYU H,PARK J,et al.Transformer-Based Current-Reuse Armstrong and Armstrong-Colpitts VCOs[J].IEEE Trans on Circuits and Systems II:Express Briefs,2014,61(9):676-680.

[5]CHANG H Y,CHIU Y T.K-Band CMOS Differential and Quadrature Voltage-Controlled Oscillators for Low Phase-Noise and Low-Power Applications[J].IEEE Trans on Microwave Theory and Techniques,2012,60(1):46-59.

[6]MAHALINGAM N,MA K,YEO K S,et al.K-Band High-PAE Wide-Tuning-Range VCO Using Triple-CoupledLCTanks[J].IEEE Trans on Circuits and Systems II:Express Briefs,2013,60(11):736-740.

[7]WU J W,WU H H,CHEN C C.A Back-Gate Coupling Quadrature Voltage-Control Oscillator Embedded with Self Body-Bias Schema[J].IEEE Microwave and Wireless Components Letters,2013,23(3):146-148.

[8]LEE S Y,CHEN C Y.Analysis and Design of a Wide-Tuning-Range VCO with Quadrature Outputs[J].IEEE Trans on Circuits and Systems II:Express Briefs,2008,55(12):1209-1213.

[9]CHOI H C,SHIN S B,LEE S G.A Low-Phase Noise LC-QVCO in CMOS Technology[J].IEEE Microwave and Wireless Components Letters,2004,14(11):540-542.

[10]YANG C L,CHIANG Y C.Low Phase-Noise and Low-Power CMOS VCO Constructed in Current-Reused Configuration[J].IEEE Microwave and Wireless Components Letters,2008,18(2):136-138.

[11]YU X,EL-GOUHARY A,NEIHART N M.A Transformer-Based Dual-Coupled Triple-Mode CMOS LC-VCO[J].IEEE Trans on Microwave Theory and Techniques,2014,62(9):2059-2070.

[12]WANG T P,YAN Y M.A Low-Voltage Low-Power Wide-Tuning-Range Hybrid Class-AB/Class-B VCO with Robust Start-up and High-Performance FOMT[J].IEEE Trans on Microwave Theory and Techniques,2014,62(3):521-531.

An Ultra-Low-Phase Noise Quadrature Voltage-Controlled Oscillator Based on Self-Injection-Coupled Technique

QI Yuhua,HE Rulong

(School of Electronic Engineering,Naval University of Engineering,Wuhan430033,China)

Abstract:An improved coupled method for multiphase oscillator is proposed and demonstrated in a standard 0.18μm CMOS technology.A self-injection-coupling(SIC)technique is used to couple two currentreused differential voltage-controlled oscillators(VCOs).Compared with the conventional parallel-coupled quadrature VCO(QVCO),the proposed QVCO using the SIC technique presents low phase noise without increasing dc power consumption.At the oscillating frequency of 16.41 GHz,the proposed SIC-QVCO shows a low phase noise of-119.7 dBc/Hz at 1-MHz offset frequency and a tuning range of 1.66 GHz.The dc supply voltage and current consumption are 1.8 V and 5.28 m A respectively.The chip size of the proposed SIC-QVCO is 0.3 mm×0.9 mm.

Key words:phase noise;self-injection-coupling;quadrature voltage-controlled oscillator;amplitude error;phase error

中图分类号:TN432

文献标志码:A

文章编号:1672-2337(2017)02-0198-05

DOI:10.3969/j.issn.1672-2337.2017.02.015

收稿日期:2016-10-05;

修回日期:2016-12-21

作者简介:

戚玉华男,1977年12月出生于湖北石首,海军工程大学电子工程学院讲师,硕士,主要从事信息通信技术以及射频集成电路设计方面的研究。

E-mail:yuhua_qi1977@163.com