0 引言

随着现代电子技术的快速发展,日益复杂的电磁环境和灵巧的干扰样式对雷达性能的发挥形成严重的限制,雷达抗干扰技术成为现代雷达领域的重要课题,其中自适应天线旁瓣相消技术已成为现代雷达系统消除旁瓣干扰最经济、最有效的措施[1]。实际应用中,通道间信号延迟、幅度和相位不一致特性会显著降低旁瓣相消系统性能。进行通道均衡、对辅助通道添加延迟节都可以有效消除通道特性非理想带来的影响,提高对消性能。其中基于延迟节的自适应旁瓣相消算法具有简单、易于实现等优点。

自适应旁瓣相消算法的实现通常利用开环算法形式。一般来说,开环算法仅利用有限快拍或样本点直接获得最优权值,收敛速度快,能够满足雷达信号实时处理要求[2]。但其运算量较大,需要强大的硬件平台支撑。目前自适应旁瓣相消系统的传统方案是采用基于DSP+FPGA相结合的硬件平台实现,利用DSP的高精度浮点运算能力进行最优权值计算,利用FPGA进行相消计算和时序控制等[3]。这种方案的优点是运算效率和精度高,缺点是软件和硬件耦合紧密、程序移植性差、系统较为复杂。近年来,通用计算机性能的不断提高以及多核技术的快速发展,可为软件化雷达信号处理的实现提供硬件支撑[4-6]。这种基于通用计算机平台的信号处理方法,以软件处理的方式完成信号的实时处理,实现了软件应用程序和底层硬件的解耦,具有标准化、模块化和数字化技术特点,程序的开放性、可移植性大大增加[7-8]。

本文针对某地面情报雷达有源旁瓣干扰抑制需求,提出了基于最大相关性准则的样本选择算法应对多种复杂干扰。构建基于通用计算机平台的自适应旁瓣相消系统,并对基于延迟节的自适应旁瓣相消算法在多核CPU上进行了试验,基于实测数据的试验结果验证了系统的实时性和有效性,满足实际工程应用需求。

1 自适应旁瓣相消算法原理

自适应旁瓣相消的基本原理是通过设置一个辅助天线阵列,利用辅助天线与主天线所接收干扰信号的相关性,对辅助天线信号进行自适应加权求和,结果与主天线信号对消使得输出的干扰信号差值最小,从而实现雷达系统抗多种干扰的功能。

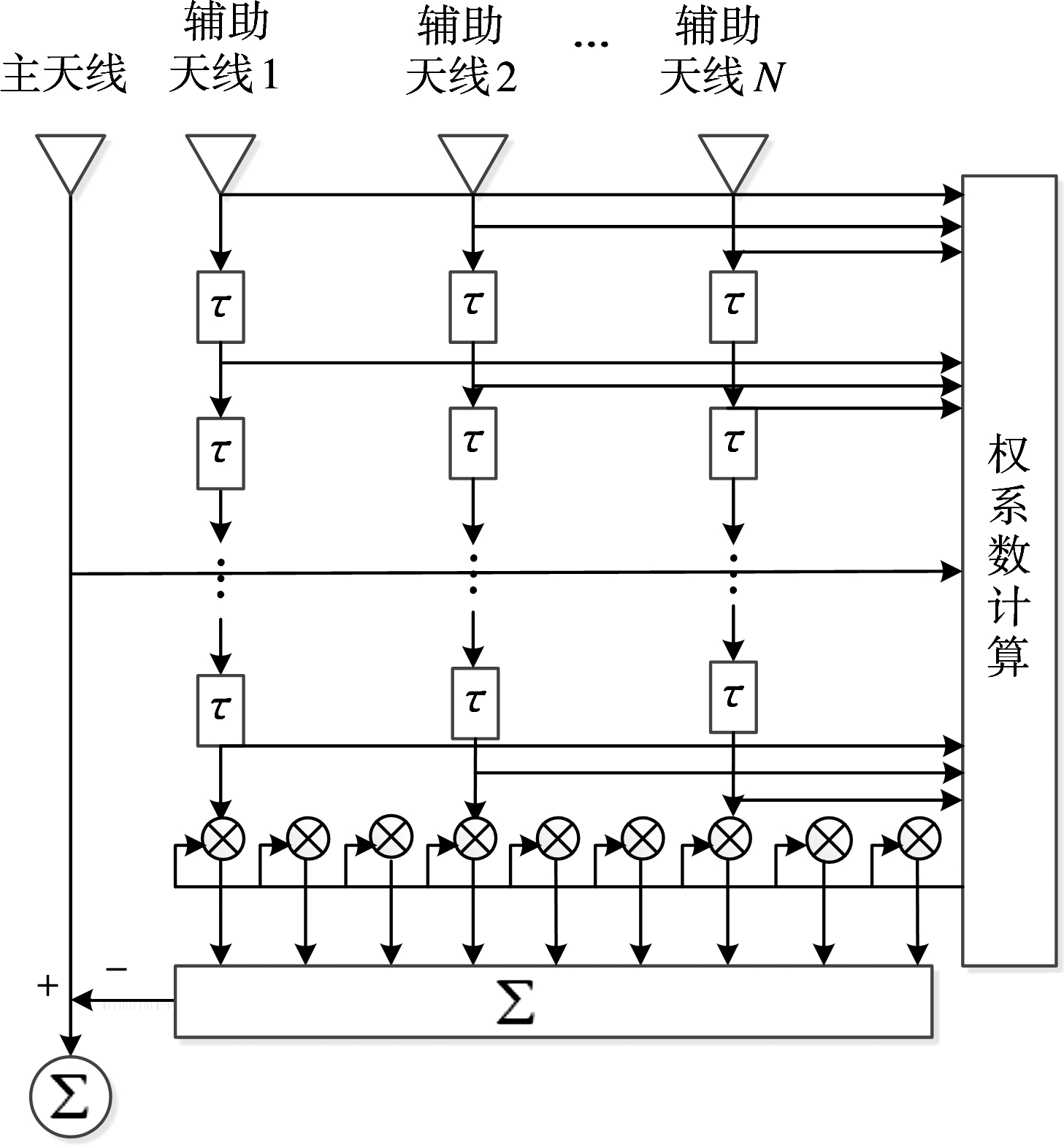

工程应用中,为消除多径影响,并在窄带和宽带条件下,对付各个通道间的不一致性,通常采用对辅助天线增加延迟节的方式,即将辅助天线样本分别延迟若干个距离单元,同时选取合适的样本数据进行自适应权值的估计和相消运算。其原理框图如图1所示。

图1 基于延迟节的自适应旁瓣相消原理框图

每个辅助通道各增加了L个延迟节,将增加延迟节后辅助通道与原有辅助通道合并,得到新的M个辅助通道,每个辅助通道各选取N个数据构成了一个M×N维的空时数据矩阵Xn,即

由空时数据矩阵Xn构成的协方差矩阵R为

主通道样本数据Yn与空时数据矩阵Xn的互相关矢量P为

最优权值W由熟知的维纳-霍夫方程求得:

主通道对消输出信号zn:

式中,xn表示辅助通道信号,yn表示主通道信号,H表示共轭转置运算,∗表示共轭运算。

干扰样本的选取应避免地杂波、噪声和真实目标的影响,传统自适应旁瓣相消样本选择在远区或休止期,但是复合干扰里密集假目标、欺骗式干扰使得该样本选择方法失效。为了充分对消干扰信号,提出了基于最大相关性准则的样本选择算法,准确选择样本并求权,可有效抑制多种干扰,这一方法需要更大的运算量。

常用干扰对消比(ICR)来衡量自适应旁瓣相消系统的性能,定义为干扰输入功率与输出干扰功率之比,即

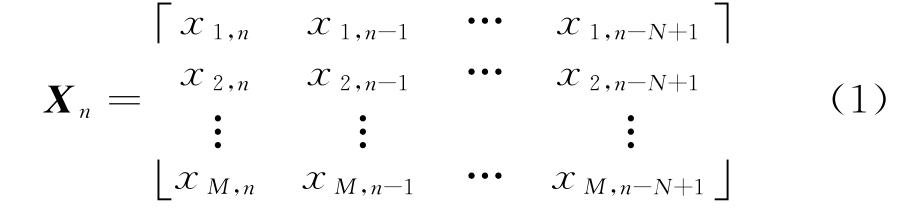

图2给出了某实测数据下平均对消比与全方位最佳对消比随延迟节个数的变化关系。总体来看,加延迟节的方法可以提高对消比,改善旁瓣相消的性能,但对消性能不会随着延迟节个数的增加一直增长下去。一般来说,当延迟节个数增大至某一数值(本数据下为15)时,对消比达到最大,旁瓣相消系统的对消性能达到最优,继续增加延迟节个数,只会降低对消性能。相对窄带下的干扰对消,宽带下的干扰对消需要更多的延迟节个数,这相当于增加辅助通道数,会大大提高运算量。

2 工程实现方法

对于地面情报雷达应用来说,体积、功耗、环境要求不苛刻,信号处理硬件平台可以采用可编程、可重构、软件统一架构且易于维护的通用高性能计算机平台构建。通用计算机平台具有强大的计算能力和大容量高速内存,同时具有PCIE、万兆以太网等多种高速数据接口,能够满足雷达信号处理对运算量、存储量及数据吞吐量的要求。

图2 不同延迟节个数条件下对消比

2.1 基于通用计算机的硬件平台架构

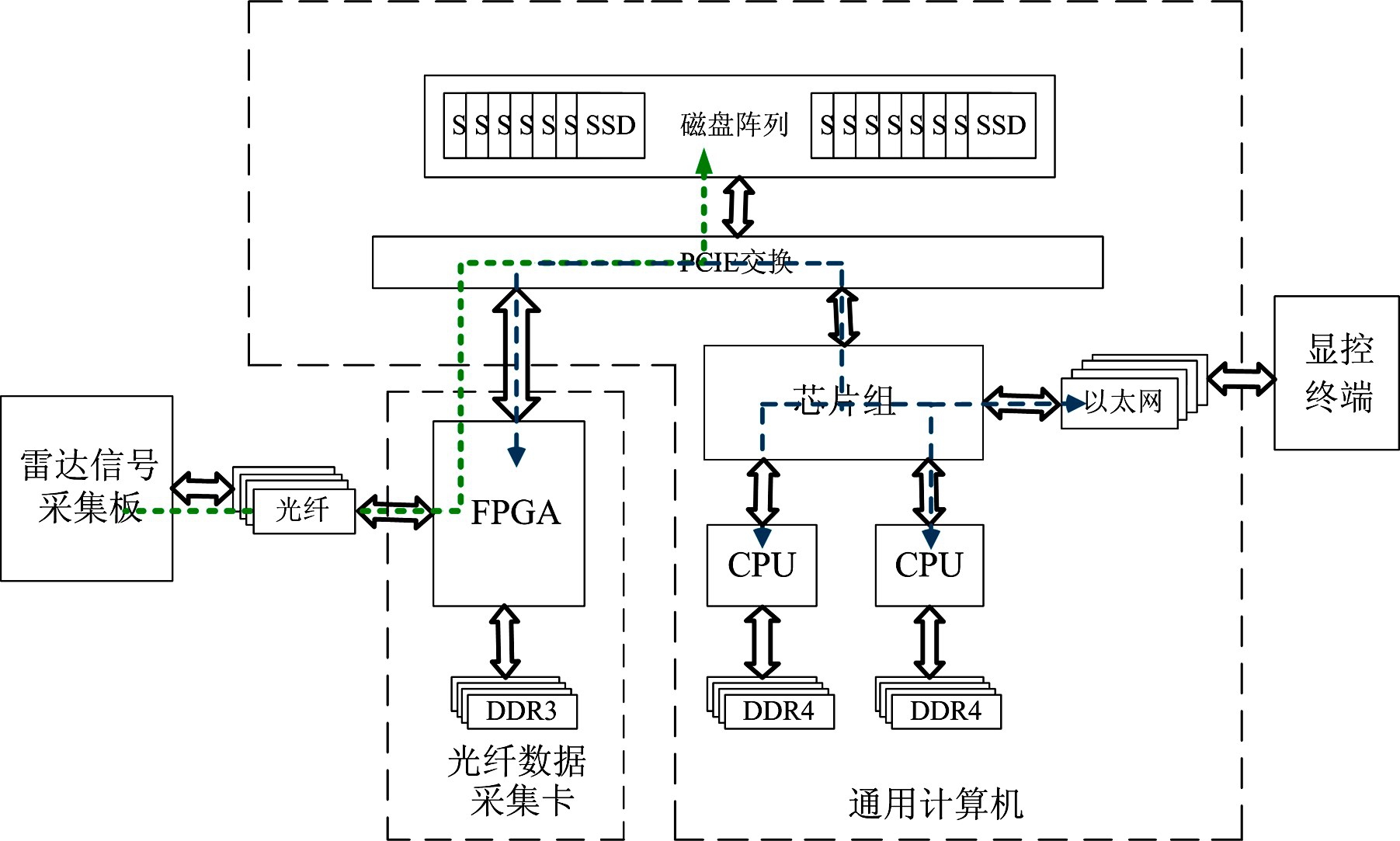

软件化雷达信号处理硬件平台由通用计算机和光纤数据采集卡构成,如图3所示。通用计算机上CPU为2颗Intel Xeon E2640@2.6 GHz处理器,每颗CPU浮点运算能力达到每秒4 000亿次以上,是TS201型DSP的100多倍,能够完成大规模雷达信号处理算法;内存容量为64 GB DDR4,可为原始数据和中间计算结果的缓存提供存储空间,便于实现精细化的信号处理。

图3 软件化雷达信号处理硬件平台框图

为保证数据从雷达信号采集板到通用计算机之间的实时、高速、可靠传输,设计了基于PCIE总线的光纤数据采集卡作为数据传输通道。PCIE总线具有良好的系统构架和传输性能,可为通用计算机与外部高速数据交换提供可靠通路。光纤数据采集卡上的FPGA完成光纤数据的接收,然后将数据经PCIE总线通过高速DMA传输方式传入通用计算机内存;采集卡上的2 GB容量的DDR3 SDRAM存储器,可用于实时数据的高速缓存。

通用计算机作为处理中心,运行基于多核CPU的信号处理软件,完成雷达信号处理。利用CPU读取通用计算机内存中的数据,实现信号处理算法,并将处理得到的目标点迹等信息在本机直接处理、显示,或者通过以太网口送至雷达显控终端,由数据处理软件进行数据处理并显示相关结果。进入计算机内存的数据经过数据重排、快速索引、格式转换后,也可以直接存储到磁盘阵列中,实现数据记录存储功能。

采用通用计算机进行信号处理设计具有以下几方面的优点:

1)基于通用计算机平台,降低了硬件成本,缩小了系统规模,方便硬件采购,提升了系统的可靠性和稳定性。

2)采用通用的高级语言(C/C++)进行软件开发,程序的扩展性、可移植性大大增加,开发周期短,同时纯软件的信号处理相比于传统DSP+FPGA的方式具有较强的灵活性。

3)有利于实现信号处理与数据处理一体化设计。传统的雷达信号处理与数据处理是分开设计的,存在较大缺陷,数据处理时丢失了回波信号的许多信息,如目标速度、加速度、幅度变化规律、目标所处环境信息、目标采用的滤波器种类等。将二者进行一体化设计后可以极大提高数据处理能力,改善雷达P显画面质量。

2.2 软件实现步骤

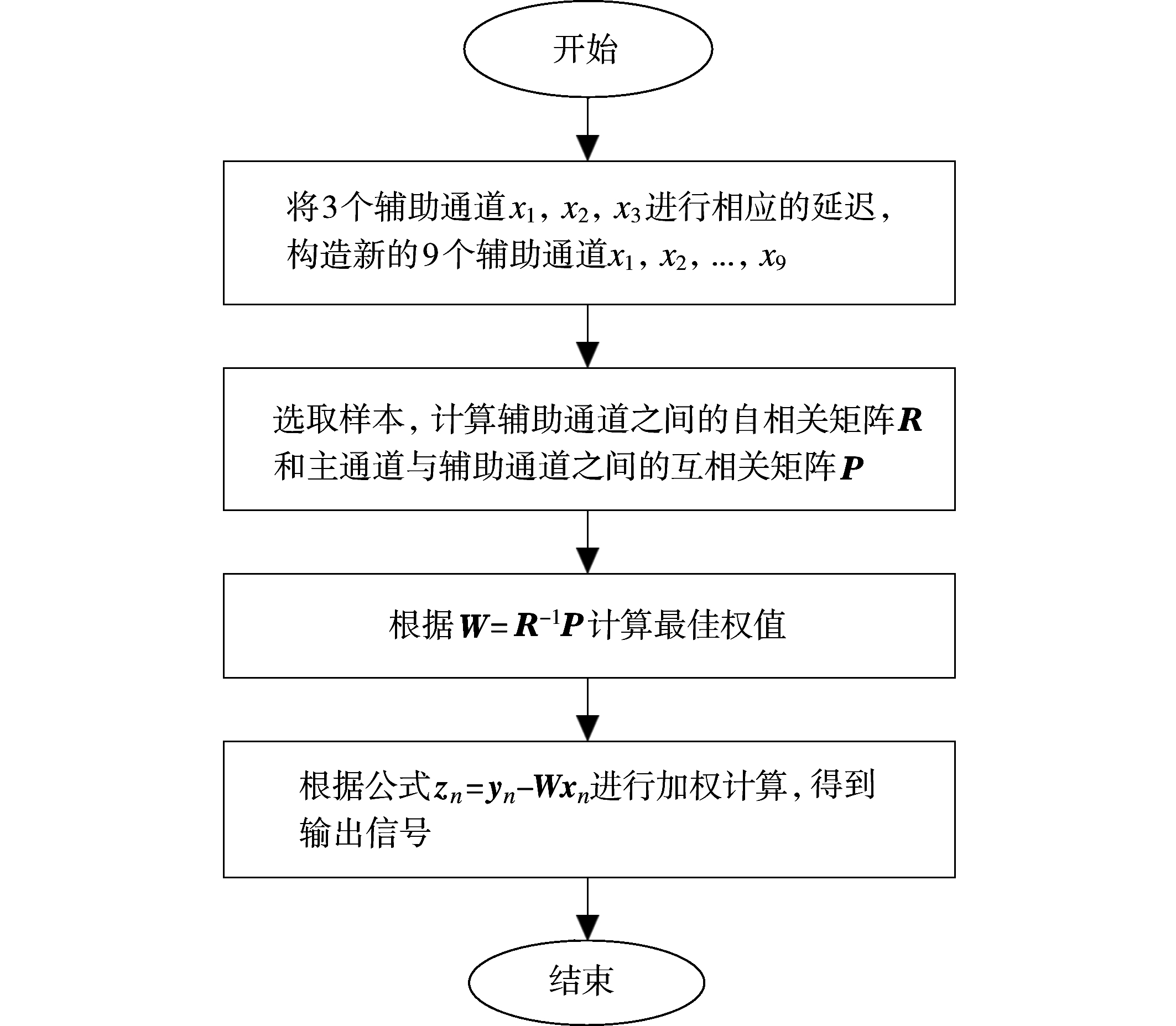

自适应旁瓣相消系统对处理实时性有严格要求,需要算法具有较强的执行效率。在进行算法设计时通过数据分块技术,使得计算过程变成向量、矩阵的基本运算,从而高效地调用Intel公司开发的科学计算库(MKL)来实现。MKL库函数经过底层指令优化和并行优化,运算效率高。同时,基于库函数开发的算法程序,可以适应各种体系结构的存储结构,实现程序高效地跨平台移植。软件实现流程图如图4所示。

图4 软件实现流程图

算法的计算过程主要包括复数矩阵求逆和复数矩阵乘法等,主要用到MKL中基础线性代数库(BLAS)和线性代数函数库(LAPACK)。BLAS涉及的是最基本的向量、矩阵运算,使用时不必过多考虑与计算机体系结构相关的性能优化问题;LAPACK主要用来求解工程计算中最常见的数值线性代数计算问题,其采用了分块矩阵操作技术,可以适应各种体系结构的存储结构,并提供一种可移植的方式,可以在多种不同计算机平台上获得高效率。

自适应旁瓣相消包括如下处理过程:

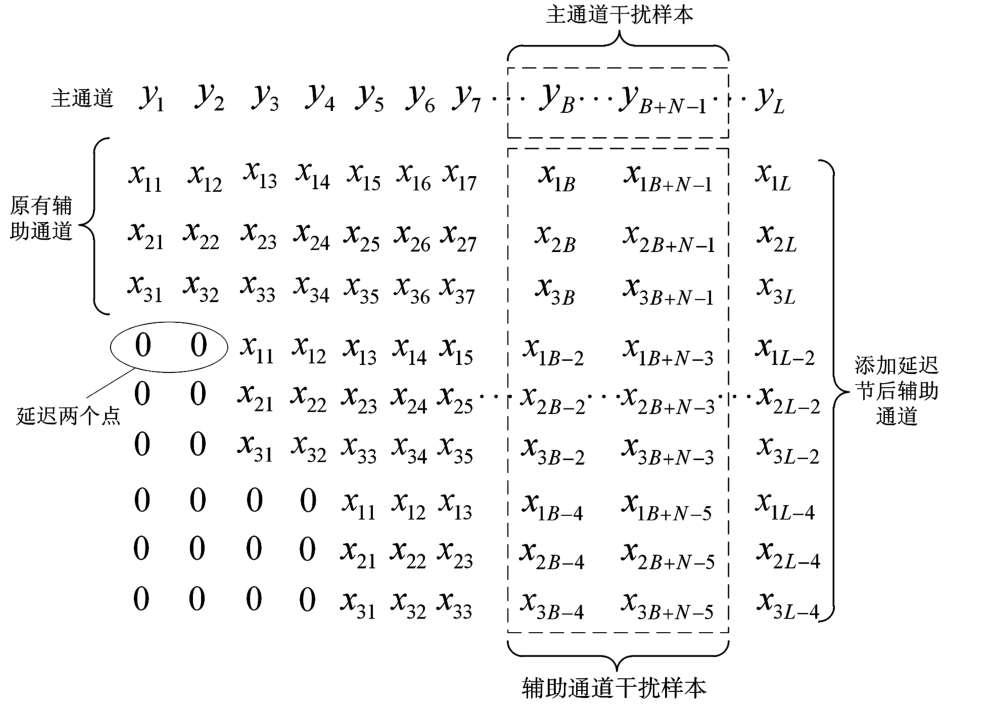

1)选取干扰样本:如图5所示,以3个辅助通道为例,首先进行通道数据的延迟,延迟点为2,延迟节数为3,最终形成9个新的辅助通道数据,根据主辅通道的相关性选取干扰样本。此过程涉及大量将原有辅助通道数据拷贝的操作,使用内存拷贝函数memcpy实现。

2)相关矩阵求解:计算辅助通道样本间的自相关矩阵和主、辅通道间的互相关矩阵其实质就是矩阵(向量)间相乘运算,选出的主、辅通道干扰样本分别以一维数组存储,调用BLAS中cblas_cgemm函数实现。

3)求取自适应权值:通过维纳-霍夫方程求最优权值,首先调用LAPACK中LAPACKE_cgetrf函数实现自相关矩阵的LU分解,再调用LAPACKE_cgetri函数实现对自相关矩阵的求逆,最后调用矩阵相乘函数cblas_cgemm将求逆后的矩阵与互相关矩阵进行矩阵相乘求出最优权值。

4)相消处理:首先调用矩阵相乘函数cblas_cgemm实现最优权值和辅助通道数据的矩阵相乘运算,然后调用MKL中的向量减函数vcSub进行相消处理。

图5 添加延迟节、选取干扰样本过程示意图

2.3 各功能模块运行时间分析

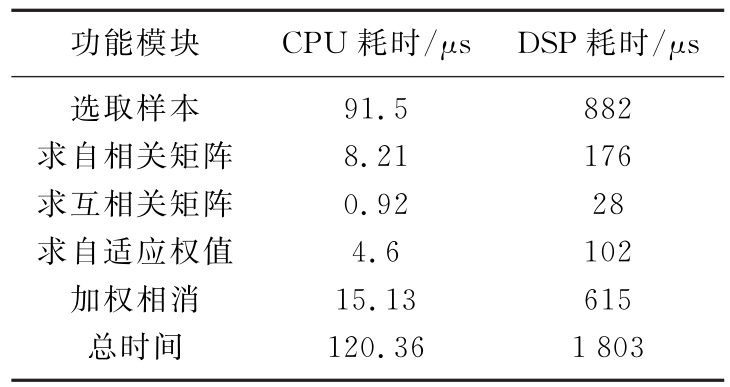

基于某地面情报雷达实测数据,对算法各功能模块运行时间进行试验分析。分别对各个处理模块在多核CPU上进行10 000次循环,详细测算函数执行时间。CPU程序使用Intel MKL11.3科学计算库并用Intel C++Compiler XE15.0编译器进行编译。程序开发平台为64位的Visual Studio 2013集成开发环境。

为进行对比,将相同算法在1片TS201型DSP上实现,CPU和DSP的运算模型和运算参数相同。基于DSP的算法实现中利用C与汇编混合编程,尽量使用汇编语言实现基本函数算法,以提升执行效率。得出单次平均运行时间如表1所示。

表1 自适应旁瓣相消系统实际耗时表

基于多核CPU的自适应旁瓣相消总的处理时间为120.36μs,占比约为常规地面情报雷达脉冲重复周期的6.02%,处理效率约为1片TS201的15倍,满足实时处理要求。进一步在通用计算机平台下实现了包括脉压、动目标检测、恒虚警、数据处理和显示的全部处理,成本是传统DSP平台的1/3,但体积和功耗大约是传统DSP平台的2倍。

3 实测数据验证

通过雷达外场实测数据进一步仿真分析本文自适应旁瓣相消系统的性能。干扰信号为干扰机发射的压制式噪声干扰,单干扰源,位于雷达224°方位。为了便于更加直观对比分析,将自适应旁瓣相消系统主通道输入的时域数据和自适应旁瓣相消对消输出的主通道时域数据转化为数据格式文件保存,用MATLAB绘图。

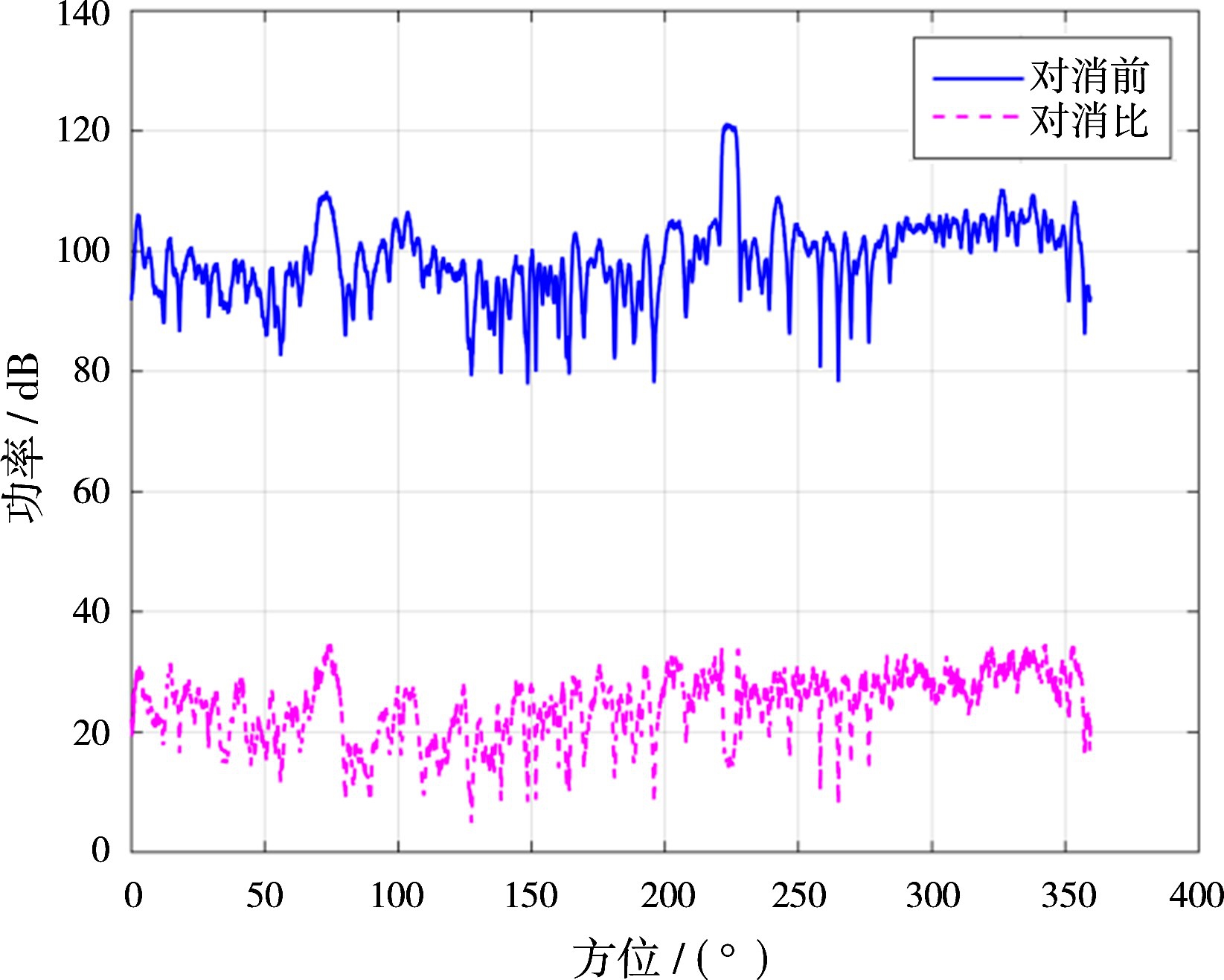

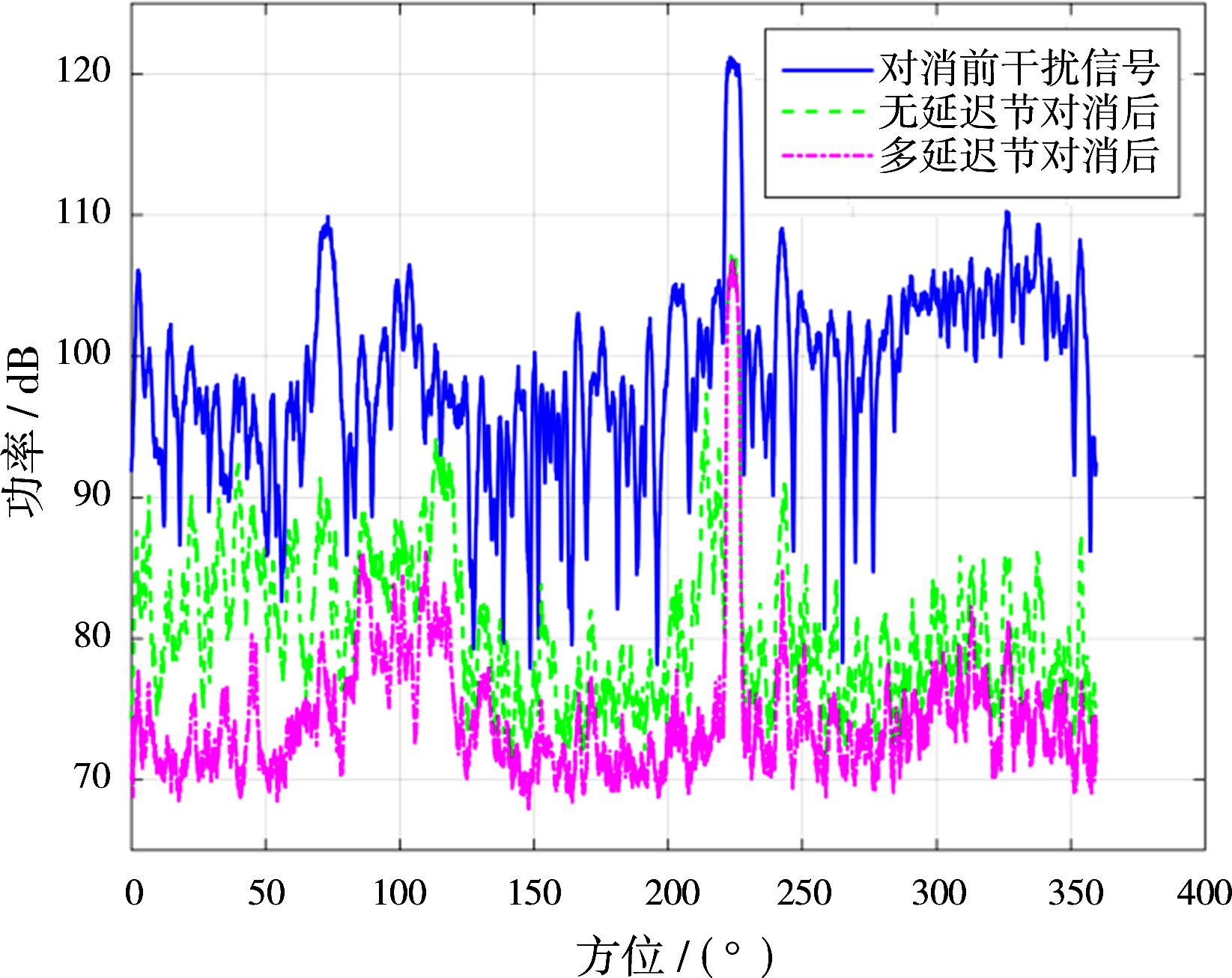

图6给出了某实采数据下对消比随方位的变化关系。从图中可以看出,全向对消比基本在20 dB左右,对消比随输入信号功率的变化而变化,当输入功率增强时,对消比增大,反之,对消比减小。不同方位对消比变化较大,较好的方位获得34 dB的对消比,而较差的方位对消比只有5 dB,主要原因是这些方位上存在较强地物反射体,导致主通道和辅助通道之间的信号相关性严重下降,从而使对消性能变差。图7进一步看出,与不加延迟节的自适应旁瓣相消算法相比,添加延迟节后,干扰剩余功率较低,对消性能更好。

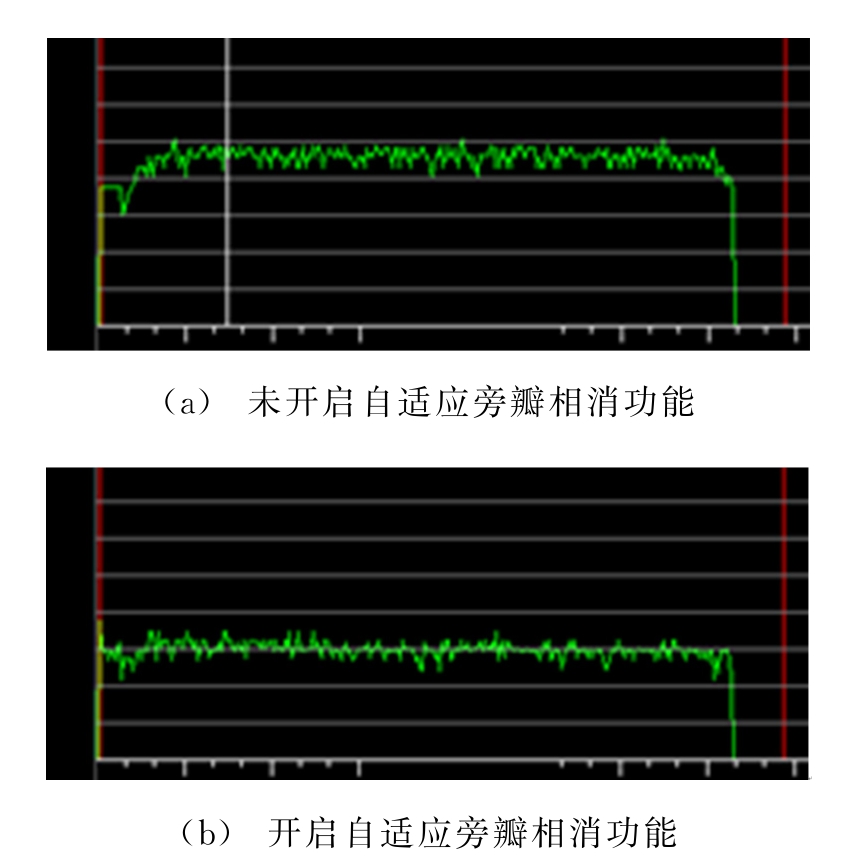

图8(a)为单源压制式干扰时实际雷达终端的画面显示,图8(b)为开启自适应旁瓣相消功能后的实际雷达终端的画面显示。可以看出,加入自适应旁瓣相消功能后干扰受到抑制,噪声背景下降,终端界面上一格代表12 dB,可见噪声背景约下降1.5格,约为18 dB,表明旁瓣相消的对消比为18 d B,达到系统要求。实测数据验证表明,基于延迟节的自适应旁瓣相消算法是有效的。

图6 对消比随方位的变化关系

图7 相消前后信号功率随方位的变化关系

图8 实际雷达终端的画面显示

4 结束语

本文提出了一种基于最大相关准则的自适应旁瓣相消样本选择方法,并构建了基于软件化雷达架构的自适应旁瓣相消系统,采用通用计算机作为处理平台,利用多核CPU软件编程实现整个雷达信号处理和数据处理功能。该系统采用基于延迟节方法应对多径和通道间时延差异,实测数据验证了基于延迟节的自适应旁瓣相消系统性能,表明了所述方法能够有效抑制旁瓣干扰。实际运行时间表明系统具有较快的运算速度,能够满足实时处理要求,具有广阔的工程应用前景。

参考文献:

[1]吴顺君,梅晓春.雷达信号处理和数据处理技术[M].北京:电子工业出版社,2008:272-279.

[2]付启众,关堂新,徐晋.基于最强快拍法的自适应副瓣对消技术[J].雷达科学与技术,2013,11(5):505-510.FU Qizhong,GUAN Tangxin,XU Jin.A Sidelobe Canceller Based on Snapshots with Strong Power[J].Radar Science and Technology,2013,11(5):505-510.(in Chinese)

[3]郑禹,汪萍.基于实测数据的稀布阵雷达副瓣对消研究[J].合肥工业大学学报(自然科学版),2012,35(1):66-69.

[4]陈国良.并行计算[M].北京:高等教育出版社,2011:25-32.

[5]秦华,周沫,察豪,等.软件雷达信号处理的多GPU并行技术[J].西安电子科技大学学报(自然科学版),2013,40(3):145-151.

[6]房骥.基于多核CPU的软件无线电平台研发及应用技术研究[D].北京:北京交通大学,2013.

[7]汤俊,吴洪,魏鲲鹏.“软件化雷达”技术研究[J].雷达学报,2015,4(4):481-489.

[8]孙雪涛.软件化雷达信息实时处理与显示[D].南京:南京信息工程大学,2009.