0 引言

合成孔径雷达(SAR)具有高分辨率、全天候、全天时成像特点,在目标识别、军事侦察、地形测绘等众多领域广泛应用[1-2]。环扫SAR系统可以实现360°方位成像,对重点区域可以实现准实时监视,是直线SAR体制系统的一种补充,应用前景良好。雷达多模式工作可以满足用户多种需求,本文研究环扫SAR多模式工作系统中距离向脉冲压缩的FPGA实现。

根据软件无线电的基本思想,中频采样可以实现更高的灵活性和更强的开放性,故本雷达系统采用中频数字化采样方案。对9.4~9.6 GHz的X波段回波信号通过超外差式接收体制进行2级降频至60 MHz中频再转换为数字信号处理[3]。

在环扫SAR系统体制下,数字信号处理板需要在天线转台的每一个转动角度的时间内完成相应距离向的解调,同时也有大量的数据需要进行实时处理,所以该系统使用运算量更小,满足实时要求的频域脉冲压缩处理方案。高性能的FPGA(Field Programmable Gate Array)芯片可以方便地实现脉冲压缩,方案设计中使用Altera公司的Cyclone系列芯片,完成雷达数字接收机距离向的信号处理[4-5]。

1 设计原理

1.1 雷达波形参数设计

雷达系统主要由频率综合器、发射机(功放模块)、转台、天线、接收单元及信号处理器组成,由频综模块产生9.39~9.43 GHz的射频激励信号和本振信号,其中,发射信号送往功率放大器进行功率放大,然后通过发射天线发送到自由空间。接收天线接收来自目标9.39~9.43 GHz回波信号,接收机的脉冲模块将回波信号放大等处理后变频至60 MHz的中频信号,而后在信号处理器进行信号处理。

设计发射波形为4种模式的脉冲体制线性调频,根据用户不同的需求采取不同的模式,达到理想的分辨率和探测距离等要求。

发射波形表达式为

(1)

即脉冲体制内的线性调频信号。式中,f0为载波频率,K为扫频斜率,T为工作周期。根据不同的模式有不同的脉冲宽度Tr。

1.2 匹配滤波理论

脉冲压缩就是在发射的宽脉冲内,采用附加的频率或相位调制,以增加信号的时宽带宽积。当接收时用匹配滤波器进行处理,这样就将宽脉冲压缩到1/B宽度(B为带宽),从而有效地解决了雷达的作用距离和距离分辨率之间的矛盾,可以在不损失雷达威力的前提下提高雷达的距离分辨率。

根据式(1)的发射信号波形,可以得到相应时延的回波模型:

sr(t)=st(t-τ)=

(2)

通过最佳处理理论可以得出对应的匹配函数[7-8]为

(3)

若忽略噪声, 则滤波器输出结果为y(t)=sr(t)*h(t),经过演算可得下式即脉压结果:

(4)

式中,r=τc/2为横坐标距离自变量,而r′=tc/2为目标距离,根据脉压结果表达式可以看出其结果为sinc函数形式,且sinc函数的峰值横坐标为探测目标距离。

1.3 模式参数分析

两个目标处于同一波束范围内但与雷达距离不同,二者能被雷达分辨出来的最小间距称为距离分辨率。雷达系统通过发射大的时宽-带宽积线性调频信号,通过脉冲压缩技术对接收到的回波进行处理,从而实现距离向高分辨。距离分辨率只与发射信号带宽有关,带宽越大,距离分辨率数值越小,分辨率越高。

本雷达发射波形最大扫频带宽B=12 MHz,理想距离分辨率为

(5)

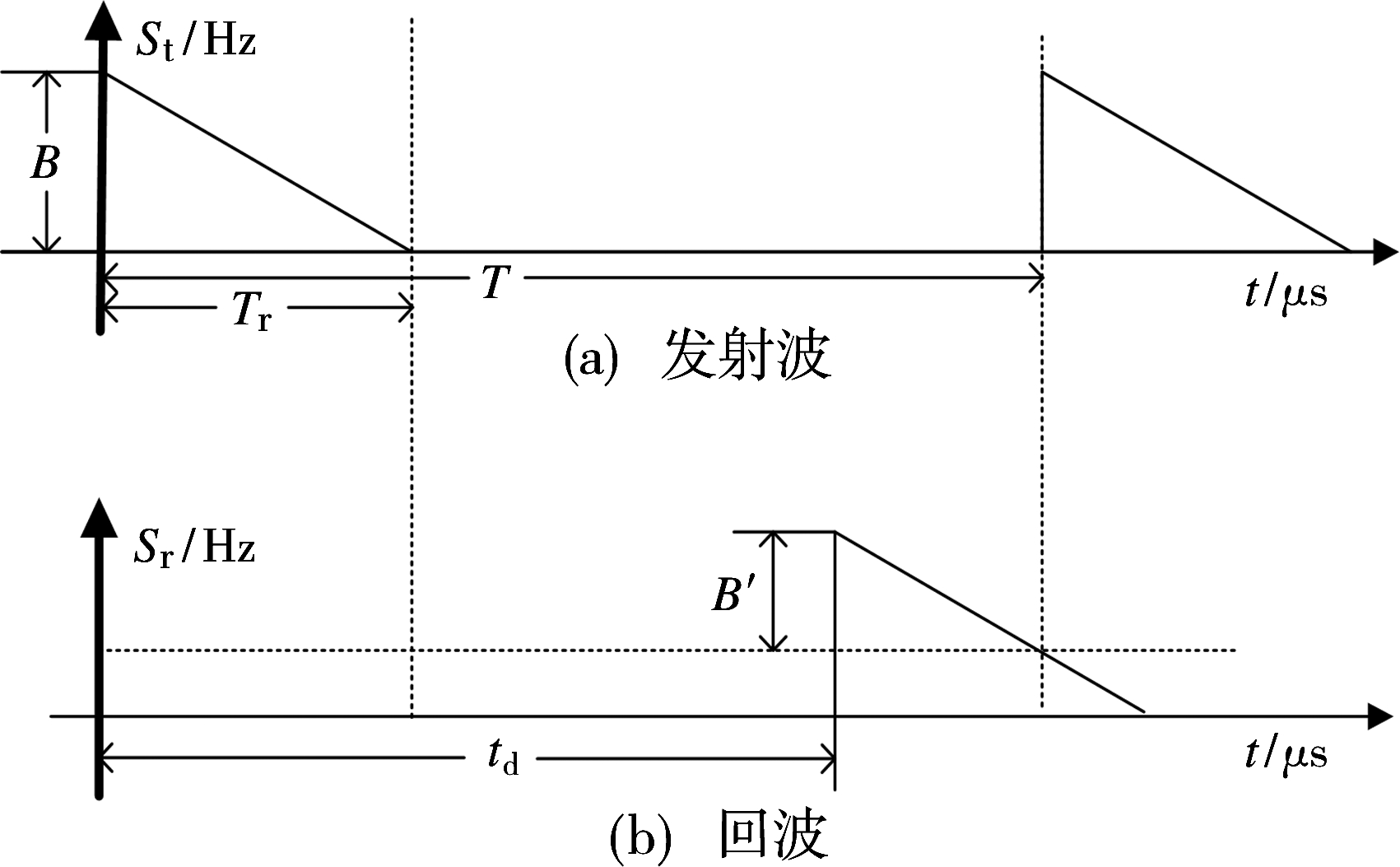

当目标回波延时td,如图1所示有效带宽降为

(6)

式中,Tr为脉冲宽度。

图1 雷达波形

考虑了回波延时的影响后,目标距离分辨率为

(7)

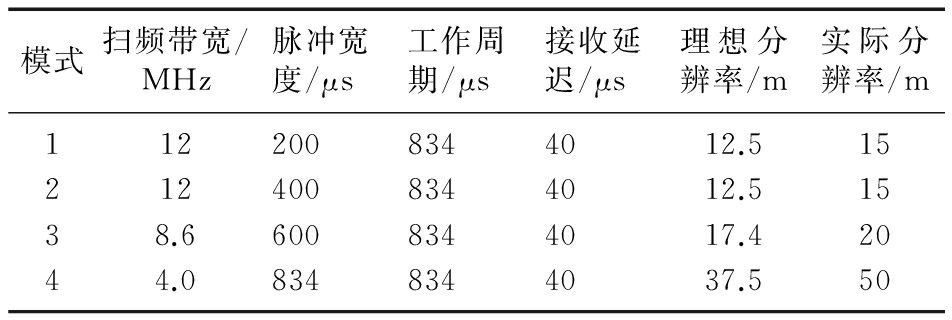

从式(7)可以计算得到雷达在不同的探测距离上有不同的距离分辨率,且距离越远,分辨率越差。表1给出了系统设计的模式参数。

表1 模式参数

2 频域脉冲压缩FPGA实现

2.1 系统结构与MATLAB验证

在FPGA设计实现之前,为了验证硬件电路的可实现性,以及提高开发的效率和正确性,先进行对应MATLAB代码的实现以及仿真。

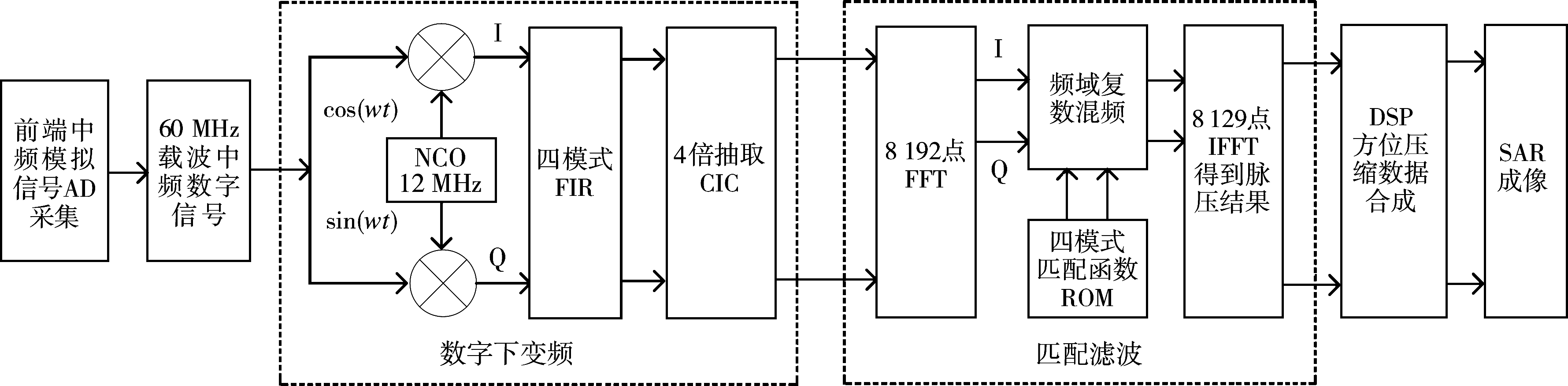

首先介绍设计实现的主要结构,图2为FPGA系统设计框图。虚线框左右两侧为FPGA系统的外围模块,虚线框左侧是来自模拟前端的AD采集模块得到的中频数字信号,虚线框右侧模块则表示将脉压输出结果数据导入DSP中进行方位向压缩,从而实现数据的距离与方位解调,得到SAR的点目标成像。而两个虚线框部分则是FPGA系统算法处理部分,四模式雷达数字接收机的脉冲压缩有两大模块:数字下变频和匹配滤波模块。

图2 FPGA系统模块框图

其中,数字下变频模块包括了正交混频、FIR滤波器、CIC滤波器[6],匹配滤波模块包括了FFT、四模式复数混频、IFFT模块。

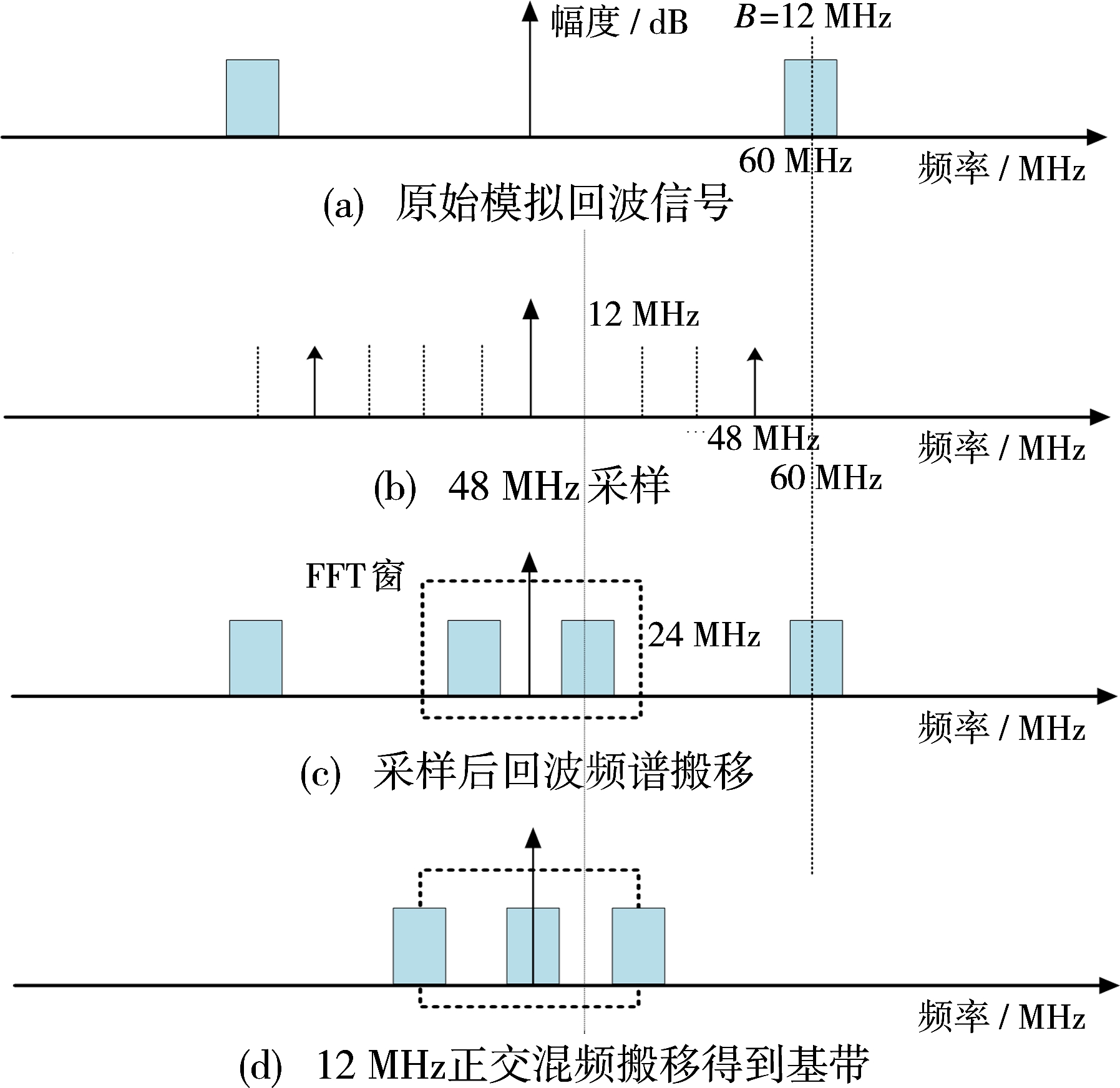

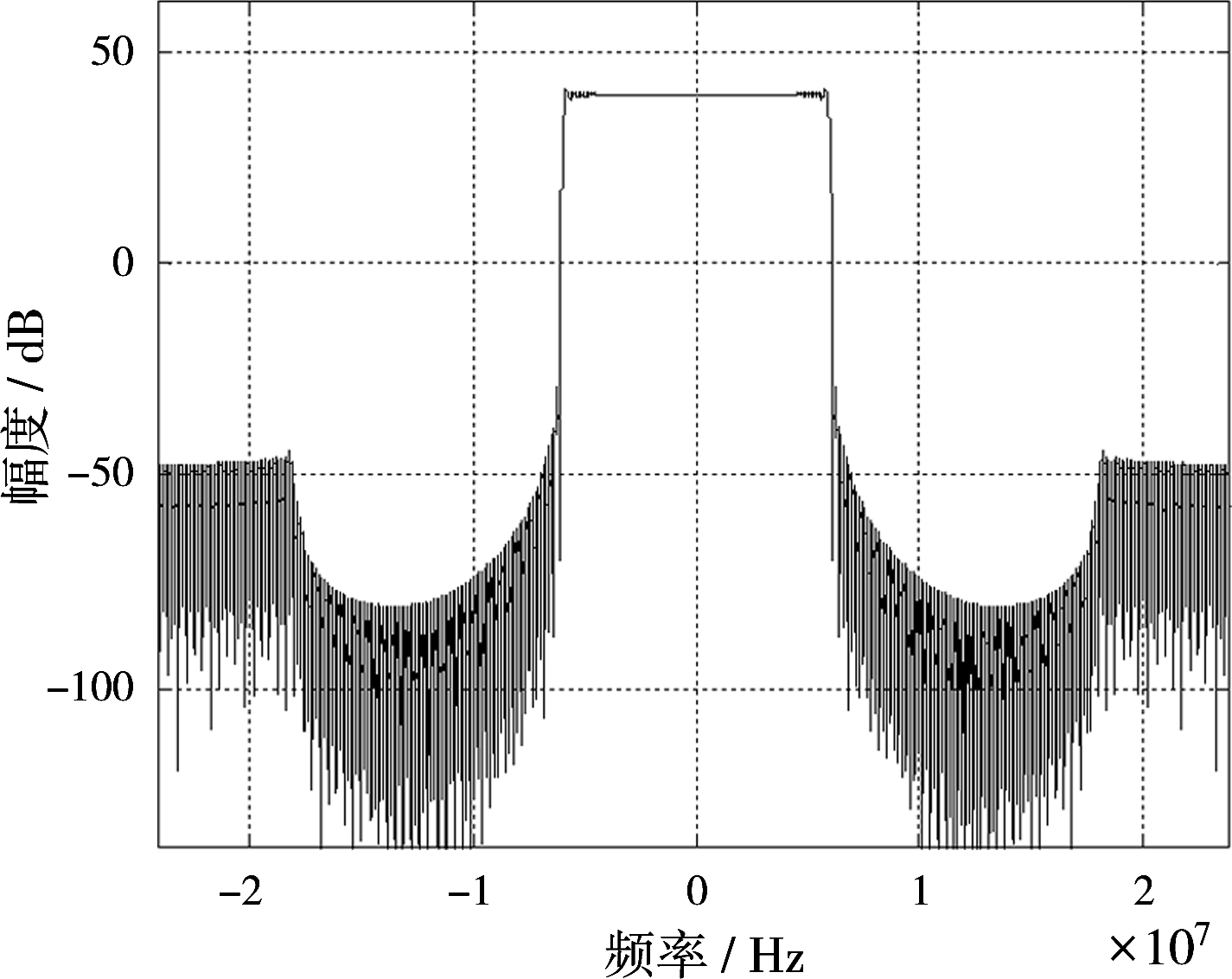

接下来介绍雷达系统的详细工作流程,模拟前端选择了某一种工作模式后,将会给电路板一个模式选择信号控制其工作,然后再根据该信号来控制FPGA内部的滤波器参数以及对应模式的匹配滤波函数。根据模式1的波形参数特性,在模块输入设计了32 768点的回波信号。回波信号为脉冲体制的线性调频信号,带宽为12 MHz,载波频率为60 MHz。由于输入回波过采样,无法进行如此大量数据的频域匹配滤波,于是对其进行下变频处理。设计的信号采样率为48 MHz,对载频为60 MHz的信号进行采样,由于采样对频谱造成的周期延拓,在频谱窗内得到的频谱为6~18 MHz的扫频,以及采样带来其他频带的信号,如图3所示。

经过采样后,再将信号进行基带搬移,采用12 MHz的数字本振,对实信号采样的单路信号,进行正交混频变成I,Q两路,此时再通过一个低通滤波器滤除混频产生的高频分量,得到基带信号并同时消除镜像频率。

图4为MATLAB仿真数字下变频得到的结果,图4(a)为数字下变频前的模拟端回波信号经过48 MHz AD采样后的数字信号频谱,图4(b)为数字下变频后得到的基带信号频谱。

图3 频带搬移示意图

(a)AD采集后回波频谱

(b)基带回波频谱

图4数字下变频前后信号观察

得到基带信号后,为了满足硬件实现的要求,将处理的数据量降低,再进行4倍抽取处理,得到基带的采样率为12 MHz的信号。

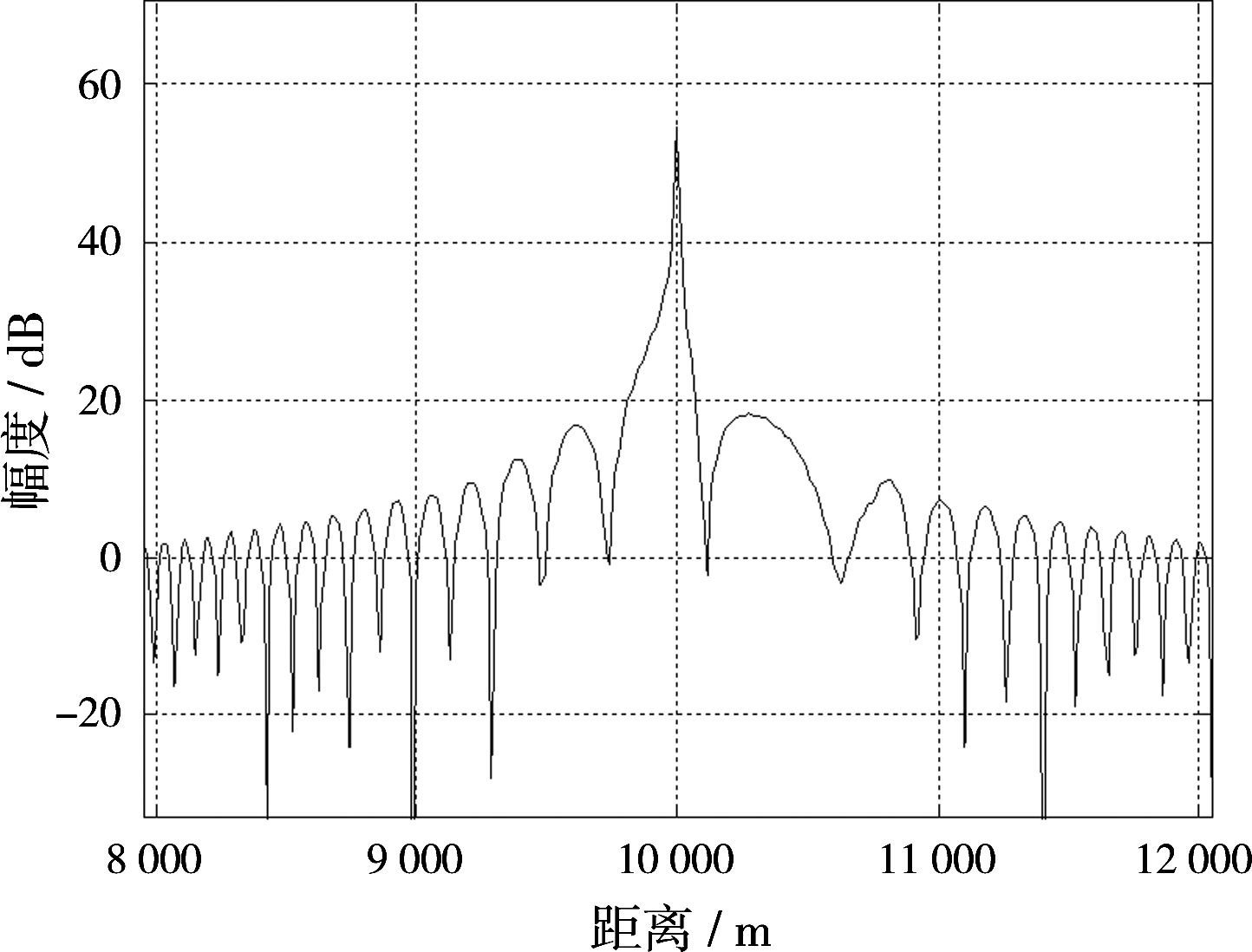

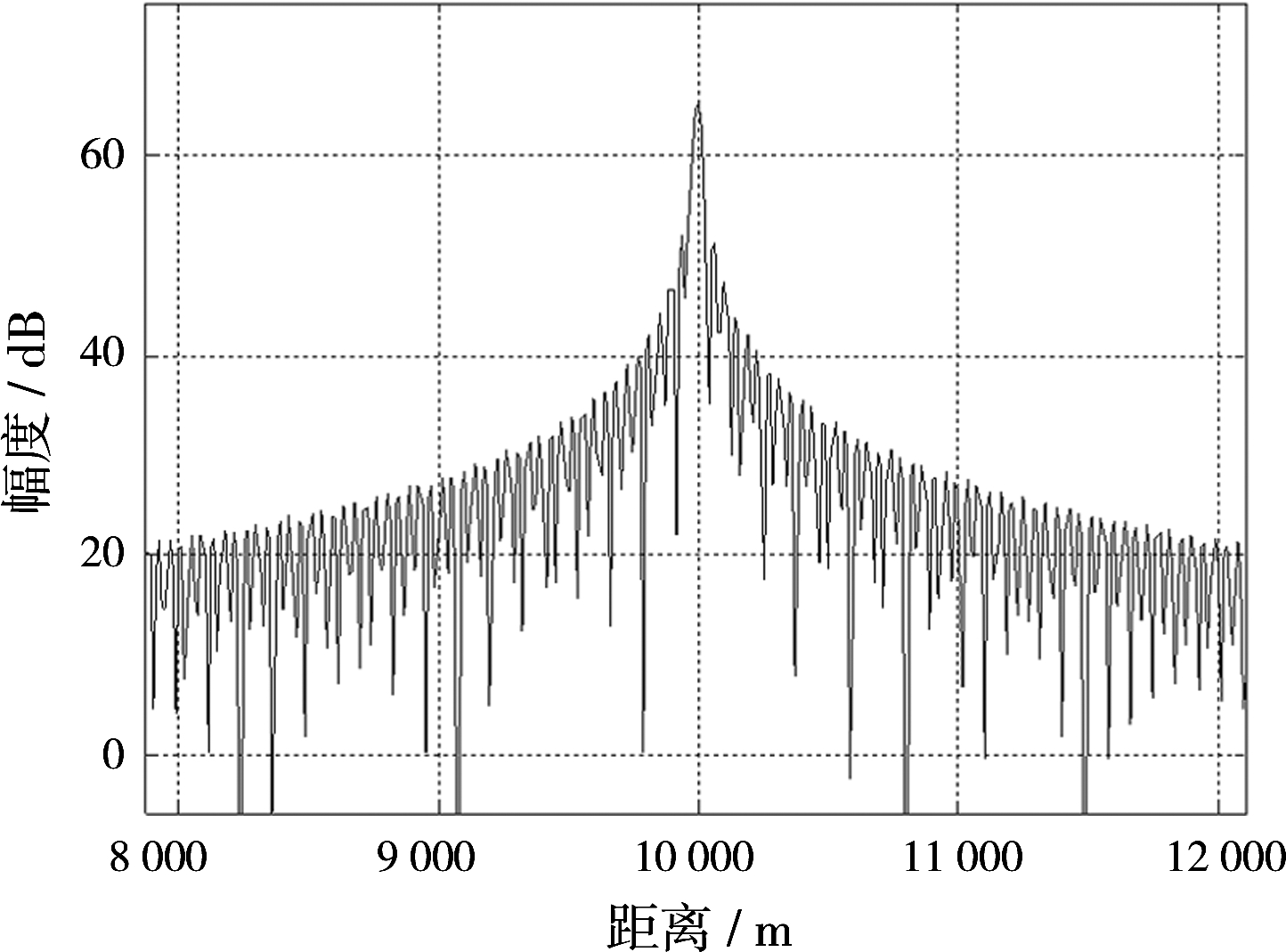

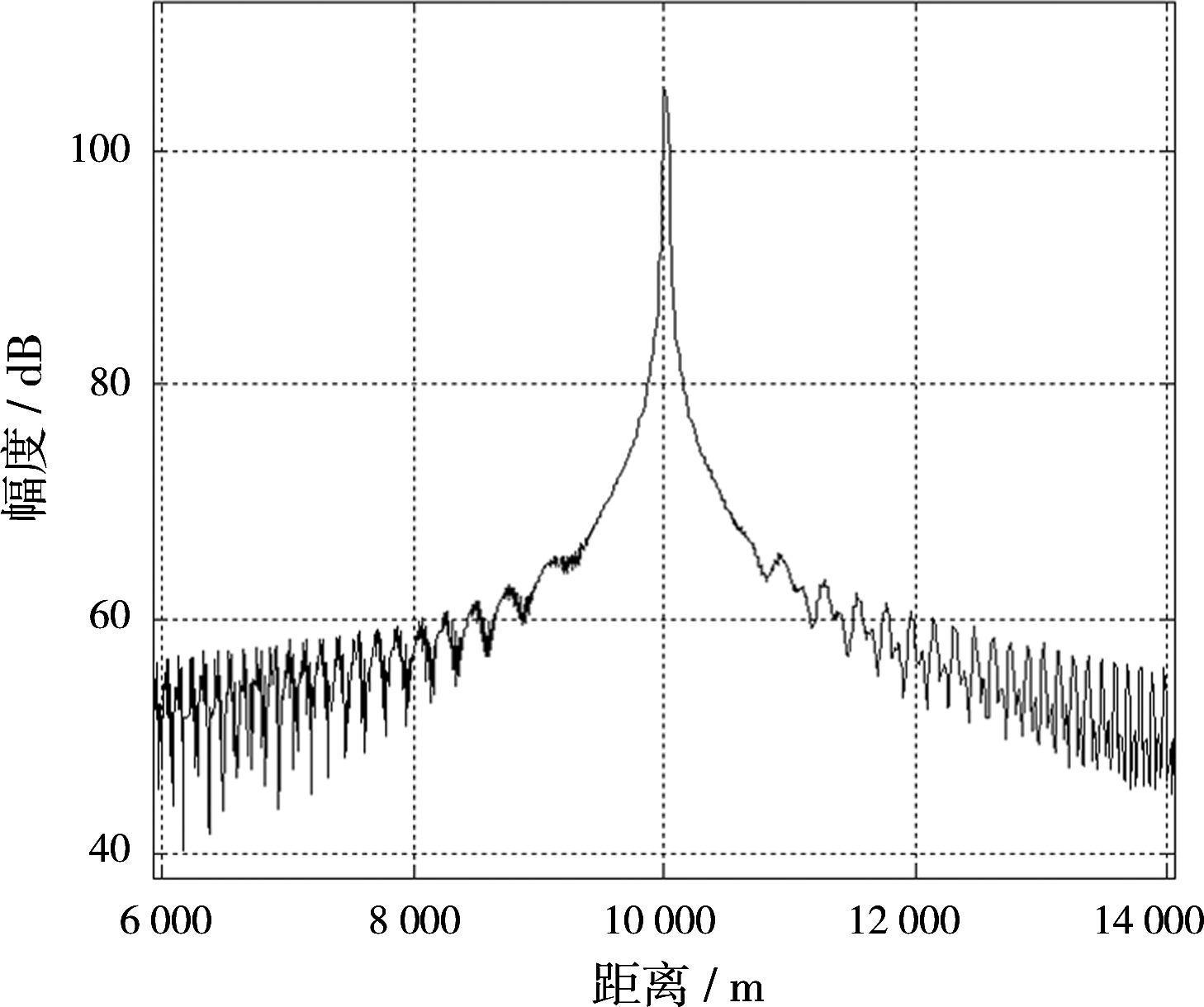

再经过频域方法的匹配滤波处理,先对基带信号进行FFT得到频域信号,匹配函数进行FFT得到其频域信号,再将两者进行频域复数乘法,最后经过IFFT处理得到脉冲压缩结果[7],图5(a)~(d)分别为模式1~4的MATLAB脉压仿真结果。

(a)模式1

(b)模式2

(c)模式3

(d)模式4

图5脉压仿真四模式结果对比

从图5可以看出,模式1和模式2的4 dB主瓣尖锐,模式3和模式4主瓣则依次变宽,表明模式1和模式2分辨率相对模式3和模式4较高;另一方面,由于各模式扫频斜率的不同,造成其旁瓣疏密不同。MATLAB结果验证了系统的正确性,下面进行FPGA模块搭建。

2.2 FPGA框架搭建

在MATLAB仿真验证之后,再进行FPGA硬件编程。FPGA设计相比MATLAB算法验证,还需要考虑硬件电路的其他模块接口以及数据流控制、资源使用等问题。其中,数字下变频包括了模式选择模块、回波模拟模块、NCO本振正交混频模块、FIR滤波器模块、CIC抽取滤波器模块。通过FPGA中的IP核调用以及各模块的连线调试,得到正确的基带脉内扫频信号,并实现4倍降速。

其中,FIR滤波器的作用是滤除正交混频后带来的高频信号,以得到正确的基带频谱[8]。对于不同模式设计了不同参数的滤波器,即图2中的四模

式FIR,FIR滤波器系数通过MATLAB中的FDA Tool生成。

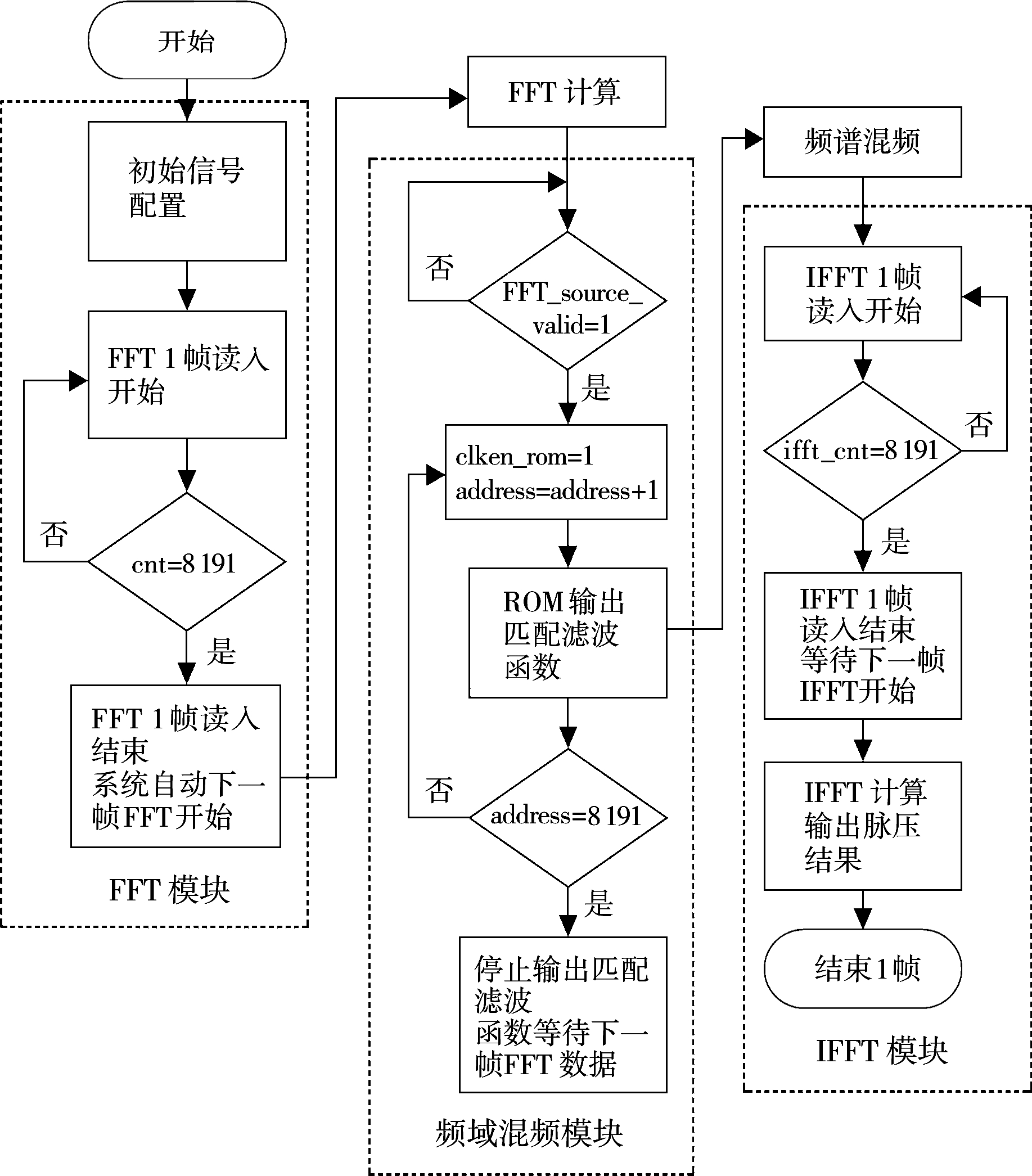

2.3 基带频域数字脉冲压缩

数字脉冲压缩的实现方法可分为时域法和频域法,时域法主要对接收信号作复相关运算,在时域完成匹配滤波。时域法适合处理数据量小的脉冲压缩,对于数据量大、实时性要求高的脉冲压缩处理,频域法更为适合[9-10]。在Quartus平台下,为了完成基带信号的匹配滤波算法,主要运用到的是软件内置的FFT(IFFT)的IP核模块、ROM模块。基带信号流通过FIFO控制读写,将第一帧8 192点数据信号送进FFT模块中。当一帧数据输入结束后,经过一段时间的FFT计算得到FFT结果,即基带回波信号的频谱,再根据模式选择信号选择对应模式匹配函数输出与基带回波信号的频谱进行复数混频。混频结果再输入到最后一个模块,即IFFT模块,IFFT模块输出的结果就是脉冲压缩最终结果。下面给出基带匹配滤波Verilog实现的程序流程图,如图6所示。

图6 基带脉冲压缩Verilog程序流程图

3 FPGA系统仿真与测试

3.1 RTL仿真结果分析

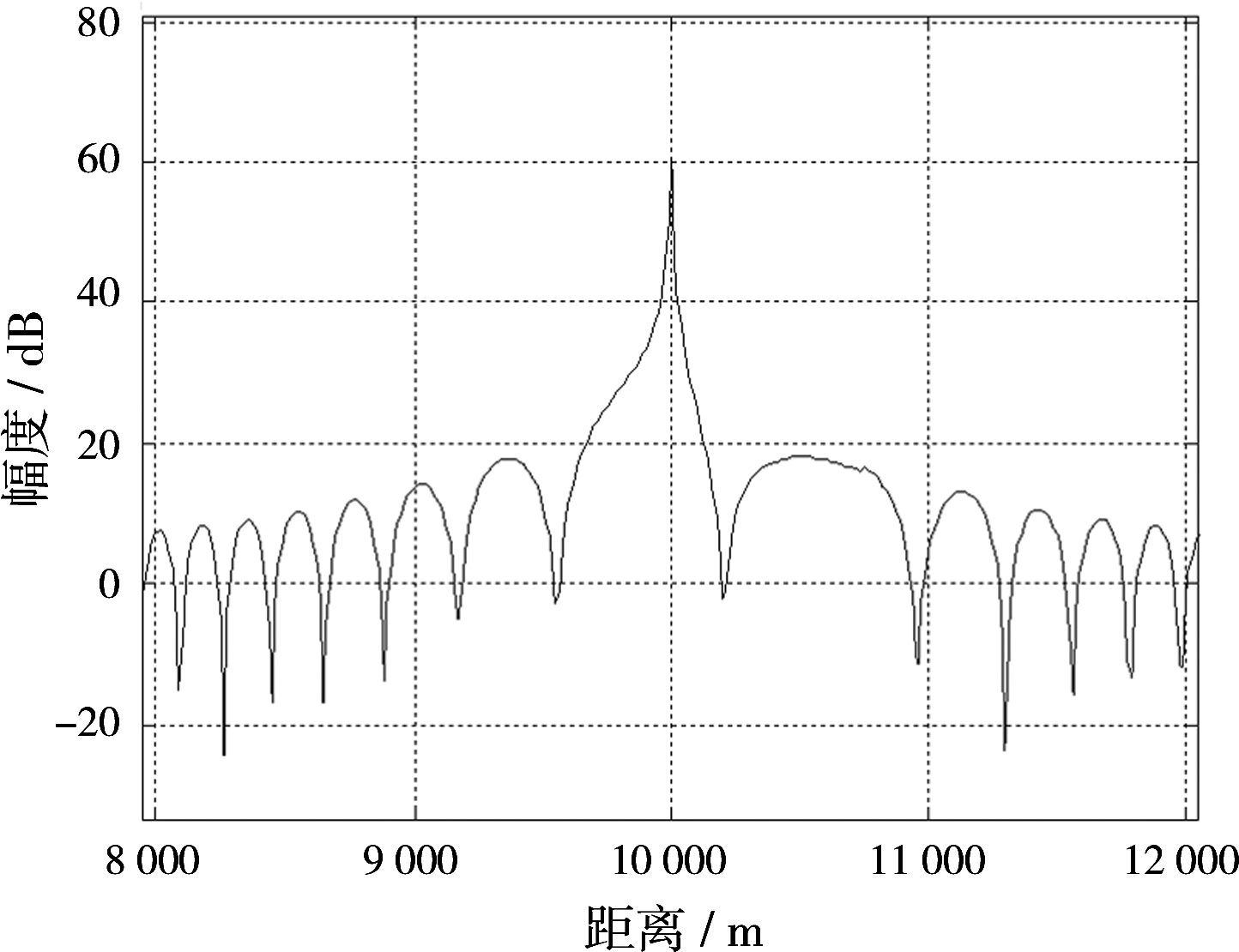

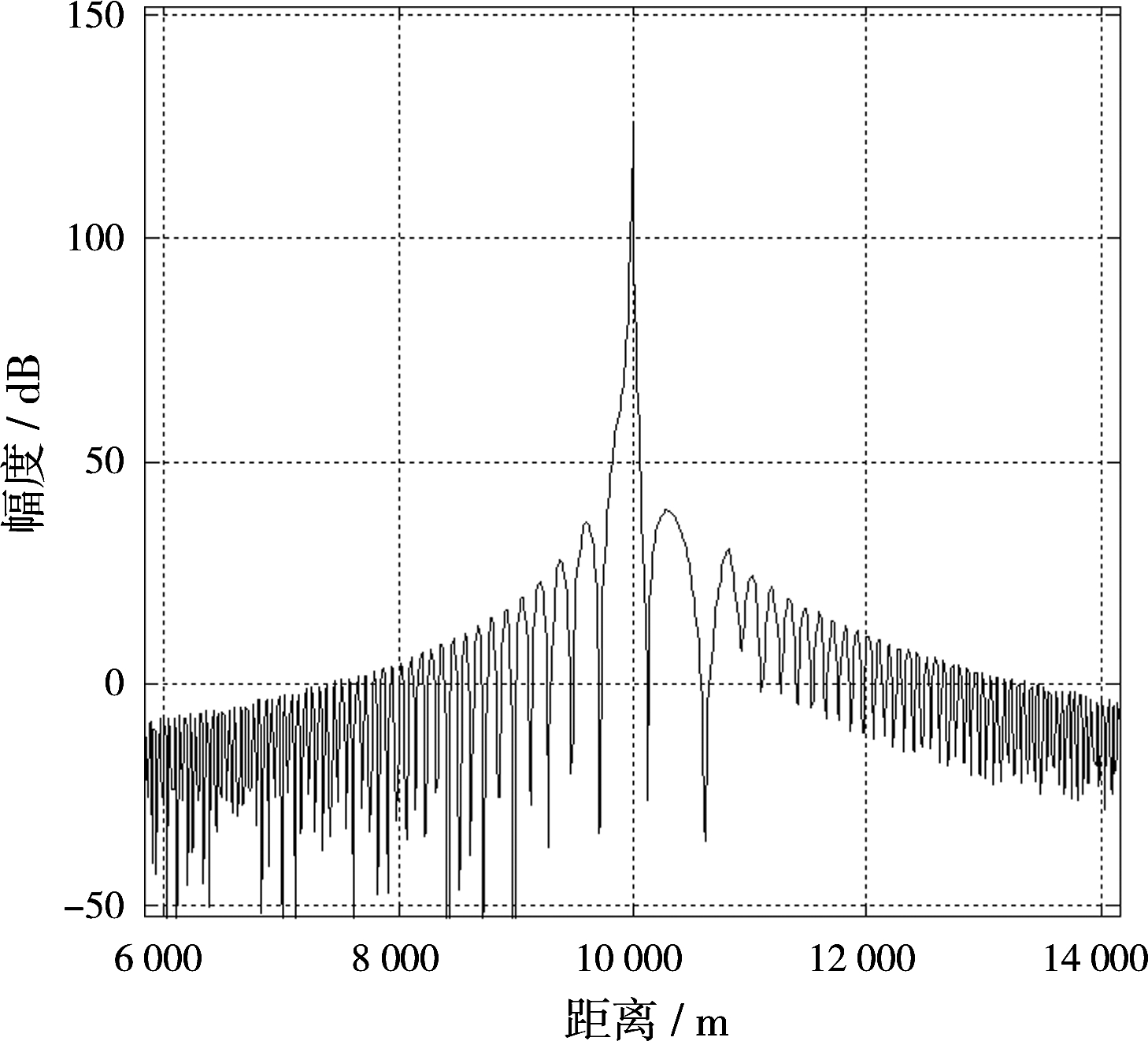

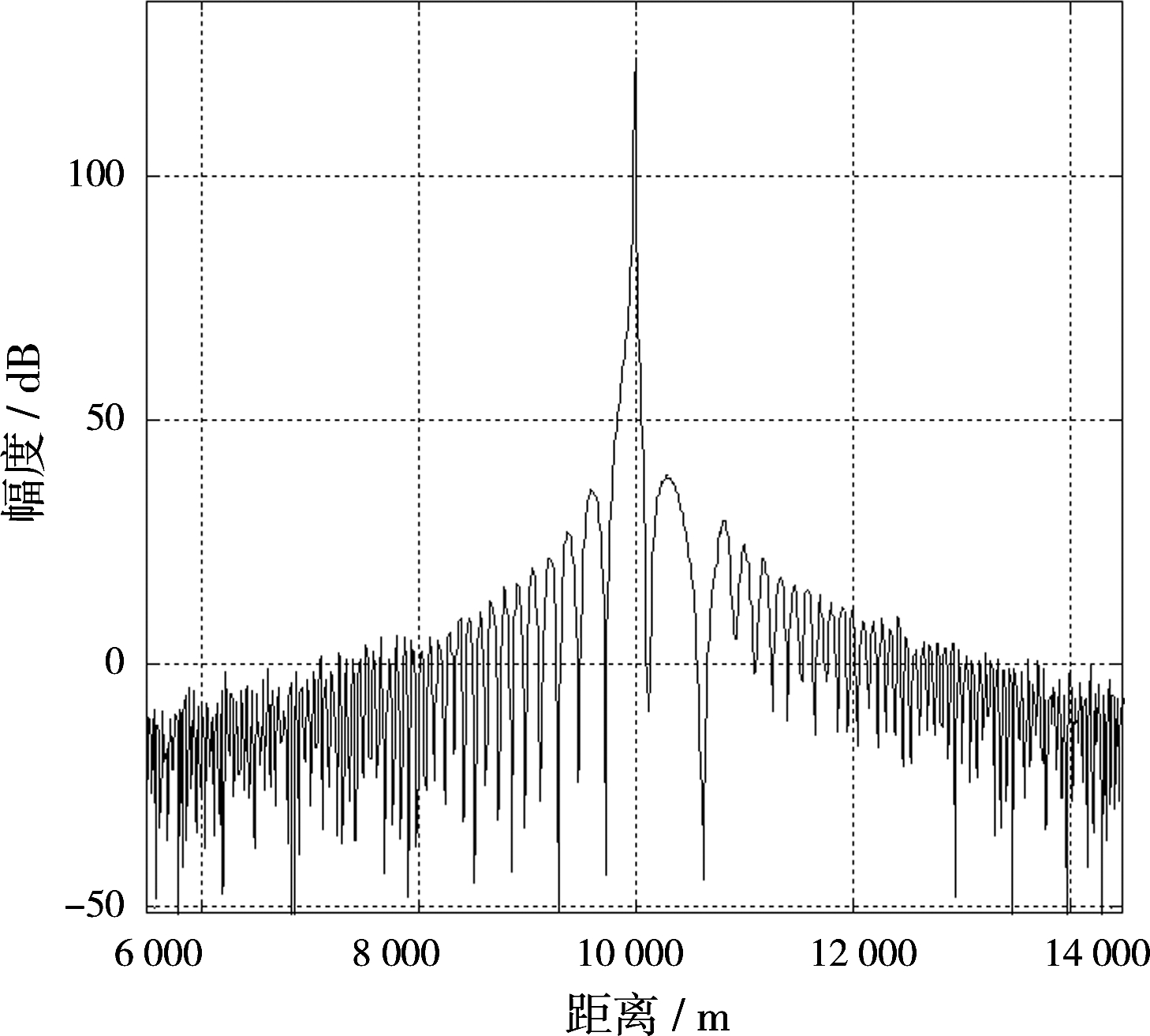

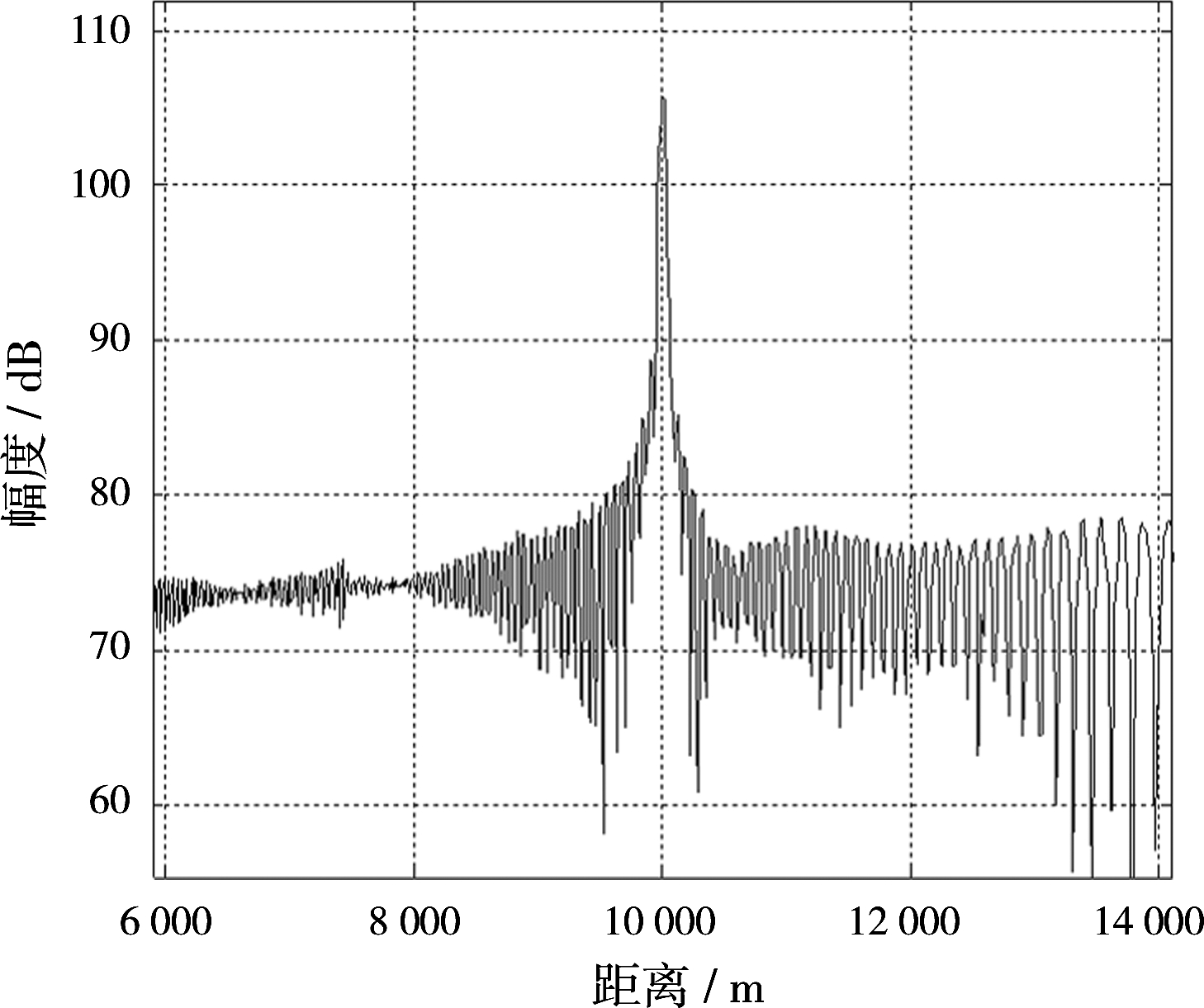

在实现FPGA框架搭建实现后,再进行FPGA电路的功能仿真(RTL级行为仿真),通过testbench文件对工程进行激励并仿真运行得到数据结果。图7为通过Modelsim软件得到的电路RTL仿真结果。设置的仿真模式为模式1,FFT与IFFT的点数为8 192点,点目标位置为x=10 000 m。

可以看出仿真得到的脉压结果与MATLAB仿真结果一致,信噪比较高,且峰值的位置与设定目标位置一致。

(a)MATLAB仿真结果

(b)RTL仿真结果

图7FPGA脉压结果信号与MATLAB仿真对比

3.2 板级测试结果分析

通过Modelsim的仿真结果可以看出,测试信号通过系统得到了目标信息,下面通过Quartus平台的工具Signal Tap II Logic Analyzer将Verilog全编译得到的.sof文件下载到SAR系统信号处理板的FPGA芯片中,进行板级仿真。

模式1通过MATLAB计算产生回波数据导入FPGA中的只读存储器ROM中的与RIGOL DG4162信号发生器产生的模拟回波信号,两种回波信号方案分别进行板级测试。测试系统选择为模式1,测试回波信号同样为模式1信号,设置的目标x=10 000 m,带宽为12 MHz,另外信号发生器产生的模拟信号需要经过进行AD采集模块才得到数字信号。

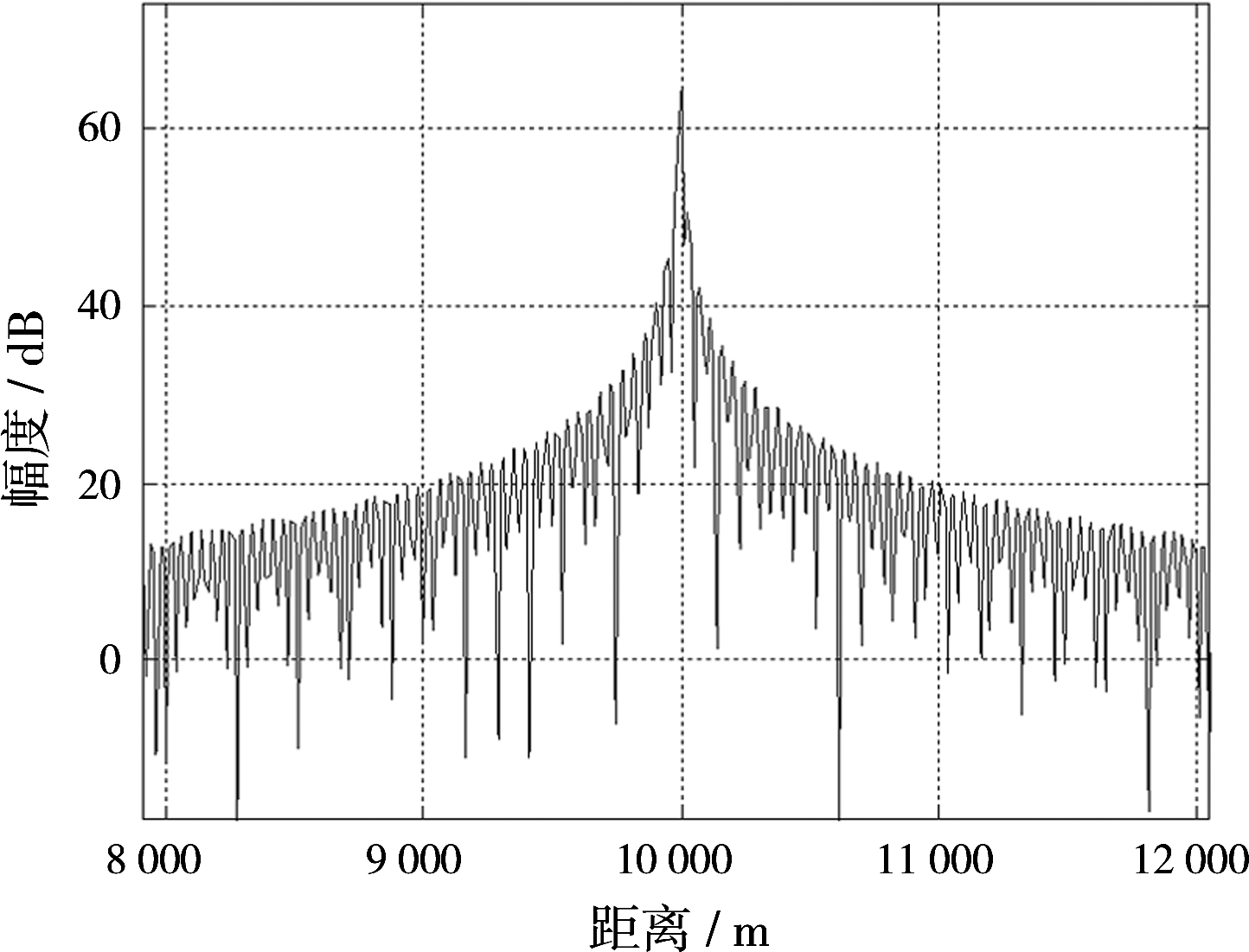

图8为Signal Tap II得到的脉压结果,即为板级仿真的脉冲压缩结果,图8(a)为存储器ROM模拟回波得到的脉压结果,图8(b)为信号发生器产生的模拟信号进行AD采集得到的脉压结果,均得到了点目标x=10 000 m的距离信息。

(a)存储器ROM模拟回波脉压结果

(b)信号发生器模拟回波脉压结果

图8板级仿真Signal Tap数据捕捉结果频谱

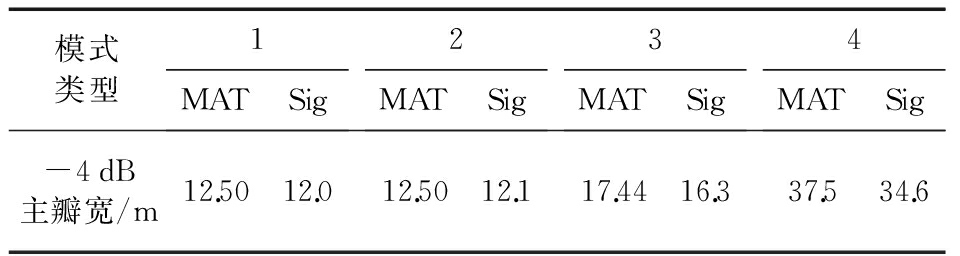

从图8(a)可以看出,存储器模拟的数字回波得到的结果很接近RTL仿真结果,但是由于电路板实测原因信噪比有一定程度的损失。而图8(b)是信号发生器模拟信号的回波得到的结果,由于回波信号来自于信号发生器则噪声比前者更多,但信号发生器的数据更加接近实际接收回波。下面将信号发生器测试的数据对x=10 000 m的各个脉冲压缩质量与MATLAB仿真结果进行对比统计,如表2所示,其中MAT表示MATLAB仿真结果,Sig表示Signal Tap II捕捉结果。

表2 FPGA设计模式误差分析

从Signal Tap II捕捉结果参数看,主瓣宽度误差很小,得到了理想的结果。

4 结束语

本文针对合成孔径雷达系统距离向的点目标探测,提出了一种多模式脉冲压缩的设计方案。设计方案通过NCO数字本振、FIR滤波器、CIC滤波器等模块完成数字下变频,通过FFT以及ROM等模块完成基带信号匹配滤波。并通过RTL仿真以及板级实验进行了验证,都满足FPGA芯片的资源限制要求,实现了点目标的反演并达到了理想的距离分辨率。然而,仅仅距离向的解调并没有完成雷达系统的所有任务。因此,接下来的工作就在于方位向匹配滤波的实现,完成整个合成孔径雷达系统的硬件设计。

参考文献:

[1]蔡永俊,张祥坤,姜景山. 调频连续波合成孔径雷达回波建模与信号分析[J]. 电波科学学报, 2015, 30(6):1158-1162.

[2]孙兵,周荫清,李千池,等.环扫SAR的快速聚焦成像算法[J].北京航空航天大学学报, 2007, 33(7):803-806.

[3]喻黎霞,王辉,周计文. 基于软件无线电的数字下变频原理和实现[J]. 微处理机, 2008, 29(4):189-191.

[4]伍小保,王冰,陶玉龙.基于FPGA多通道多带宽多速率DDC设计[J].雷达科学与技术, 2016, 14(4):403-410. WU Xiaobao, Wang Bing, TAO Yulong. Multi-Channel Multi-Bandwidth and Multi-Rate DDC Design Based on FPGA[J]. Radar Science and Technology, 2016, 14(4):403-410.(in Chinese).

[5]高西全,丁玉美.数字信号处理[M].3版.西安:西安电子科技大学出版社, 2008.

[6]关涛,朱运航,常文革,等.数字下变频与脉冲压缩系统的设计与实现[J].雷达科学与技术, 2010, 8(2):133-145. GUAN Tao, ZHU Yunhang, CHANG Wenge, et al. Design and Implementation of Digital Down-Conversion and Pulse Compression System[J].Radar Science and Technology, 2010, 8(2):133-145.(in Chinese)

[7]邱丽原. 线性调频信号脉冲压缩仿真与分析[J]. 电子科技, 2011, 24(7):117-119.

[8]黄世峰,陈章友,张兰,等. 多通道雷达数字接收机数字下变频设计[J]. 电子技术应用, 2016, 42(6):46-48.

[9]苏斌,刘畅. 基于FPGA的脉冲压缩处理器设计与实现[J]. 电子测量技术, 2014, 37(7):57-61.

[10]高翠翠,林明. 线性调频脉压信号的旁瓣抑制方法[J]. 江苏科技大学学报(自然科学版), 2016, 30(2):151-155.