0 引言

脉冲超宽带雷达有着固有的高距离分辨率及良好的穿透特性,可实现对非金属障碍物后面隐藏目标的探测和定位,在军事、反恐、安检、救灾和医疗等领域有着重大的应用前景[1-2]。脉冲超宽带雷达信号的脉宽一般在纳秒以下,信号带宽一般大于2 GHz,直接数字化会对ADC器件的采样率提出极高的要求,接收机硬件电路的设计与制作十分困难,成本昂贵。当前普遍采用的方法是根据回波信号在一段时间内呈准静态及周期性的特点,采用等效时间采样原理实现对超宽带信号的数据采集,从而大大降低采样率[3-4]。

等效采样方法主要有两种:顺序等效采样和随机等效采样[5]。顺序等效采样是每个触发后经过一个微小而确定的延迟就采集一个样值。当下一次触发到来时,延迟增加一段小的增量Δt,该增量就是等效采样的周期,再采集一个样值。该过程重复多次,延时不断累加,直到填满整个时间窗口。随机采样是通过精心设计触发信号周期和采样时钟周期之间的比例关系,一般为互质数,使采样孔径能够在多次采样后遍历波形上的兴趣点,再进行数据重排以达到波形重构[6]。

当前顺序等效采样和随机等效采样方法都存在一个共同的问题,就是数据的模糊与重组。对于顺序等效采样,普遍的做法是不断改变采样时钟的相位以达到数据延时的效果,这必然会带来采样时钟对触发信号的亚稳态时序,使得顺序等效采样的第一个数据点难以定位,必须通过离线或在线的方法来辅助校正,增加了软硬件复杂度。对于随机等效采样,准确测量每次信号触发时刻与ADC第一个采样时钟的时间差也是难点,同样使第一个数据采样点难以定位,必须增加校正手段。

本文提出了一种改进型的顺序等效采样方法,基于FPGA内置的输出延时线来控制波形发射触发信号,使发射波形实现真时延调整,从而控制回波的时延变化。再基于大带宽采样保持器和高速ADC器件,在FPGA内完成数据重排与平均积累处理,实现超宽带信号的等效采样。

1 改进型的顺序等效采样

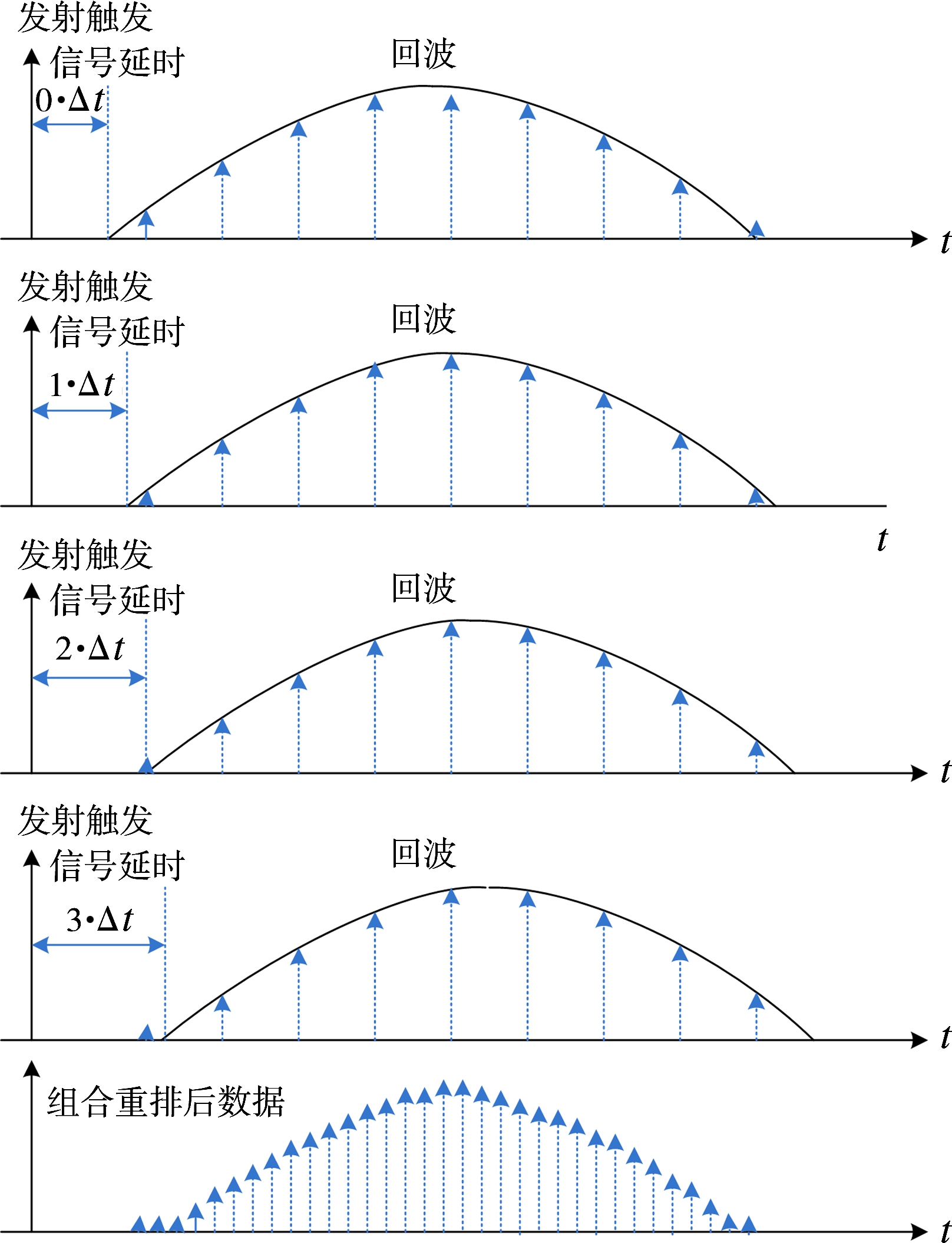

对传统的顺序等效采样方法进行两方面优化:一是在一个发射触发周期内采集多个样点,缩减复原信号所需要的时间,同时减少延时单元的级数;二是以延时信号来代替延时时钟,以消除时钟锁定死时间、软件时序重启以及时钟周期性模糊等一系列问题。改进型的顺序等效采样原理如图1所示。

图1 改进型顺序等效采样原理框图

取可控单位延时Δt为TADC/n,其中TADC为ADC的采样时钟周期,n为等效采样次数。在第一个发射触发时,FPGA输出发射触发信号的延时为0·Δt,采集一组计m个数据,记为

S0=[S(TADC),S(2TADC),S(3TADC),…,

S(mTADC)]

(1)

在第二个发射触发时, FPGA输出发射触发信号的延时为1·Δt,采集一组计m个数据,记为

S1=[S(TADC-Δt),S(2TADC-Δt),

S(3TADC-Δt),…,S(mTADC-Δt)]

(2)

在第n个发射触发时, FPGA输出发射触发信号的延时为(n-1)·Δt,采集一组计m个数据,记为

Sn-1=[S(TADC-(n-1)Δt),S(2TADC-(n-1)Δt),

S(3TADC-(n-1)Δt),…,S(mTADC-(n-1)Δt)] (3)

将这n组数据在时域上重新组合,代入Δt=TADC/n,即可恢复出正确的时域波形:S=[S((1/n)TADC),S((2/n)TADC),S((3/n)TADC),…,

S(((m·n)/n)TADC)]

(4)

由式(4)可知,数据的采样间隔变为TADC/n,等效采样率提升了n倍。

2 接收机实现方案

接收机系统主要由接收前端、数字接收机和低相噪时钟源组成。接收前端输入天线接收的回波信号,低噪声放大至功率合适的电平后送给数字接收机。数字接收机基于采样保持器(S/H)+ADC+FPGA的实现架构,对模拟回波信号进行模数转换、积累平均和数据缓存重组,再将数据送给信号处理板进行雷达信号处理;同时生成延时可控的发射触发信号给窄脉冲产生模块,用以控制发射脉冲的延时。低相噪时钟源用来产生S/H和ADC的低抖动采样时钟以及FPGA的工作时钟,给整机提供统一的时钟参考。

图2 接收机系统框图

Xilinx公司的FPGA具有大量的I/O延时调整单元,非常适用于产生延时可控的发射触发信号。使用带输出延时功能的FPGA管脚,系统硬件上可省去高精度延时芯片及相关外设电路,简化了电路设计。当FPGA参考时钟为200MHz时,FPGA内置延时线延时最小步进为1/(64·200MHz)=78.125ps,延时调整值为(0~31)·78.125ps。78.125ps对应的等效采样率为12.8GS/s,等效采样次数为32,故ADC的采样率为12.8 (GS/s)/32=400MS/s。

3 定时误差分析

对于等效采样,恢复波形的精度主要取决于采样定时误差。本系统中的采样定时误差主要由以下几方面组成:

1)S/H采样时钟的抖动Tj_SH

S/H采样时钟的抖动主要取决于采样时钟源的相噪指标和时钟管理模块的附加抖动,降低该抖动需要采用相噪超低的晶振或原子钟作参考,选用低附加抖动的时钟管理芯片。

2) 发射触发的延时抖动Tj_trig

发射触发的延时抖动主要来源于FPGA内置延时线和高速驱动接口的时序抖动误差,取决于硬件电路的输出附加抖动指标,受温度和湿度等环境因素影响较大。在精度要求较高的应用场合,需要对系统添加辅助的环控装置。

3) 各周期间发射信号相对于发射触发的抖动Tj_trans

可等效为发射波形的定时触发抖动,其主要取决于波形产生模块中定时触发电路的精度和稳定性。

以上3种定时误差可以统一等效为采样时钟抖动Tjitter。通常认为时钟抖动噪声互不相关,且服从高斯分布,则

(5)

在S频段以上的射频采样系统中,采样输出信号的信噪比(SNR)主要受限于时钟抖动[7]。Tjitter对SNR的限制如下:

SNR=-20 lg(2·π·fin·Tjitter)

(6)

式中,fin为输入信号频率。fin=6 GHz,期望SNR≥40 dB时,Tjitter≤0.27 ps;fin=6 GHz,期望SNR≥30 dB时,Tjitter≤0.83 ps;fin=6 GHz,期望SNR≥20 dB时,Tjitter≤2.67 ps。

如需达到40 dB的采样信噪比,要求3种定时误差的总抖动要小于0.27 ps,这在工程上很难实现,即使能达到该要求,也是以极其昂贵的时钟源和信号产生及定时定路为代价的。为了降低时钟抖动要求,工程应用中通常采用多周期数据积累平均的方法来提升信噪比。依据常规元器件工艺水平,总定时误差为0.5~1 ps,数据积累平均前所能达到的最高信噪比约为30 dB。

4 硬件实现

4.1 接收前端

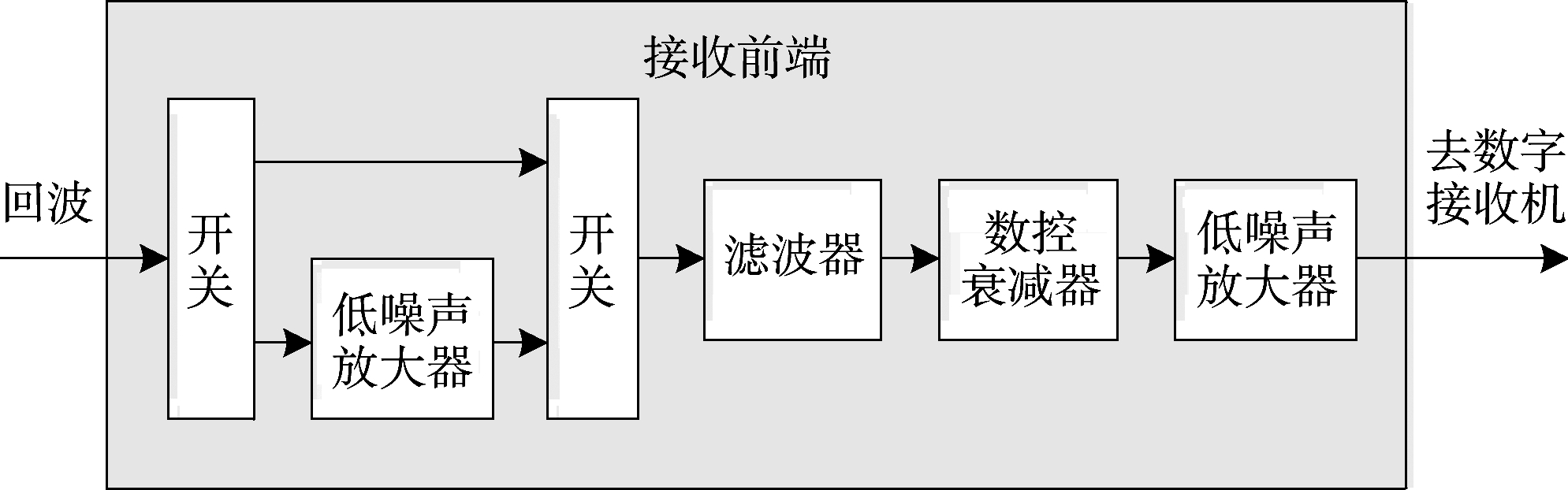

脉冲超宽带雷达的障碍物直接反射杂波与近端目标回波是叠加在一起的,为了避免杂波对接收机前端饱和以至于影响近端回波的接收,需要在低噪放之前利用数控衰减器对杂波进行衰减。同时,为了增加系统动态范围和实现对远端弱回波信号的有效探测,系统通过开关选择来实现对近端和远端回波的分时接收,使用数控衰减器来控制通道增益。分时接收会造成开关切换时间内回波接收数据的异常中断,在不同回波周期内保证一定的数据时间段交叠就可以解决此问题。

接收前端的链路框图如图3所示,主要由开关、低噪声放大器、滤波器和数控衰减器等组成。低噪声放大器将信号放大至T/H所需的合适电平;滤波器主要用来对回波信号进行抗混叠滤波,将信号频段限制在等效采样的第一Nyquist带内,即低于6.4 GHz;数控衰减器对链路进行增益调整,防止低噪声放大器和T/H饱和。

图3 接收前端链路框图

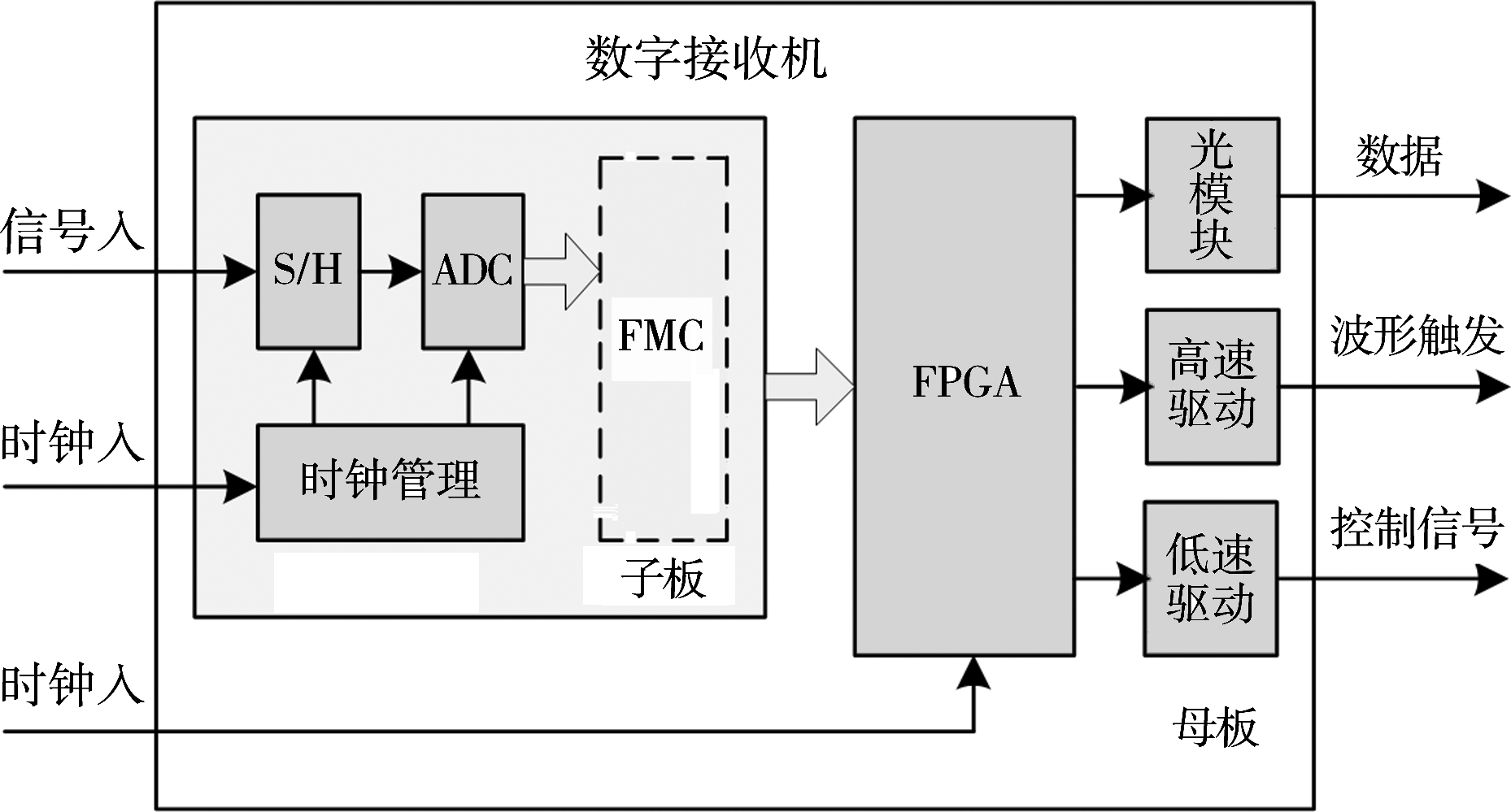

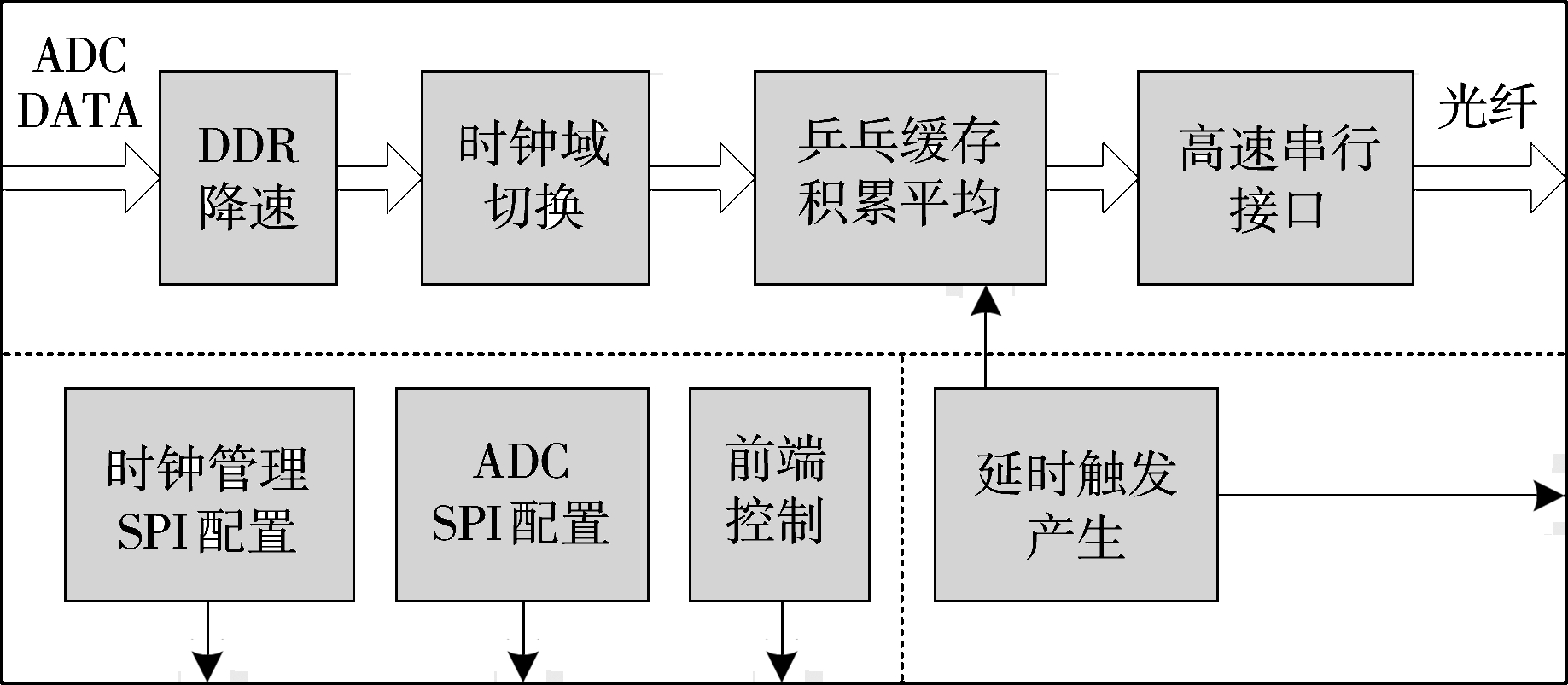

4.2 数字接收机

数字接收机采用通用灵活的FMC子母板架构,由高速欠采样ADC子板和FPGA母板组成,如图4所示。高速欠采样ADC子板由采样保持器(S/H)、ADC和时钟管理芯片等组成,用来完成信号的模数转换,并将数据通过FMC接口送给母板。FPGA母板主要由FPGA芯片、光模块以及高/低速驱动电路等组成,主要用来完成系统等效采样的时序控制和数据处理,生成窄脉冲产生模块所需要的高速触发信号和接收前端的开关及增益控制信号,并通过光纤将等效采样数据送给信号处理板。

图4 数字接收机功能框图

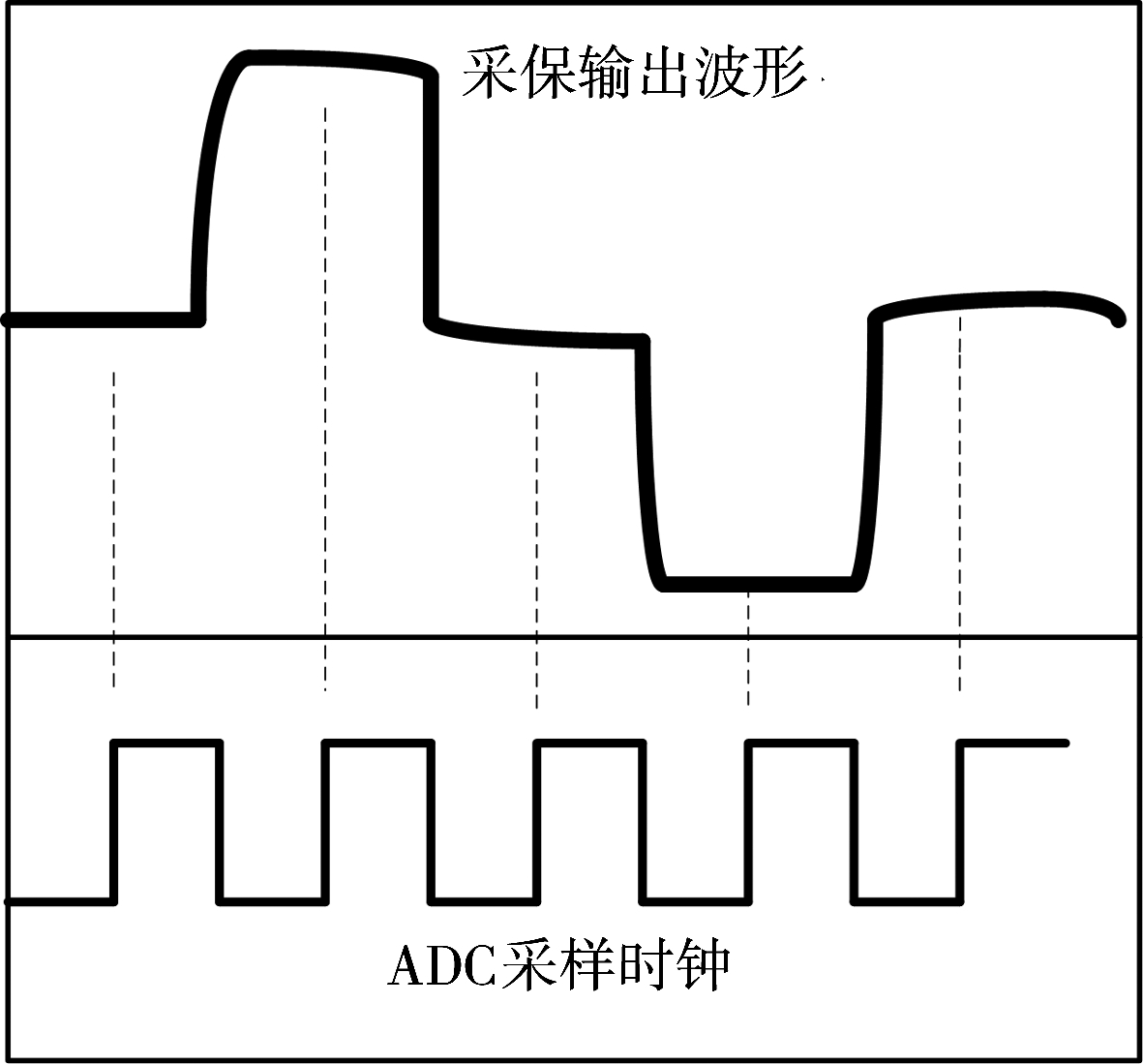

脉冲超宽带信号的频段上限通常为5 GHz以上,常规ADC芯片的模拟带宽难以满足要求,需要外置高带宽采样保持器(S/H)才能完成窄脉冲信号的数字化接收。采样保持器选用Hittite公司生产的HMC1061LC5芯片,采用主从设计,包含两级采样保持电路,降低了S/H与ADC之间的时序接口要求。主从两级采样保持器可以共用一路时钟,也可各自供给时钟。采样保持器输入信号的-3 dB带宽为18 GHz,最大采样率为4 GS/s,4 GHz模拟输入时SFDR为56 dB,保持模式下射频泄露抑制度大于65 dB,保持模式输出噪声RMS值为1.5 mV。ADC采用Intersil公司的ISLA214P50芯片,14 bit精度,最大转换速率为500 MS/s,满足系统400 MS/s的应用需求。子板上时钟管理模块主要由高速时钟驱动器和可编程时钟延时器组成,用来生成采样保持器采样时钟和ADC采样时钟,同时调整这两种时钟之间的相对时延,使ADC采样时钟的上升沿位于保持脉冲的中间位置(对应着最大的建立/保持时间裕量),使采样时序达到最优,如图5所示。高速时钟驱动器采用Hittite公司的HMC987LP5E芯片,输入频率范围为DC~8 GHz, 9个端口扇出,8 GHz输出时的附加抖动为50 fs。可编程时钟延时器采用Hittite公司的HMC988LP3E芯片,输入频率范围为DC~4 GHz,可调时延步进为20 ps,最大可调步长为60 ps, 2 GHz输出时的附加抖动为13 fs, 控制接口为SPI总线。为了减小触发信号的上升时间,减小定时抖动误差, FPGA产生的波形触发信号由高速驱动芯片SN74AVC4T245驱动,1.8 V到3.3 V的最大传输速度为380 Mbit/s。

图5 T/H输出波形与ADC时钟之间的最优时序关系

4.3 低相噪时钟源

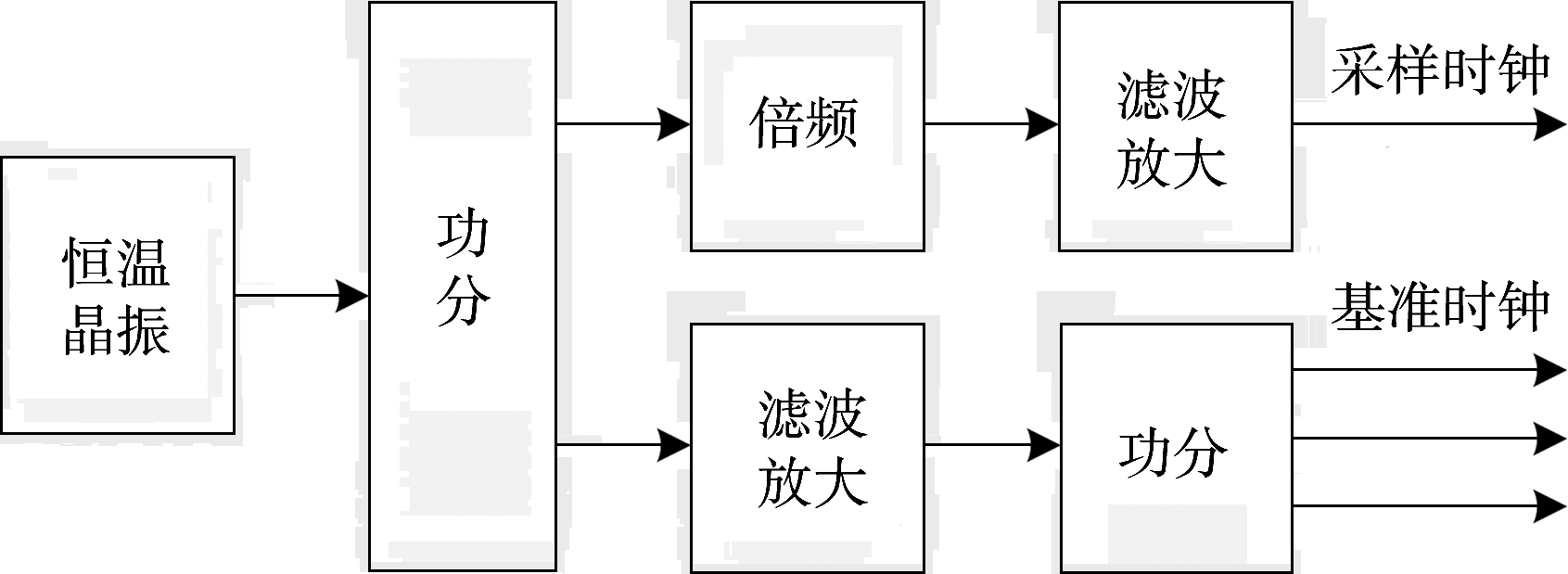

为了最小化系统时钟抖动,基准时钟源采用低相噪恒温晶振作为参考,功分两路,一路通过倍频和滤波放大生成S/H和ADC的采样时钟,另一路经过滤波放大和功分后作为数字接收机、波形产生模块以及信号处理板的基准参考时钟,如图6所示。接收机选用100 MHz恒温晶振的相噪低于-155 dBc/Hz@1 kHz,频率温度稳定度低于±0.5×10-6。

图6 低相噪时钟源功能框图

5 FPGA逻辑设计与工作流程

FPGA内部逻辑主要由外设芯片配置/控制、数据流处理以及延时触发三大功能模块组成,如图7所示。外设芯片配置/控制模块用来对时钟管理芯片、ADC芯片进行初始化配置,同时在工作过程中实现对接收前端的开关选择与增益控制;数据流处理模块由DDR降速、时钟域切换、乒乓缓存积累平均以及高速串行接口等组成,主要完成等效采样数据的存储、累积、重排与传输;延时触发模块用于产生等效采样时序,输出延时控制命令与内/外触发信号。

图7 FPGA逻辑功能框图

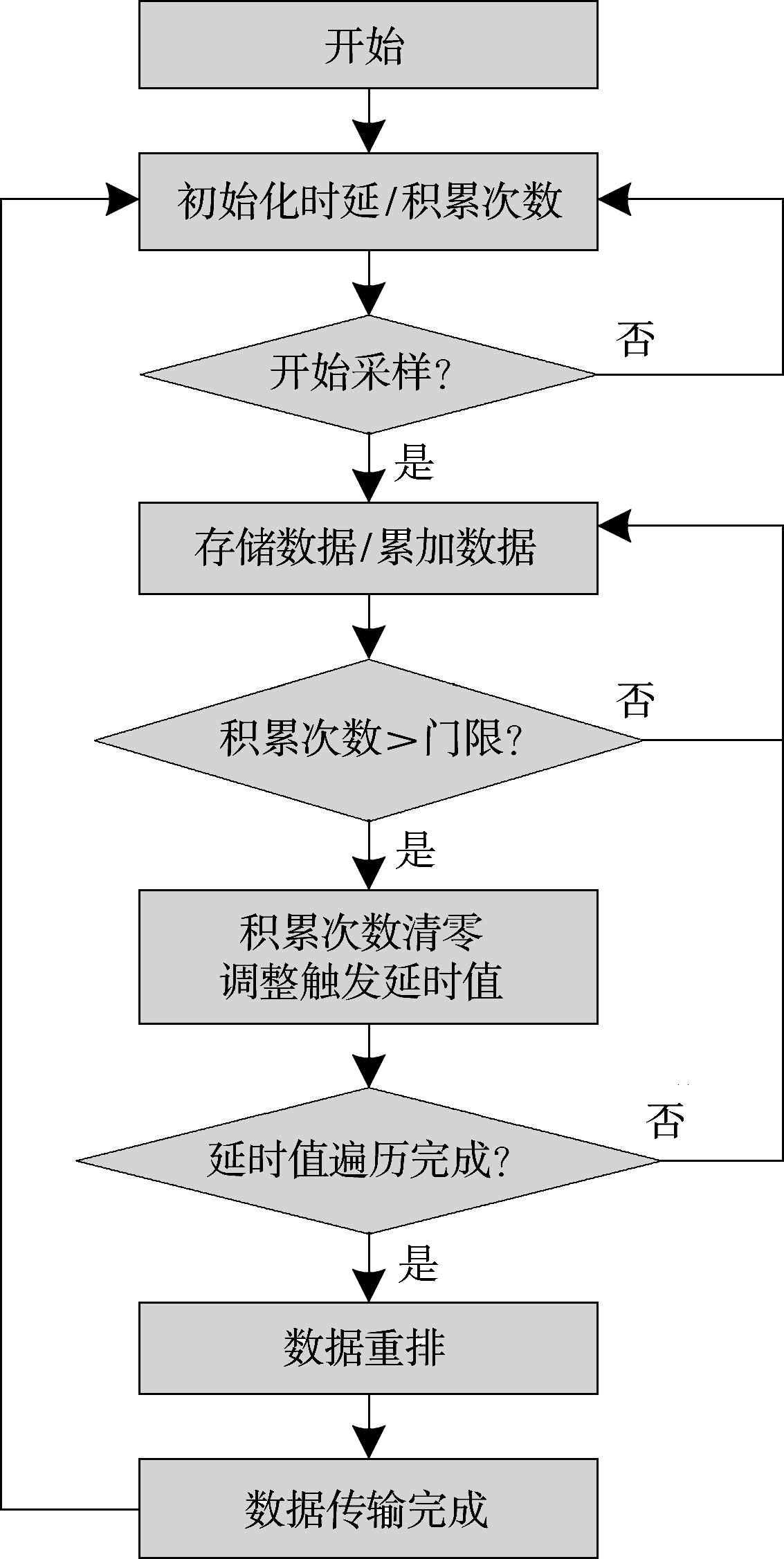

接收机工作流程如图8所示。开始工作时,初始化发射触发时延和数据累积次数计数值。在收到开始采样命令后,在触发信号的同步下完成预定累积次数的数据采集和存储。之后增加触发时延值,重复完成数据采集和存储,直至触发时延变为最大值。最后将所有数据在时域上重排后送给信号处理板,从而完成一次等效采样。

图8 接收机工作流程图

6 测试结果及分析

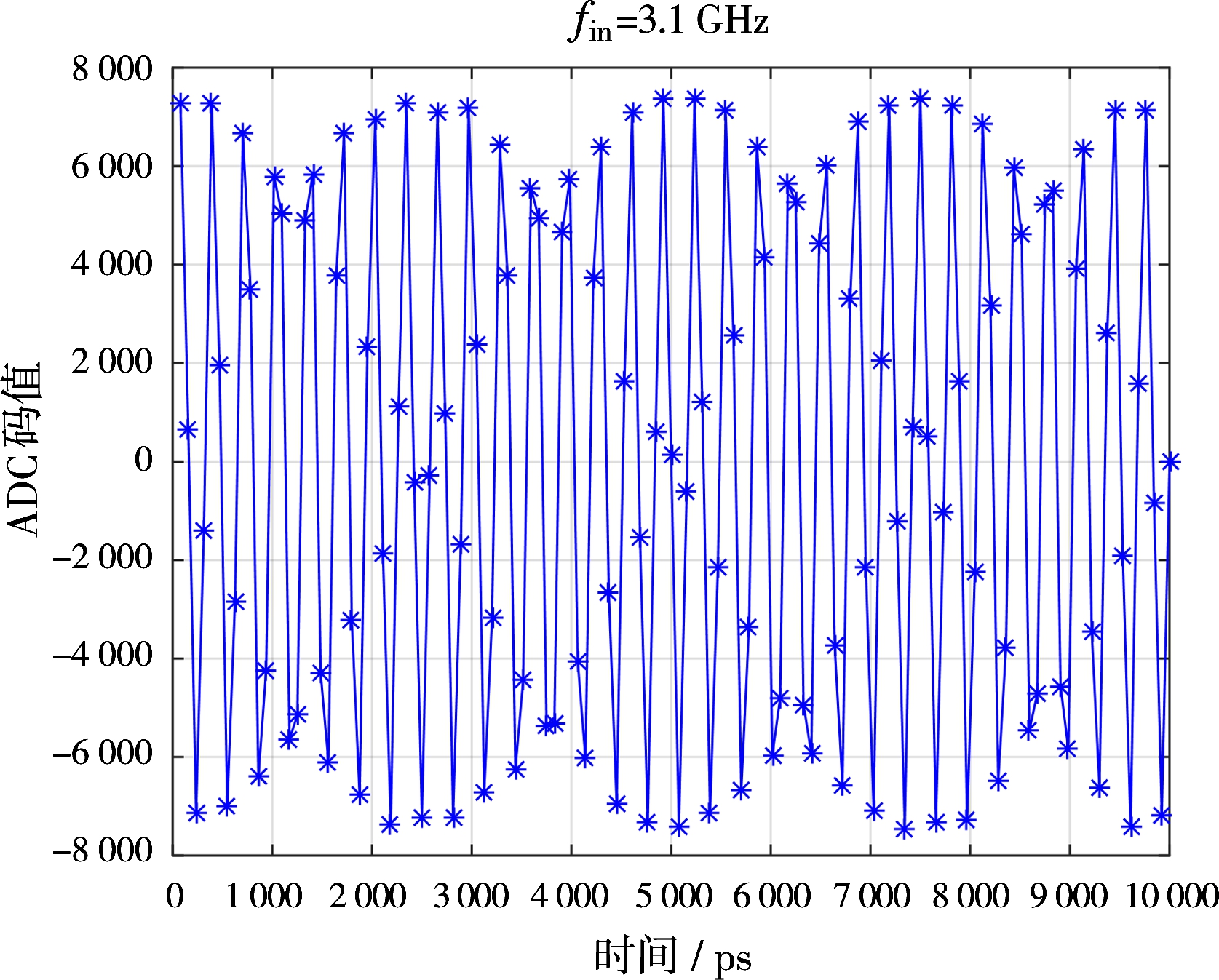

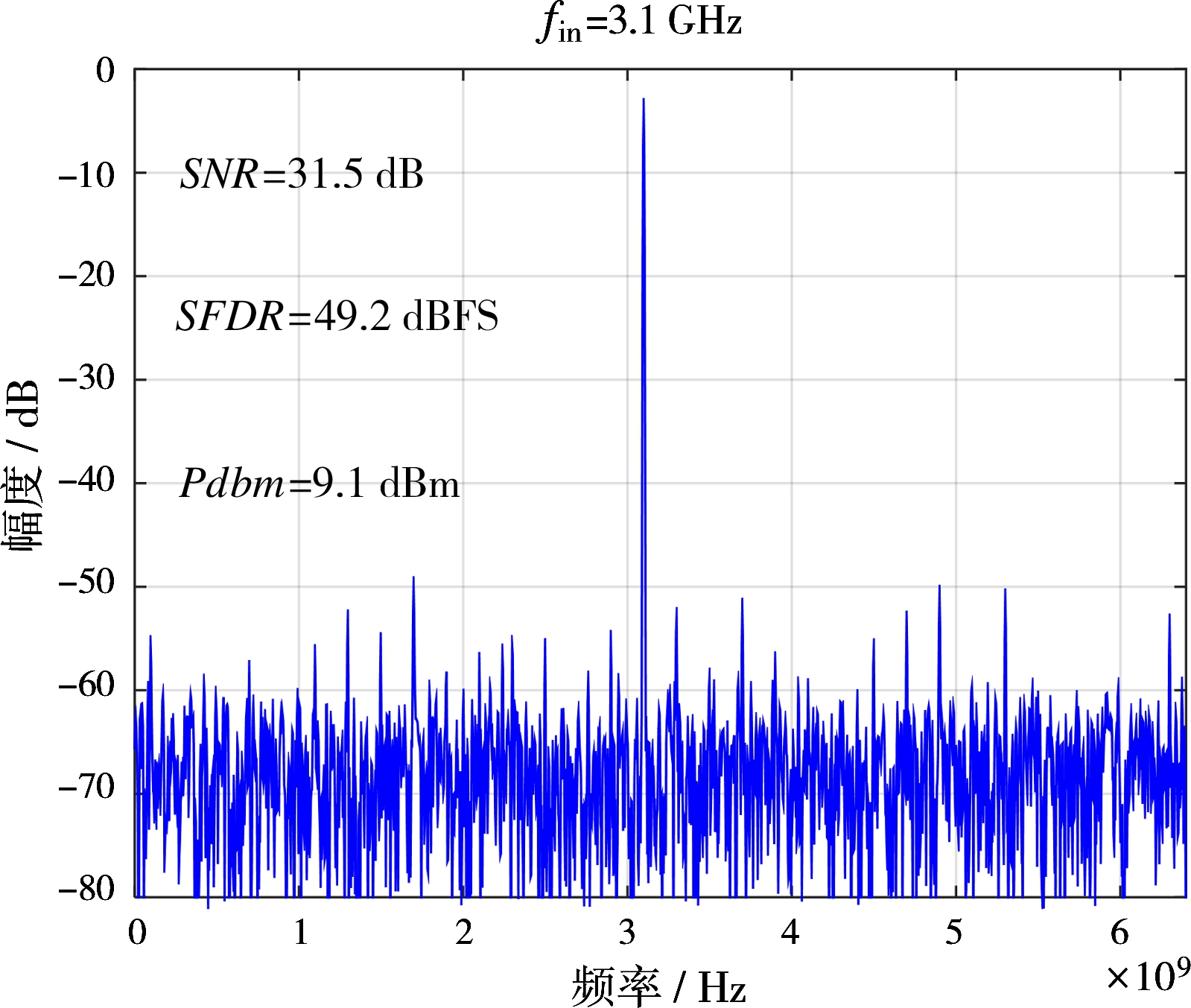

在同步触发的控制下,波形产生模块产生3.1 GHz的点频连续波送给接收机。系统触发重频为1 MHz,ADC采样率为400 MS/s,每个触发周期采样128点数据,等效采样倍数为32。接收机等效采样的时域波形和频谱如图9和图10所示。可以看出,接收机的等效采样率为12.8 GS/s。鉴于系统定时抖动的影响,信号的信噪比限制为31 dB,与前面分析基本吻合。更高射频输入时会产生更大的幅度采样误差,信噪比会进一步恶化。在信号回波特征变化不明显的时间区间内,可采用多周期积累平均的方法来改善信噪比。

图9 等效采样数据的时域波形

图10 等效采样数据的频谱曲线

7 结束语

本文介绍了一种应用于窄脉冲回波探测的超宽带等效采样接收机,描述了系统软硬件的具体实现,给出了等效采样数据的测试结果。提出了一种基于FPGA内置延时线的改进型等效采样方案,基于触发信号真时延调整方法,不改变采样时钟相位,无需进行多次采样数据之间的时序错位校正。接收机等效采样率为12.8 GS/s,最高输入信号频率为6.4 GHz,在窄脉冲回波探测领域中具有很好的应用前景。

参考文献:

[1]WANG Y, FATHY A E. Advanced System Level Simulation Platform for Three-Dimensional UWB Through-Wall Imaging SAR Using Time-Domain Approach[J]. IEEE Trans on Geoscience and Remote Sensing, 2012, 50(5):1986-2000.

[2]刘俊斌,吴松林,周卫星. 基于FPGA实现的高速等效采集系统[J]. 电子技术应用, 2011, 37(10):84-86.

[3]刘莎,张福洪,易志强. 一种基于FPGA的高精度随机等效采样系统的实现[J]. 南阳理工学院学报, 2016, 8(2):5-8.

[4]陈培哲,曾刚,黄志远,等. 冲激脉冲的等效采样研究[J].电子测量技术, 2014, 37(10):55-58.

[5]胡恺,欧阳缮,徐五生. 超宽带穿墙雷达数据采集系统的设计与实现[J]. 桂林电子科技大学学报, 2015, 35(1):10-14.

[6]郭宇,朱国富. 全新的高稳定穿墙雷达接收机前端设

计[J]. 雷达科学与技术, 2015, 13(2):203-209. GUO Yu, ZHU Guofu. Design of a Novel High-Stable Receiver Front-End of Through-Wall Radar[J]. Radar Science and Technology, 2015, 13(2):203-209.(in Chinese)

[7]段宗明,柴文乾,代传堂.时钟抖动和相位噪声对数据采集的影响[J].雷达科学与技术, 2010, 8(4):372-375. DUAN Zongming, CHAI Wenqian, DAI Chuantang. Effect of Clock Jitter and Phase Noise on Data Acquisition[J]. Radar Science and Technology, 2010, 8(4):372-375.(in Chinese)