0 引言

在大多数雷达系统的处理架构中,一般由数字中频接收系统完成模拟中频信号模数变换器(Analog to Digital Converter,ADC)采样,并基于现场可编程门阵列(Field Programmable Gate Array,FPGA)实现数字下变频和数据打包输出算法,再由信号处理系统基于数字信号处理器(Digital Signal Processor,DSP)实现基带信号数字脉压和后续处理算法。但是DSP芯片处理速度低、实时性差且并行处理能力弱,使得基于DSP的数字信号处理有着极大的应用局限性。

随着FPGA芯片技术和集成度的高速发展,以及FPGA本身具备的处理速度快、适合并行运算的特点,在雷达数字接收系统和信号处理系统得到越来越广泛的应用。部分信号处理算法(如线性调频信号脉压等)可以前移至数字中频接收系统基于FPGA实现,这样不但能够有效减轻DSP芯片的处理压力,也可以优化信号处理系统的算法架构。在数字中频接收系统中,基于FPGA实现多通道数字下变频、线性调频信号数字脉压和数据打包算法的综合设计,能够有效提升数字中频接收系统的预处理能力。

1 数字脉压方法

1.1 频域相乘法

线性调频信号的脉压工程实现包括时域卷积和频域相乘两种方法。在雷达窄带信号处理系统中[1],线性调频信号脉压长度从几十点到几千点不等,如果采用时域卷积的方式进行脉压,匹配滤波器的设计较为困难。尤其是脉压长度达到几千点数时,无论如何优化设计,匹配滤波器的阶数都太大,其乘法及加法的运算规模可能导致FPGA的资源占用过多而无法实现。

频域相乘[2]的方式主要需要进行快速傅里叶变换(Fast Fourier Transform,FFT)和快速傅里叶逆变换(Inverse Fast Fourier Transform,IFFT)运算,脉压匹配过程是在频域与匹配系数进行点乘。而目前工程上应用较为广泛的FPGA,其开发环境都提供了能够进行FFT和IFFT运算的IP核,这使得信号的时域-频域-时域转换变得不太复杂。这些IP核支持的转换运算长度可达64K点,能够满足雷达窄带系统对绝大多数线性调频信号脉压的处理需求,因此基于FPGA的窄带多通道数字脉压更适合采用频域相乘方式。

设基带线性调频信号为x(n),频域匹配系数为h(n),那么频域脉压运算过程可表示为

将数字下变频后的基带线性调频信号先进行FFT运算,再在频域与脉压匹配系数进行复乘运算,最后进行IFFT运算即获得信号脉压结果。

1.2 匹配系数

除FFT和IFFT运算外,脉压匹配函数的系数计算也是实现脉压的关键,一般可以采用预先存储与实时计算两种方式。预先存储是根据线性调频信号参数,基于Matlab进行计算并将匹配系数存储于FPGA的只读存储器(Read Only Memory,ROM)中[3]。这种存储方式对匹配系数的处理简单,但是设计不够灵活,更适合大带宽线性调频信号、带宽种类较少的情况。

而雷达窄带多通道处理系统一般包含多种带宽和脉宽的线性调频信号,由此导致脉压匹配函数的种类很多,采用匹配系数存储方式需要枚举的数量太多。本文采用雷达系统通过串行通信总线提供回波线性调频信号参数的方式,在FPGA内进行实时FFT计算的方式获得脉压匹配系数的频域形式,这样的方法更加适合窄带多通道、多带宽接收系统的脉压处理。

2 多通道数字脉压

2.1 架构设计

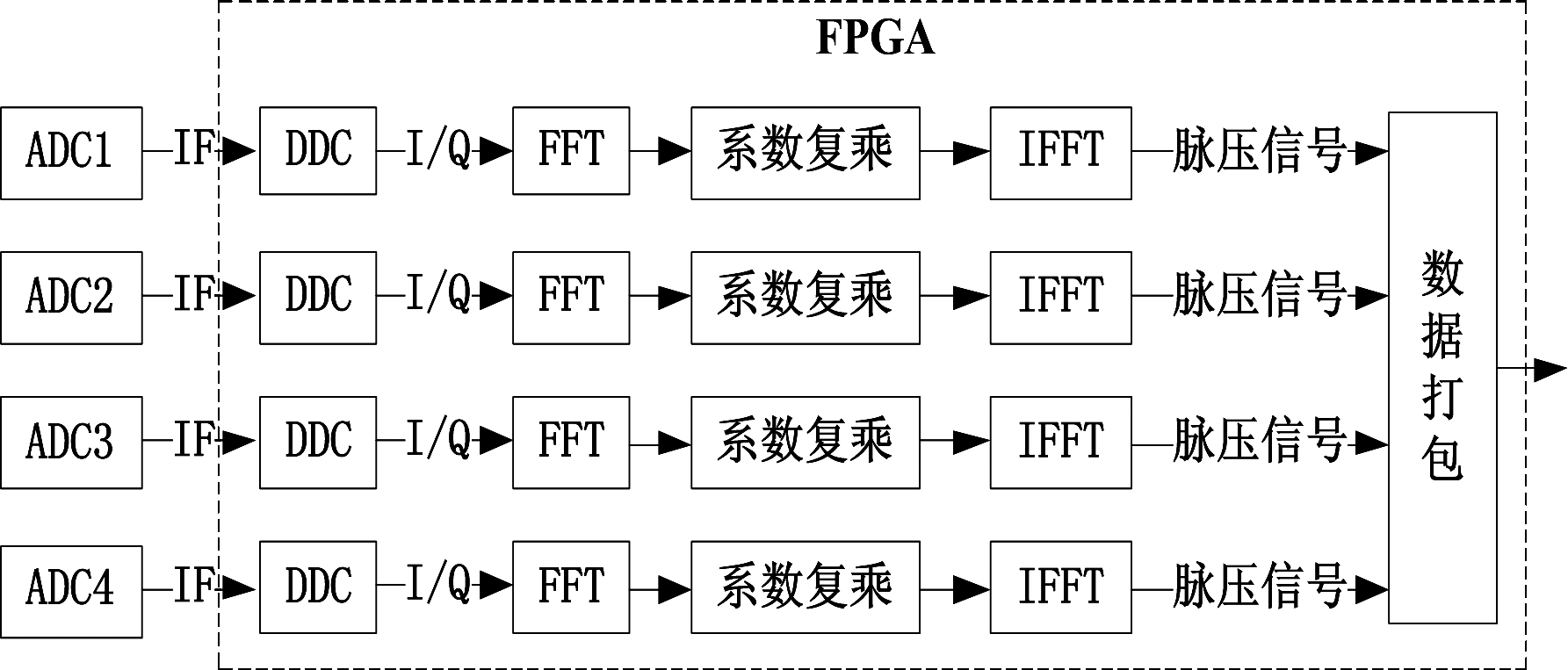

雷达窄带接收系统中通常采用多个接收通道的处理模式。以常用的4个接收通道为例,在窄带数字中频接收系统中,基于单片FPGA不仅实现窄带多通道数字接收、数字下变频和数据打包处理,在FPGA中增加多带宽回波信号数字脉压,与原有功能实现一体化设计架构,如图1所示。各个通道独立完成ADC采样、数字下变频(Digital Down Conversion,DDC)、脉压运算等,再统一进行数据打包输出至处理机完成雷达信号处理系统的后续处理算法。

图1 多通道DDC及脉压一体化设计架构

采用一体化设计架构,将原本在处理系统中基于DSP芯片实现的脉压算法,前移至数字中频接收系统中。数字下变频后的基带信号直接在FPGA内完成数字脉压,与DDC算法无缝对接,优化了雷达系统数据处理模式。脉压后的信号再进行数据打包组合,处理系统可以基于此脉压信号完成后续算法,减少一级脉压处理,使得基带数据流的运算处理更加紧凑。

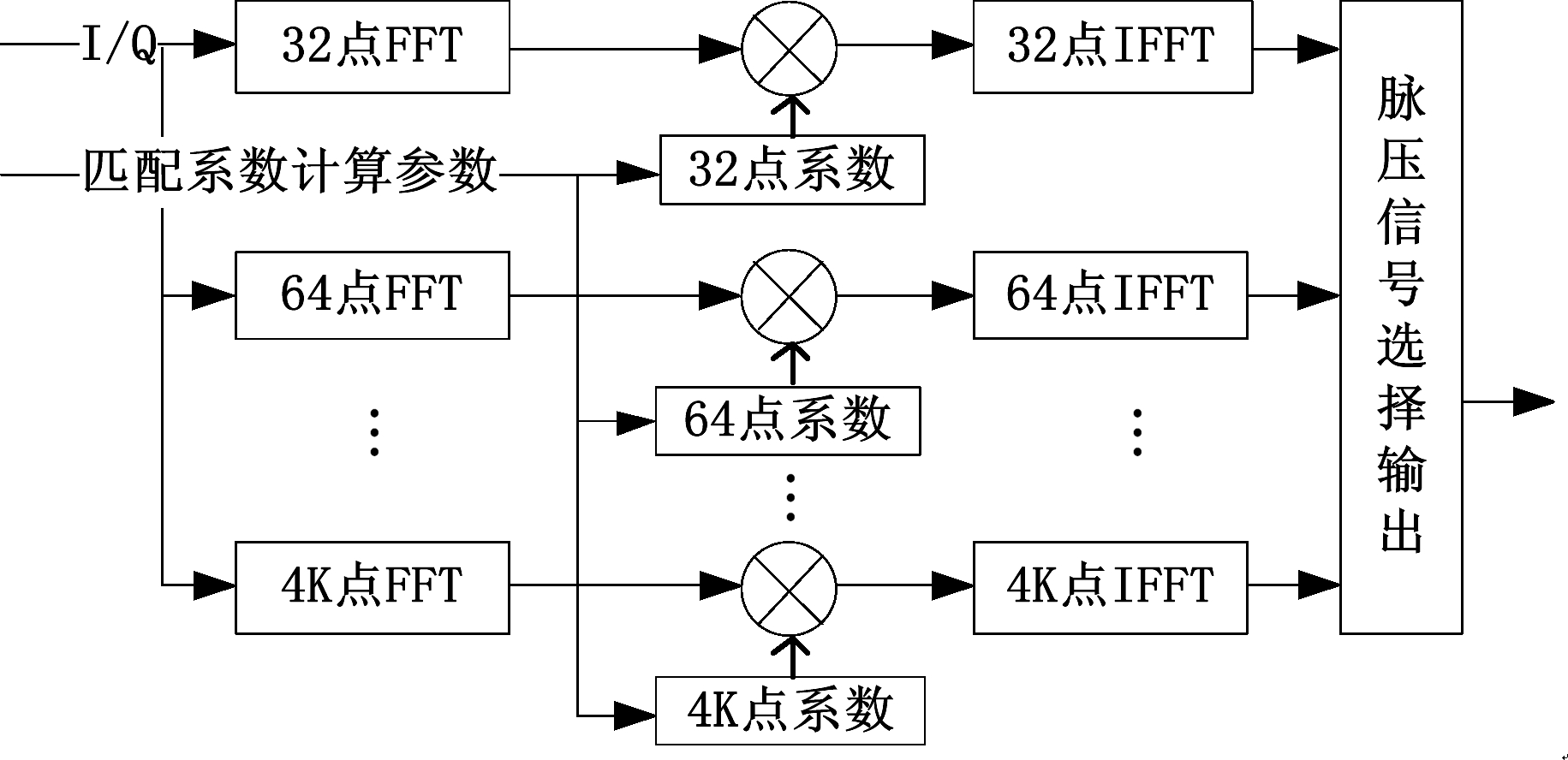

由于窄带接收通道包含多种带宽和脉宽的线性调频回波信号,数字下变频抽取后根据信号带宽的不同可能包含多种基带数据率,脉压运算每个PRI周期进行一次。FFT的IP核要求运算点数满足2N,当数据长度不满足FFT运算要求的2N时还需进行补零操作。结合大多数雷达窄带接收系统的回波参数,线性调频信号脉压的FFT及IFFT计算长度可能包含32,64,128,256,512,1K,2K和4K等多种。

单个接收通道包含多种长度数字脉压的处理架构如图2所示,由于FFT IP核对运算长度不可重加载设置,因此每一种长度的FFT和IFFT均并行平铺设计,而无法多种长度运算共用,这对FPGA资源的消耗将是很大挑战。各种匹配系数的计算根据系统提供的脉宽、带宽和数据率等参数在FPGA实时计算获得。多通道脉压算法的线性调频信号FFT和IFFT运算各自独立进行,但是脉压匹配系数可以在通道间共用,节省FPGA资源消耗。

图2 单通道多长度脉压架构

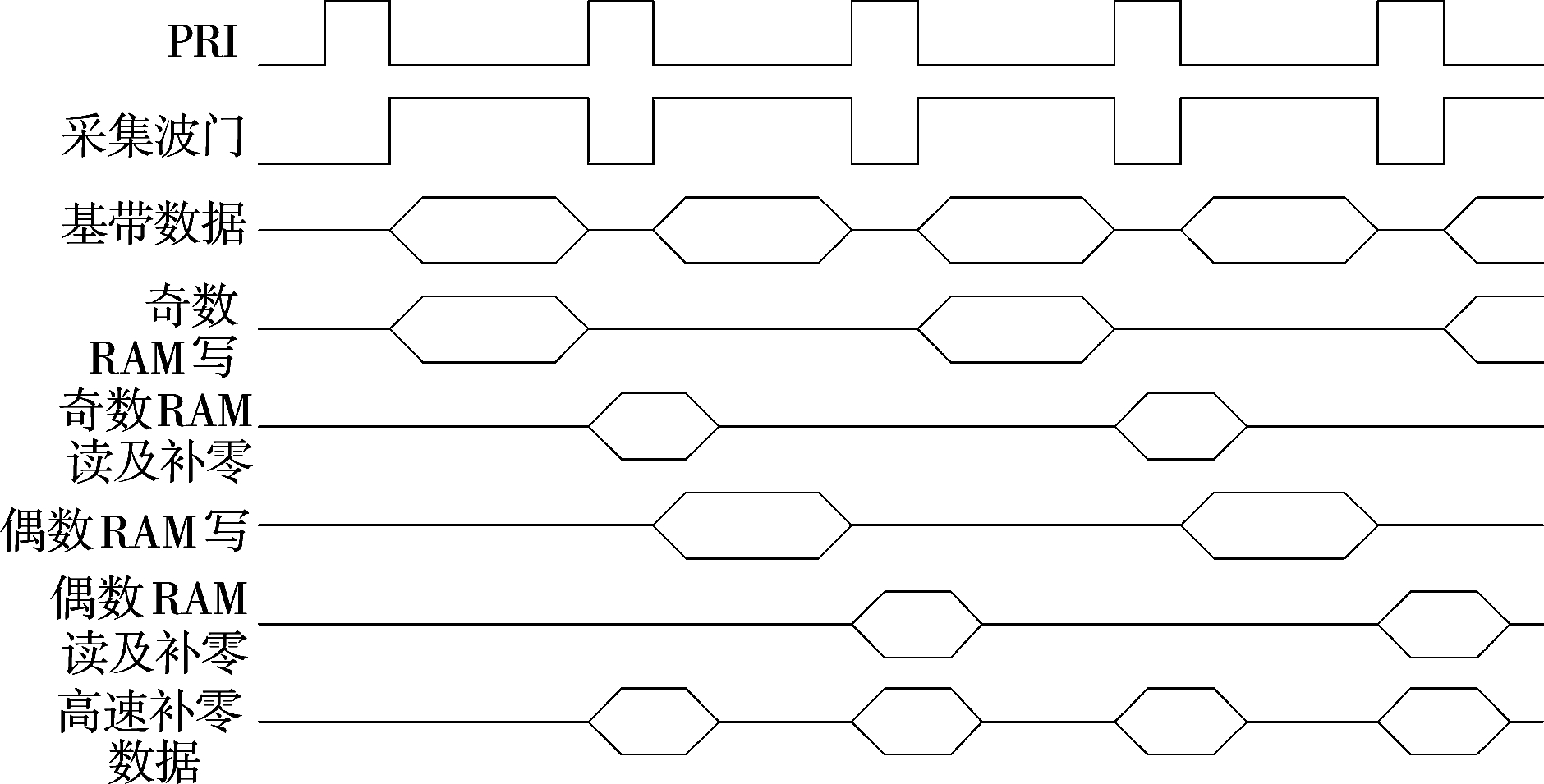

2.2 补零处理

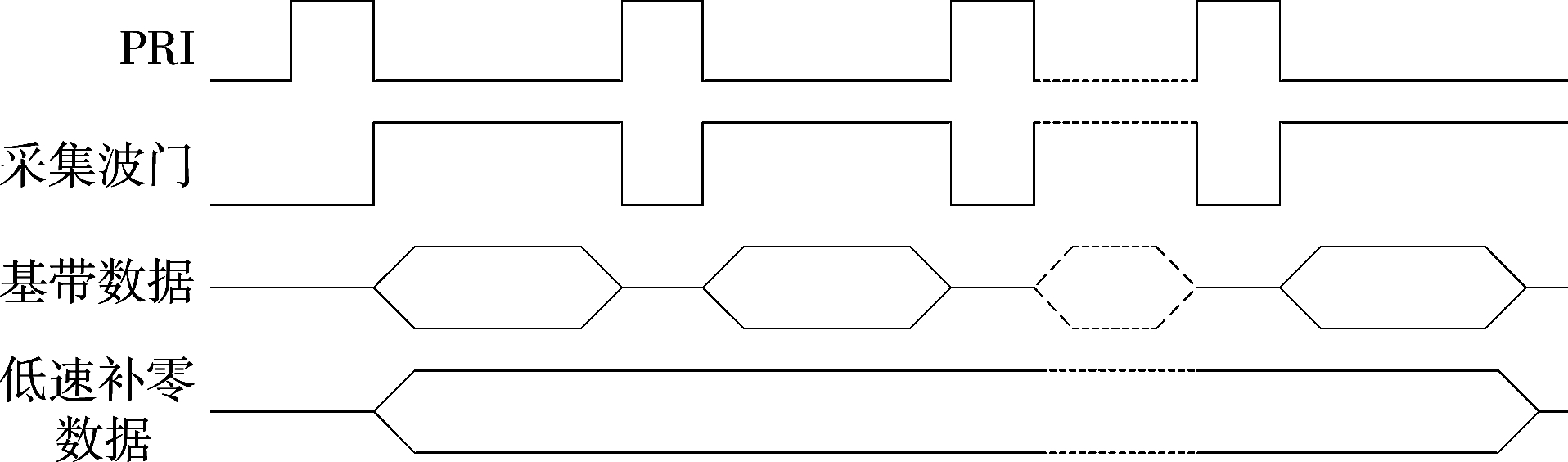

雷达系统通常以PRI为处理单位,线性调频信号的脉压运算每个PRI进行一次,而不同带宽的中频信号经过数字下变频低通滤波及抽取后的数据率也不同,因此每个PRI周期由采集波门脉宽和基带信号数据率来决定处理点数。不过数据采集波门脉宽和数据率计算获得的点数并不一定满足2N,但是FFT和IFFT IP核运算要求的长度必须符合2N,这就涉及数据补零操作,将数据处理长度向上补零至最近的2N。雷达PRI脉冲、数据采集波门脉冲、原始基带处理数据及以基带低速数据率进行补零操作的时序关系如图3所示。

图3 低速率基带数据补零时序

由于窄带系统基带数据率一般只有几兆赫兹、最多十几兆赫兹,同时数据采集波门的占空比又较高,即每个PRI周期内,除了信号发射时间,其余回波信号几乎要全部进行脉压处理。如果采用与基带数据率相同的速率进行补零数据操作,当需要补零较多时,补零后的数据可能与下一个数据采集波门的原始基带数据重合,这样将导致补零数据堵塞和混叠,进而无法完成后续脉压处理。

为解决这种矛盾,并且提高脉压处理效率,需要对原始基带数据提高到高速时钟域处理,即对各种数据率的低速基带信号通过双口随机存储器(Random Access Memory,RAM)提高到统一的高速率数据。高速时钟通常选择最大基带数据率的几倍甚至几十倍,比如200 MHz以上的处理时钟既可以提高基带数据整合效率,又能够保证FPGA逻辑实现的时序要求。

不过虽然采用双时钟域的方式可以解决补零操作数据堵塞和混叠的问题,但是写RAM端的时钟只能是基带数据率的低速时钟,为避免写入RAM的数据无法及时读取而导致数据覆盖,数据整合及补零操作需要采用乒乓结构。奇数序列和偶数序列数据采集波门的基带信号各自独立进行数据低速写入和高速读取处理,然后在高数据率下完成数据补零及奇偶数据组合,使得后续脉压处理在高时钟域内进行。跨时钟域乒乓结构数据补零及整合的时序关系如图4所示。

采用乒乓结构双口RAM数据整合方式[4],用高速时钟将低速基带信号进行速率提升处理,并实现多数据率基带信号的数据整合及补零操作。这种跨时钟域的数据处理方式,将低速基带信号提升至高速时钟域,不仅保障补零数据不会混叠,还能够大大增加待脉压基带数据流的间隔,提高数据处理效率,保障充足的计算时间,为基于FPGA的数字脉压流水运算提供了工程可行性。

图4 高速率乒乓结构数据补零及整合时序

2.3 脉压实现

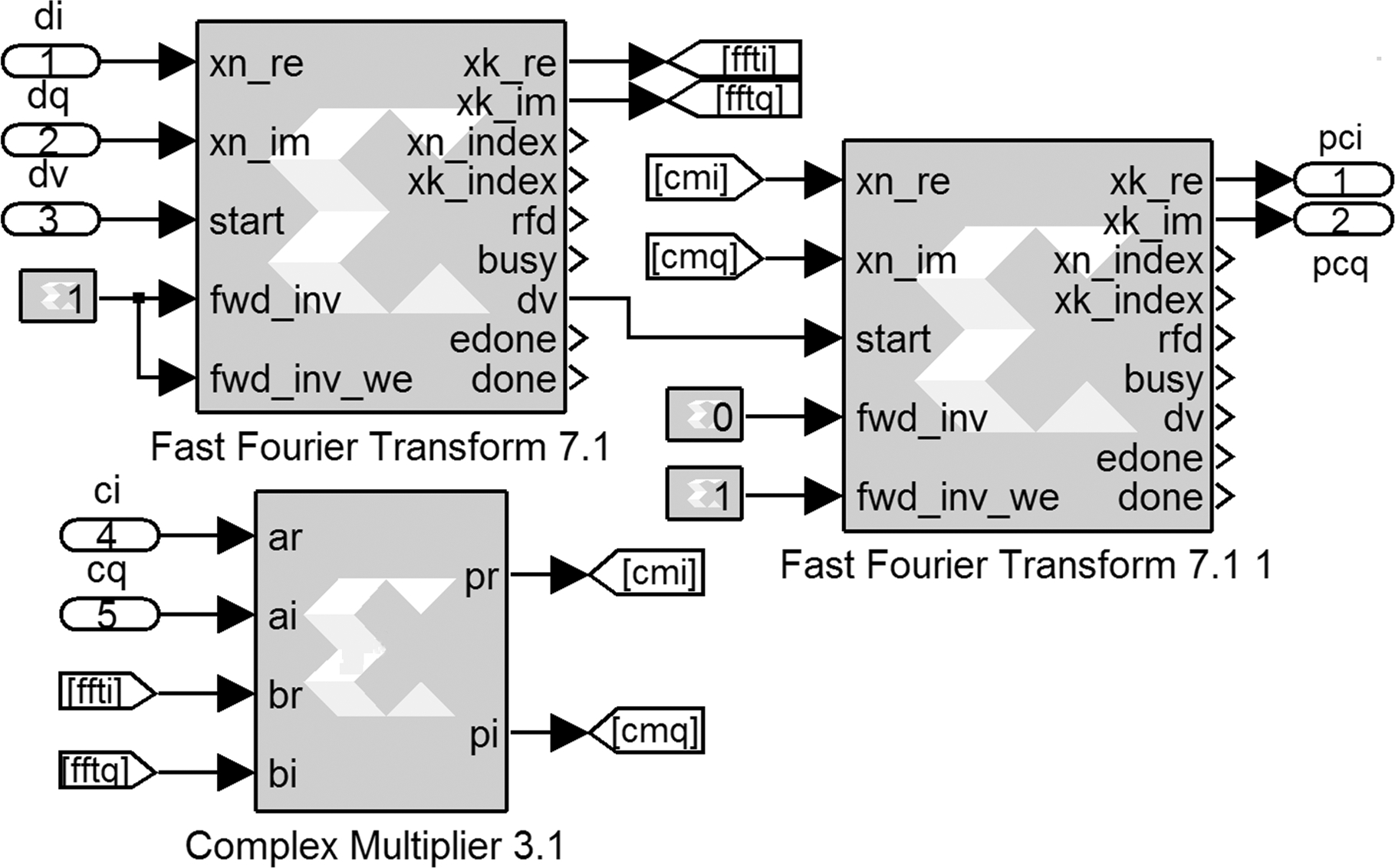

目前主流FPGA芯片公司的应用开发环境都为用户提供了多种IP核,对常用的运算不需要进行复杂的逻辑开发,直接调用相关的IP核即可[5]。例如Xilinx FPGA开发环境提供了脉压主要运算所需的IP核,能够满足雷达窄带接收系统对线性调频信号脉压的处理需求:用于FFT和IFFT运算的Fast Fourier Transform,最大可以支持64 K点计算;用于复数乘法运算的Complex Multiplier,可以实现信号FFT结果与脉压匹配系数的复乘运算。

同时,基于Matlab Simulink与Xilinx System Generator联合开发环境的设计与仿真方法,使得用户能够直接调用界面化的IP核进行工程设计,对FPGA的开发更加直接与简化,适合于大规模、多通道、多带宽窄带数字接收系统的线性调频信号脉压算法设计与实现。本文将主要基于Xilinx FPGA开发环境System Generator中的IP核:用于基带线性调频信号FFT和复乘结果IFFT运算的Fast Fourier Transform 7.1[6],以及用于复数乘法运算的Complex Multiplier 3.1,来实现窄带数字中频接收通道多种运算长度的脉压设计,其中单一计算长度数字脉压的FFT、匹配系数复乘和IFFT三个关键算法实现过程如图5所示。多通道线性调频信号脉压除了匹配系数可以共用外,FFT、匹配系数复乘和IFFT各自独立进行,以确保通道间的运算同步性。

图5 数字脉压实现

基于FPGA的多通道频域方式数字脉压工程实现,除了算法实现的IP核外,关键还在于FPGA各项资源的消耗能否支撑。由于脉压的FFT和IFFT运算占用较多用于数据缓存的Block RAM资源、用于乘加运算的DSP48E1资源,以及用于逻辑运算的Slice资源,因此在实际工程应用时需要对Fast Fourier Transform核进行优化设计,通过设置此IP核的参数使得FPGA内的各种资源能够均衡使用。

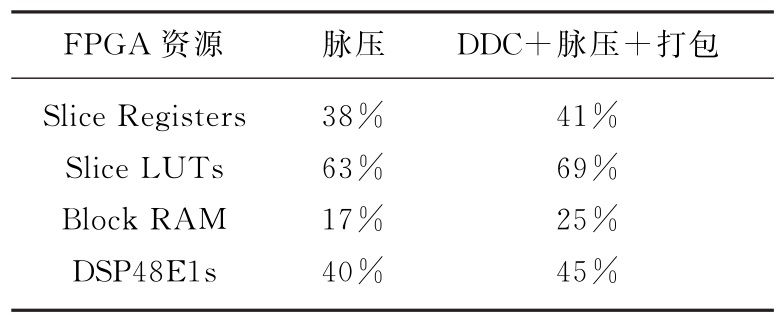

以Xilinx公司资源与性能较优的7系列FPGA XC7VX690T为数字脉压开发平台,窄带4个接收通道32点~4K点共计8种长度的数字脉压算法对FPGA主要资源的使用情况,以及与数字中频接收系统原有的窄带4通道、多带宽、多抽取率DDC和数据打包等功能综合的一体化设计资源占用情况如表1所示。

表1 窄带4通道脉压及综合设计FPGA资源

从表1中FPGA主要资源的使用情况可以看出,能够在单片FPGA内实现窄带4通道数字下变频、数字脉压及数据打包的一体化工程设计。在传统数字接收功能基础上增加数字脉压算法,将有助于提升数字中频接收系统的处理能力,同时可以减轻信号处理系统的数据运算压力,达到雷达接收及处理系统综合优化设计的目的。

3 FPGA仿真

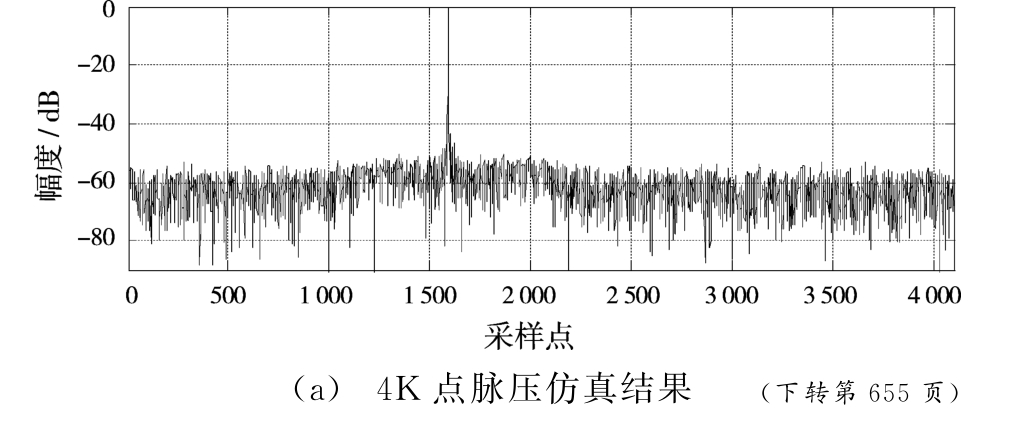

基于FPGA的运算通常以定点为主,这与DSP的浮点运算相比,存在计算精度误差。但是FPGA的定点运算过程能够扩展数据位数,减少对中间计算过程的数据位截取,以尽可能靠近浮点运算的精度。通过对FFT、复乘和IFFT各级运算的数据截位进行合理优化,既能保证FPGA各项资源的均衡使用,又使定点运算精度能够满足雷达系统的应用需求。

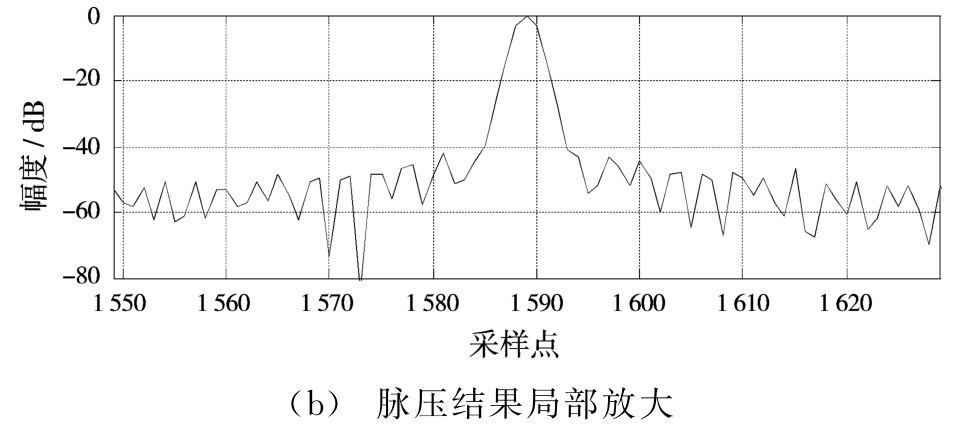

以基带线性调频信号的数据长度4K点进行数字脉压为例,脉压匹配函数加Hamming窗,基于FPGA的窄带线性调频信号数字脉压仿真结果如图6所示。在FPGA开发环境基于IP核的数字脉压仿真获得了很好的效果,能够满足雷达系统对运算精度的要求。

图6 4K点脉压FPGA仿真结果

4 结束语

在数字中频接收系统仅实现ADC采样、数字下变频及数据打包等功能的基础上,增加传统上在处理系统实现的脉压功能。在单片FPGA内实现窄带多通道数字下变频、多长度数字脉压和数据打包的一体化设计,能够有效地提升数字中频接收系统的综合预处理能力。将数字脉压由信号处理系统提前到数字中频接收系统的FPGA中实现,这样有助于减轻信号处理系统的数据处理压力,对优化雷达接收及处理系统的架构均衡设计具有积极作用。

参考文献:

[1]伍小保,王冰,陶玉龙.基于FPGA多通道多带宽多速率DDC设计[J].雷达科学与技术,2016,14(4):403-410.

[2]关涛,朱运航,常文革,等.数字下变频与脉冲压缩系统的设计与实现[J].雷达科学与技术,2010,8(2):133-138.

[3]顾峰,戴健.一种基于FPGA的频域脉冲压缩处理器的实现[J].舰船电子对抗,2016,39(4):105-109.

[4]王利华,胡志东.基于乒乓结构的数据打包技术[J].信息通信,2014(3):20-21.

[5]孙娟,韩涛,李彬,等.基于FPGA IP核的脉冲压缩算法的实现[J].空间电子技术,2015,12(2):63-67.

[6]邢冠培,孟凡利.基于Xilinx FPGA IP核的浮点频域脉冲压缩算法的设计与实现[J].电子测试,2015(15):28-30.