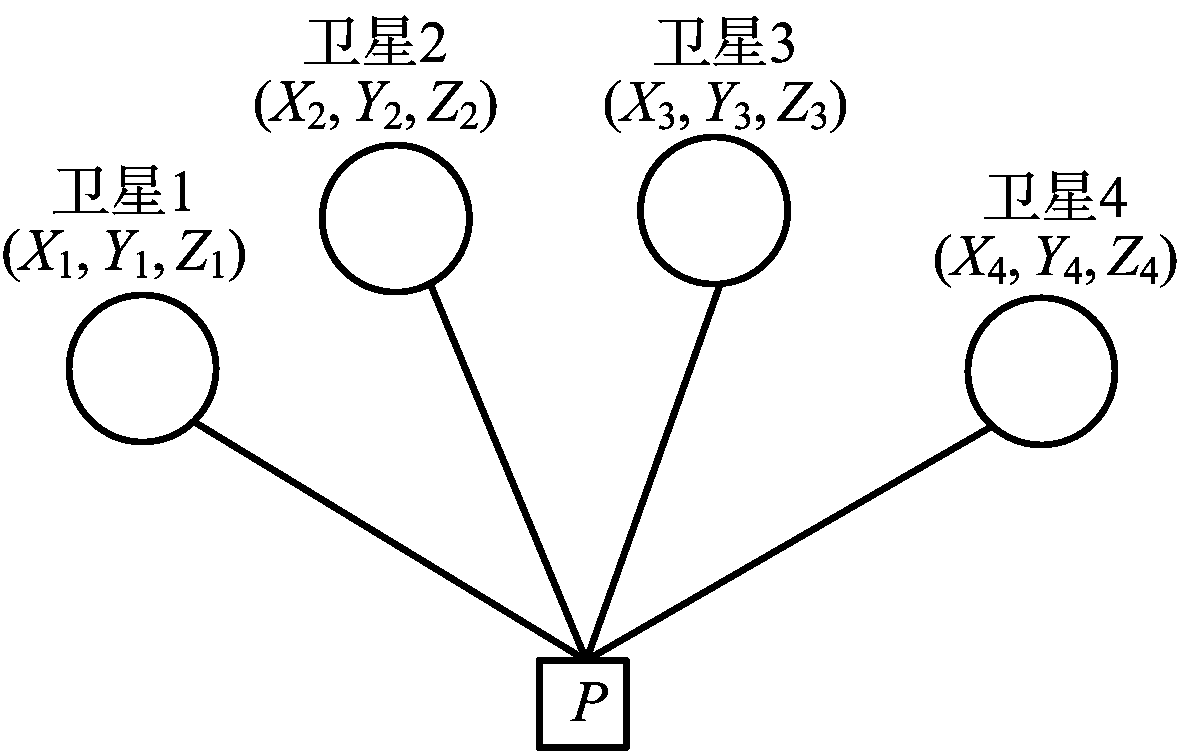

图1 GPS定位原理

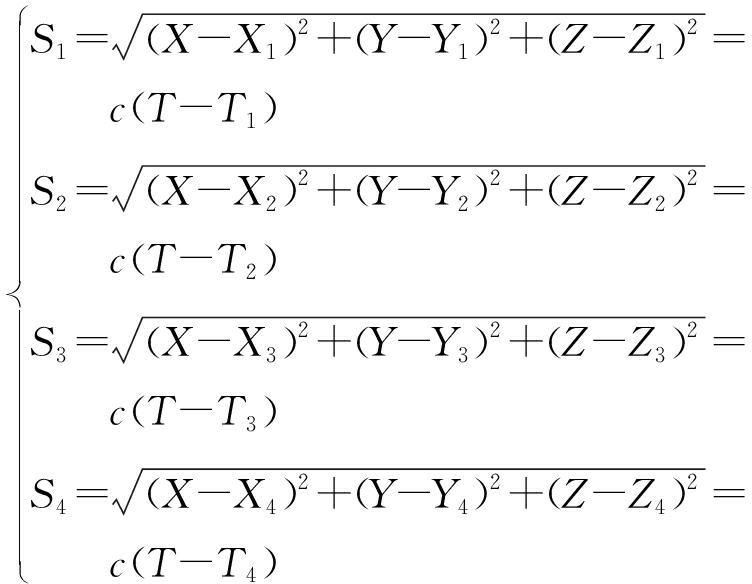

现代地空导弹系统都是由指挥控制车、雷达、导弹发射车及相关配套设备组成,雷达按作战任务分为搜索雷达和跟踪制导雷达(简称制导雷达)。搜索雷达对指定空域或360°全方位扫描,将截获的飞行目标参数报送指挥控制车(简称指控车),指控车对疑似目标进行威胁等级评估,将预打击目标的方位、高度、速度、航向等参数送制导雷达,引导制导雷达天线对准目标来袭空域,待目标进入制导雷达作战威力范围内,制导雷达开始对目标进行精确跟踪,并将目标的详细参数报送指控车,指控车依据来袭目标的详细参数进行火力单元(即导弹发射车)分配,指挥导弹发射,对来袭目标进行拦截。目标情报在导弹系统内的传递以及作战控制指令的响应要求具有严格的时效性,这就需要为地空导弹系统各单元建立统一的时间基准,使各单元间时间同步。基于地空导弹系统各单元机动性配置的要求,利用北斗、GPS进行系统的时间统一是一个理想解决方案,能很好地保证各单元间时间同步的准确性[1-2]。雷达情报处理一般要求时间准确度控制在μs级。北斗、GPS的授时精度一般在1 000 ns以内,北斗二代系统能达到50 ns以内,满足系统情报处理要求。

GPS定位和授时主要采用测距法,即利用4颗卫星同时进行距离测量,并解算出目标的位置,其原理如图1所示。

图1 GPS定位原理

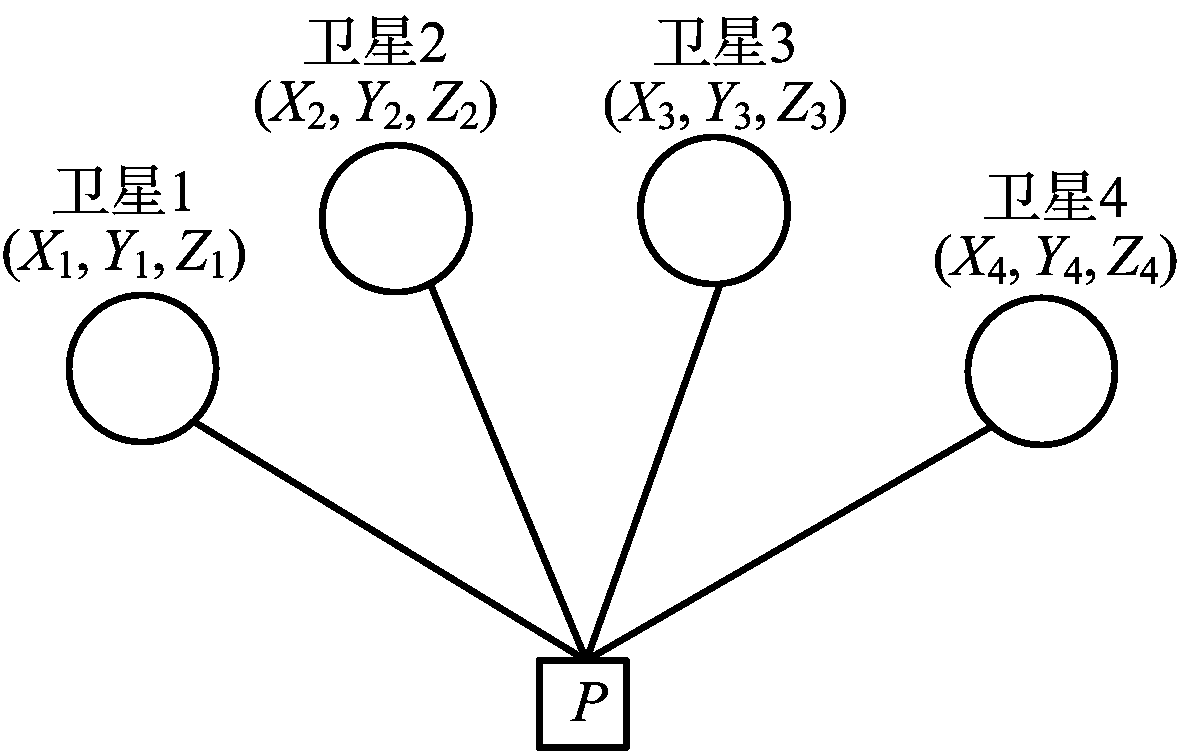

设T时刻在目标位置P处用接收机同时测得4颗卫星1, 2, 3, 4到P点处的距离分别为S1,S2,S3,S4,4颗卫星的坐标分别是(Xi,Yi,Zi),i=1, 2, 3, 4,则P点的坐标和时间T可通过式(1)解算得出:

(1)

式中,Ti(i=1, 2, 3, 4)为各卫星的时间,T为用户接收机的时间,c为光速,(X,Y,Z)为用户接收机的坐标。各卫星的时间Ti和坐标(Xi,Yi,Zi)通过解析接收到的卫星报文获得[3-4]。

北斗卫星导航系统已发展至第三代,具备卫星无线电测定系统(Radio Determination Satellite System, RDSS)和卫星无线电导航系统(Radio Navigation Satellite System, RNSS)两种模式。RDSS模式采用主动定位方式,即先由用户接收机主动发出定位请求(通过卫星转发),北斗系统的地面控制中心进行相应解算后,下发定位信息和授时数据。RNSS模式采用无源定位方式,通过地面运控系统监测整个导航系统的卫星位置并同步卫星时钟,该模式与GPS系统的原理相同[5-6]。授时精度上,北斗一代是100 ns,二代是50 ns,三代可达20 ns。

某型地空导弹系统组成如图2所示,各单元采用相同的时间同步设计,下面以在搜索雷达中的设计、应用为例进行介绍。

图2 地空导弹系统组成示意图

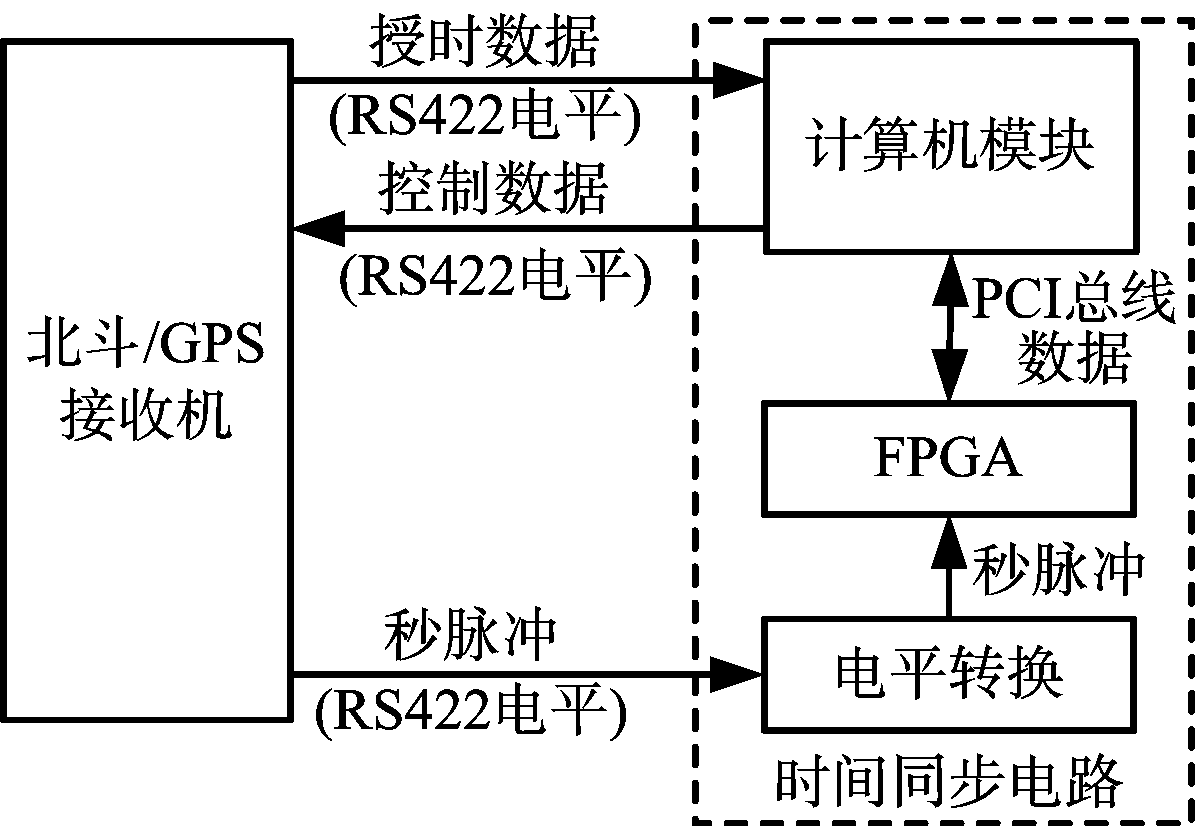

北斗/GPS接收机接收卫星信号,通过串口或网络以固定重复频率输出授时数据,包含年、月、日、时、分、秒信息,同时以电信号的方式每秒输出一个秒脉冲[7]。搜索雷达的时间同步电路由计算机模块、FPGA电路和电平转换电路组成,与北斗/GPS接收机间接口如图3所示。计算机模块实现授时数据接收解析、对时控制管理、相对时间读取、实时时间产生与分发功能;FPGA电路实现秒脉冲接收、计数、相对时间产生、秒脉冲软件抗干扰保护等功能;电平转换电路实现秒脉冲信号从RS422电平到TTL电平的转换功能。

图3 授时数据及秒脉冲接口示意图

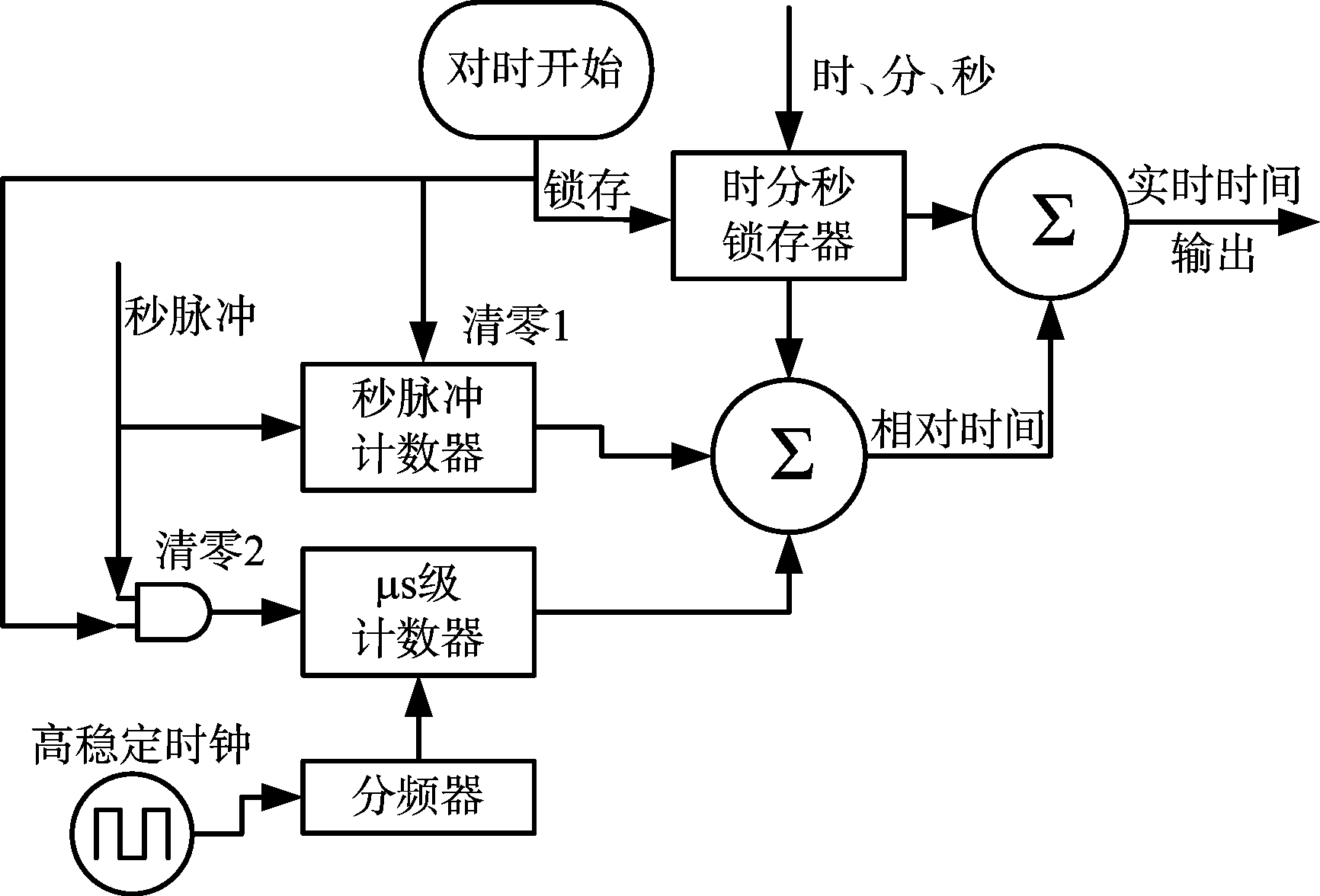

FPGA电路接收雷达系统的高稳定、高精度时钟信号,利用其内部锁相环分频产生满足时间分辨率要求(一般取μs级)的内部计数用时钟信号,在计算机模块下发对时开始时刻,该计数器从零开始计数。对于对时开始时刻,设相对时间为零,则该计数器的实时计数值即是相对于对时开始时刻的实时相对时间。如图3所示,计算机模块通过PCI总线读取FPGA电路计数产生的实时相对时间,与对时开始时刻的绝对时间累加,即是系统的实时时间。对时开始时刻的绝对时间由计算机模块通过解析串口或网络接收的授时数据报文获得。设计采用FPGA接收20 MHz的雷达系统时钟。

为方便设计实现,具体工程设计上,将上述相对时间的统计分成两部分,即以秒为量级对秒脉冲的计数累加和以μs为量级对分频得到的内部计数用时钟脉冲的计数累加,两者之和为相对时间。如图4所示,用于雷达情报处理用的实时时间由3部分组成:解析授时数据得到的对时开始时刻的绝对时间、秒脉冲的累加计数值、μs级计数器值。三者累加即构成了系统的实时时间。

图4 实时时间产生原理框图

如图4所示,秒脉冲进入FPGA后有两个处理:一是对秒脉冲进行计数累加处理,二是用秒脉冲的前沿对μs级时钟计数器做清零操作。

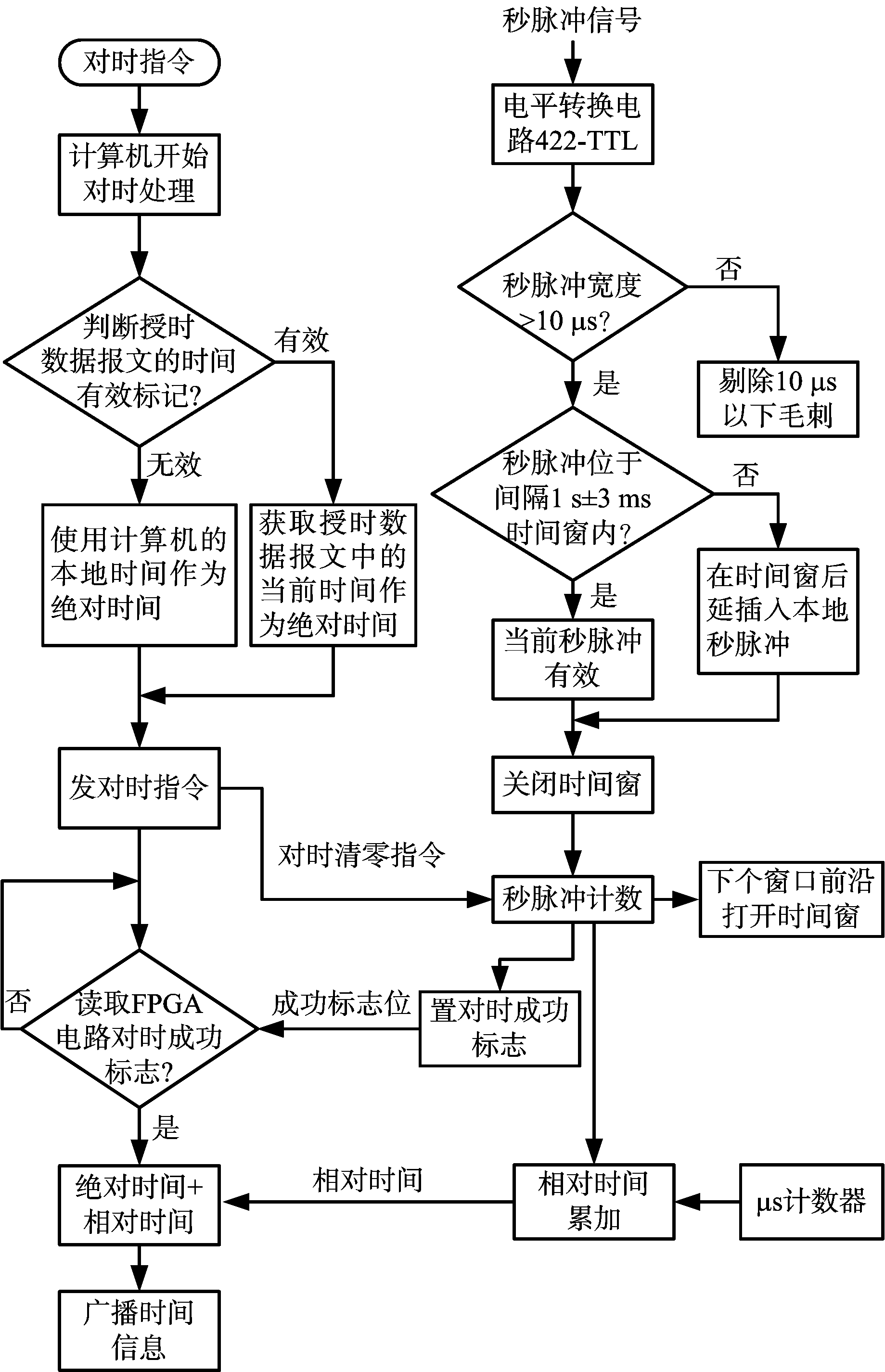

在计算机模块发出对时指令后,FPGA电路通过其内部计数操作产生实时的相对时间,计算机模块读取该相对时间,并与对时开始时刻的绝对时间相加,即获得实时的系统时间。详细处理流程如图5所示。

图5 时间同步处理流程图

基于上述原理分析,地空导弹系统各单元的时间均同步于北斗/GPS时间,在采用相同的时间同步设计且受控于统一的对时指令控制下,地空导弹系统各单元间的时间可以保证统一和同步。

如图3所示,时间同步电路从北斗/GPS接收机接收两路信号,分别是串口(或网络)数据信号以及秒脉冲信号。鉴于雷达系统内部电磁环境复杂,存在高电压、大电流设备,会对授时数据信号和秒脉冲信号的传输产生干扰。工程设计上,分别从硬件和软件两方面采取措施,避免和滤除干扰,对授时数据和秒脉冲信号加以保护。

2.2.1 硬件措施

形成电磁干扰的基本要素分别是干扰源、传播路径和敏感器件,抗干扰设计就是要针对这3个要素分别采取防范措施,切断或降低干扰信号对接收端敏感器件的影响[8]。鉴于干扰源无法彻底杜绝,时间同步电路的抗干扰设计重点是对信号传输过程的保护和选用抗干扰能力强的器件。

信号传输过程中的干扰引入有传导和辐射两个途径。干扰的传导引入主要是通过供电回路,采用与干扰源分开供电、二次供电等措施可有效隔离干扰的传导引入。干扰的辐射引入是干扰源向空间辐射的电磁信号在传输导体及处理器件中感应出干扰信号,对有用信号形成干扰。辐射干扰在线缆的各芯线中感应生成的信号幅度和极性均相同,利用差分放大电路,即可去除辐射干扰信号。信号传输采用差分传输方式是抗辐射干扰的有效措施。抗辐射干扰的另一重要措施是采用有屏蔽层保护的传输线缆。

针对信号接收处理器件的抗干扰设计,重点是选用内部带隔离电路的器件。

设计中综合运用上述各种抗干扰措施,信号传输采用RS422电平标准,以正/负差分信号的形式传输,可有效抗辐射干扰,具有抗干扰能力强、驱动距离远的优点,结合常规的EMC设计,包括阻抗匹配、电源滤波、正确的接地处理、尽可能远离干扰源布线等,保证了硬件抗干扰措施的有效性。

2.2.2 软件措施

鉴于干扰信号产生的原因错综复杂,且具有很大的随机性,单纯的硬件抗干扰措施很难保证信号传输、接收完全不受干扰,因此设计了必要的软件抗干扰措施。

时间同步电路接收北斗/GPS接收机的授时数据和秒脉冲信号,其中授时数据接口是串口或网络,由计算机读入并解析出年、月、日、时、分、秒信息,在数据协议层定义有数据校验措施和固定周期发送机制,可保证授时数据的正确接收与解析。

对于秒脉冲信号,一般脉宽1~2 ms,相对于 1 s的重复周期,其占空比是很低的,极易受到干扰。在数字电路设计中,对于脉冲信号的采样,脉冲宽度的判宽滤波是常见的软件抗干扰措施,即用较高的采样时钟连续对输入脉冲信号进行采样,如果连续N个采样值都有效,则判断该输入脉冲有效,否则认定为干扰脉冲,作滤除处理。N值的设定依据工作现场的实际电磁干扰情况,原则是N次连续采样的时间宽度应该小于输入脉冲信号的宽度。针对秒脉冲的软件抗干扰保护,在FPGA固件设计中,采用了上述的判宽滤波处理,设计的采样时钟是10 MHz,N取值100,对脉宽在10 μs以下的输入脉冲认定为干扰脉冲,作滤除处理。

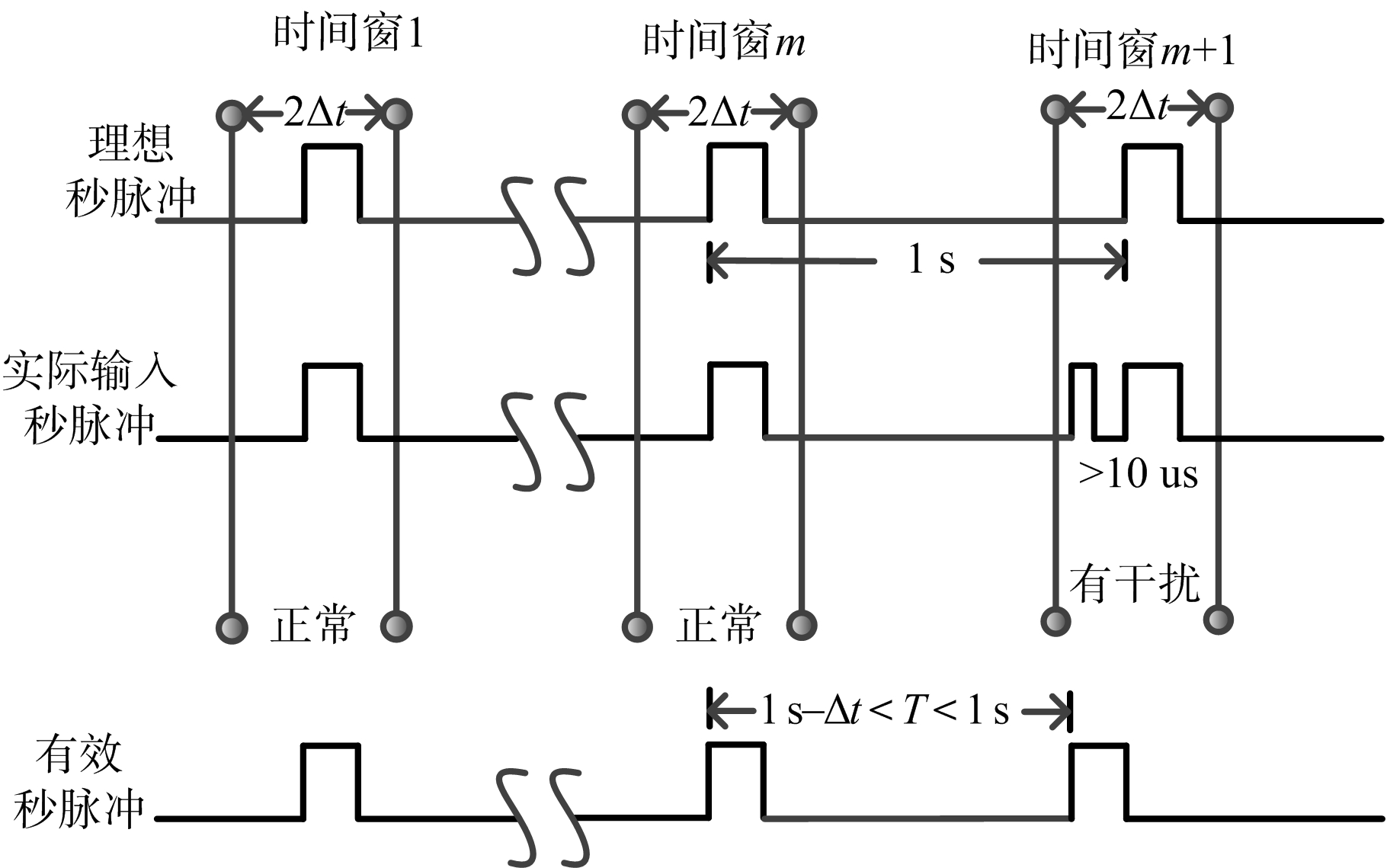

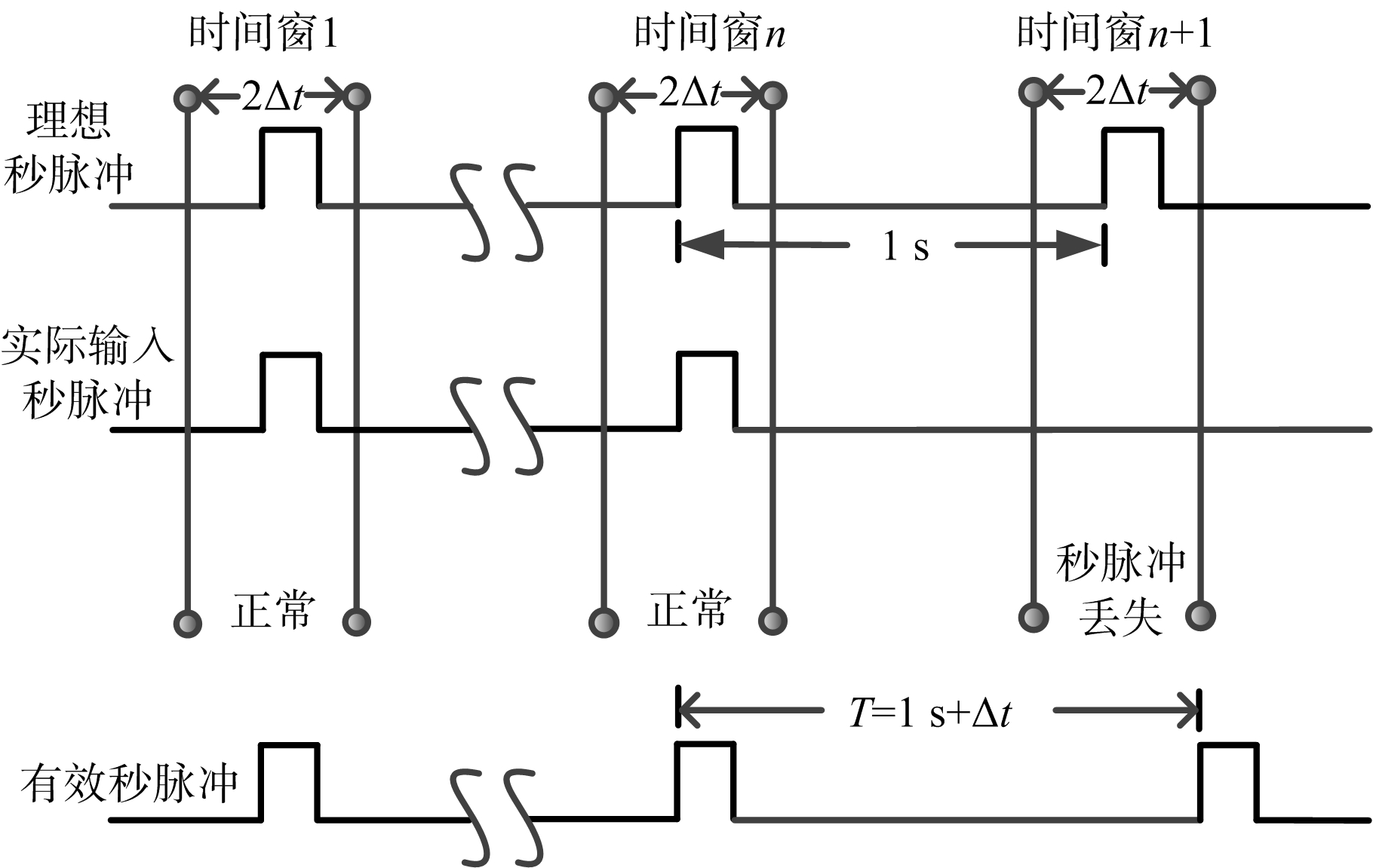

在判宽滤波处理的基础上,针对秒脉冲极低占空比的特点,在FPGA固件设计中,首次提出了秒脉冲时间轴开窗保护机制,其设计思想是:以当前秒脉冲在时间轴上位置预计下一个秒脉冲出现的时刻,以这个预计的时刻为中心在时间轴上开一个窗,窗外的任何输入脉冲都将被认定为干扰脉冲,作滤除处理,仅窗内的第一个脉冲被认定为有效秒脉冲输入。

秒脉冲时间轴开窗保护的具体设计如下:对输入的秒脉冲,先是滤除脉冲宽度在10 μs以下的干扰脉冲,然后以滤波后的第1个有效秒脉冲开始,在当前秒脉冲的前沿开始计时,到达1 s-Δt时刻,打开时间窗,时间窗宽度2Δt,在这个时间窗内出现的首个脉冲确定为有效秒脉冲,秒脉冲计数器加1,然后关闭时间窗;如果整个2Δt时间窗内都没有脉冲输入,则在时间窗的后沿插入一个脉冲,作为有效秒脉冲,秒脉冲计数器加1,关闭时间窗。再以当前有效秒脉冲的前沿开始计时,在时间轴上相应时刻打开第2个时间窗,输出或插入有效秒脉冲,秒脉冲计数器加1,关闭时间窗。如此循环处理,即实现了对输入秒脉冲的时间轴开窗保护。需要注意的是,如果当前时间窗内没有脉冲输入,则下一个时间窗的打开时刻是在当前插入的有效脉冲前沿滞后1 s-2Δt时刻。

图6、图7是秒脉冲时间轴开窗保护示意图。图中,Δt为系统允许的秒脉冲周期误差,设计取值3 ms。

图6 秒脉冲时间轴开窗保护示意图(时间窗内有干扰脉冲)

图7 秒脉冲时间轴开窗保护示意图(输入秒脉冲丢失)

通过秒脉冲时间轴开窗保护,可有效滤除时间窗外干扰脉冲,因为窗口关闭,判断输入脉冲是否有效、秒脉冲计数器计数等操作都被屏蔽,杜绝了此类干扰的影响。理论上还存在一种可能,即系统在工作过程中,因某种原因造成秒脉冲输入中断,按照秒脉冲时间轴开窗保护的工作原理,时间同步电路仍可正常守时,以保证导弹系统作战任务的完成。

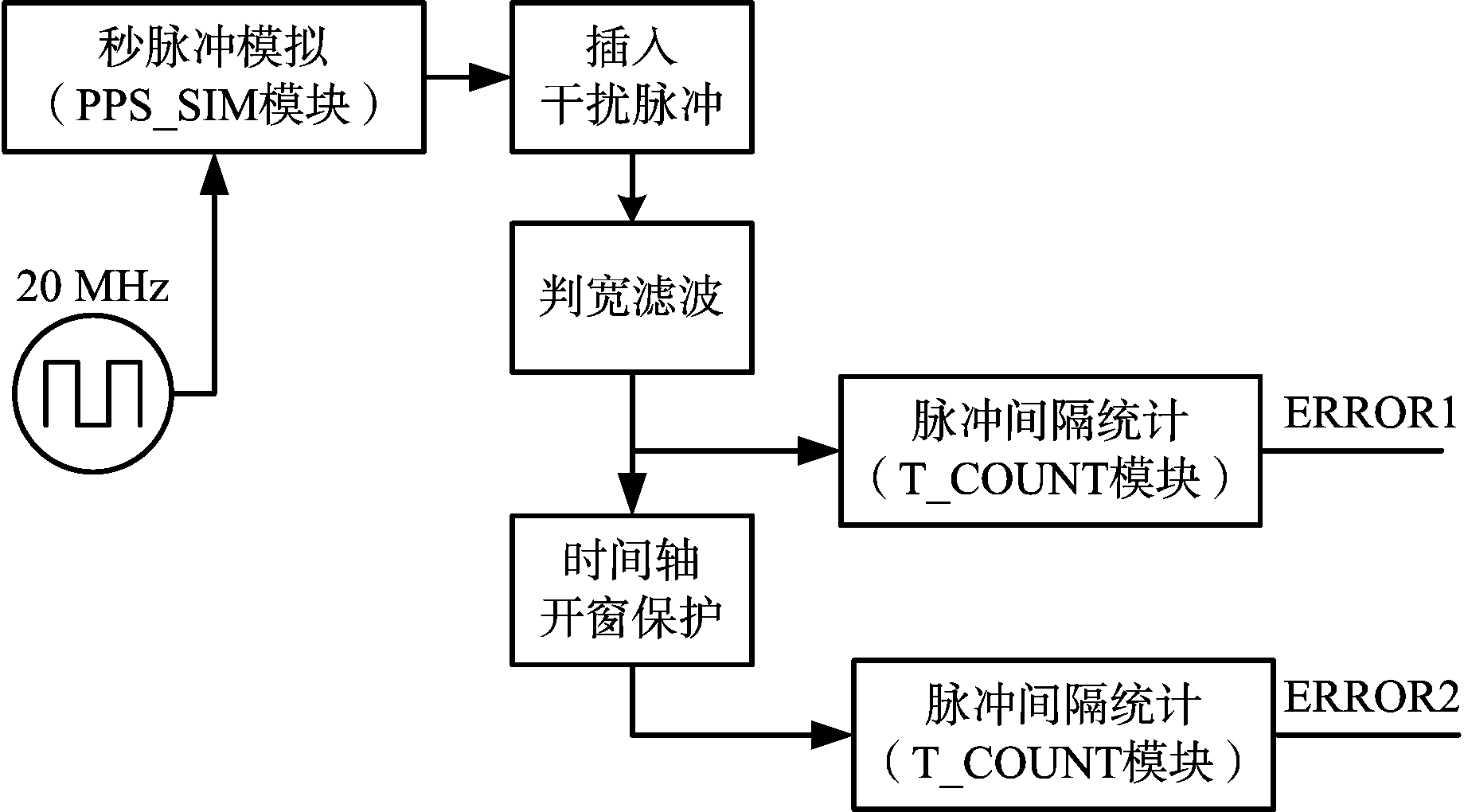

秒脉冲时间轴开窗保护属新设计,为验证其有效性,编写了秒脉冲模拟发生模块PPS_SIM,用内部的20 MHz时钟去计数产生模拟秒脉冲,并在模拟的相邻秒脉冲间随机加入模拟干扰脉冲;编写了相邻脉冲间隔时间统计模块T_COUNT,若相邻脉冲间隔时间不在1 s±3 ms以内,则错误计数器ERROR加1,计算机模块定时读取ERROR值,写入文件备查。用PPS_SIM模块输出的加有模拟干扰的秒脉冲模拟信号替代实际输入的秒脉冲信号,用T_COUNT模块分别检测统计PPS_SIM模块的输出和经过时间轴开窗保护处理后的输出(即有效秒脉冲),重新编译工程文件并加载FPGA,运行,查阅记录文件,发现统计PPS_SIM模块输出的错误计数值ERROR1一直在累加,统计经过时间轴开窗保护处理后输出的错误计数值ERROR2一直是0,证明时间轴开窗保护是有效的。

仿真验证的流程图如图8所示。

图8 开窗保护仿真验证流程图

对于时间同步的硬件电路设计,电平转换电路采用AD公司的ADM2582E芯片实现RS422电平到TTL电平的转换,该芯片内部集成有收、发电路各1个通道,特点是RS422端的电源、信号、地与TTL端的电源、信号、地是隔离的,采用单电源供电,内部集成隔离式DC-DC电源。FPGA采用Altera公司的产品,固件代码用Verilog HDL语言编写。计算机采用国产龙芯3A计算机模块,与FPGA间通过PCI总线实现数据交互。

实际应用发现,秒脉冲在传输过程中更易受周边复杂电磁环境影响而引入干扰,单纯的硬件保护不能彻底杜绝干扰。在某型地空导弹系统联试初期,FPGA固件未设计对秒脉冲的时间轴开窗保护处理,曾发生过秒脉冲跳秒现象,某时刻本应只增加1 s,实际秒脉冲计数器增加了2 s,造成从这一时刻开始,所有的计时都与标准时间差1 s,与导弹系统其他单元的时间也就差了1 s,破坏了导弹系统各单元时间的统一性,严重影响作战任务的执行。故障排查阶段,用示波器检测输入的秒脉冲信号,未发现异常,秒脉冲信号的脉冲宽度、周期都在指标范围内,判定为外部偶发干扰引起。在确认设计的各项硬件抗干扰措施均有效作用的情况下,在FPGA固件中增加对秒脉冲时间轴开窗保护处理,经过近一年时间的联试、验证,秒脉冲跳秒现象未再发生,时间同步电路工作一直正常。

武器系统的各组成单元(指控车、雷达、导弹发射车等)使用高稳定的晶振作为本地时钟源,利用北斗、GPS秒脉冲来同步这个本地时钟,实现了整个武器系统的时间统一和同步。文中所述同步设计有借鉴意义,可推广应用至对时间有同步要求的系统和设备。所述抗干扰措施,在工程设计中具有普遍参考价值,其中首次应用的秒脉冲时间轴开窗保护具有很强的针对性,有效地解决了秒脉冲抗干扰保护,拟推广应用于新型号雷达的时间同步设计。

[1] 王凌. 时间基准及其在雷达装备中的应用要求[J]. 雷达与对抗, 2014, 34(4):13-15.

[2] 郝士林,严超,毕进. 武器系统基于GPS时间同步方法研究[J]. 火控雷达技术, 2017, 46(3):1-5.

[3] 宋洪良,唐小明. 雷达同步信号参数提取及重构技术[J]. 电光与控制, 2017, 24(8):71-75.

[4] VYSKOCIL P, SEBESTA J. Relative Timing Characteristics of GPS Timing Modules for Time Synchronization Application[C]∥ International Workshop on Satellite and Space Communications, Tuscany, Italy: IEEE, 2009:230-234.

[5] 邹绪平,王相军. 北斗二代卫星导航系统定位优化仿真研究[J]. 计算机仿真, 2017, 34(6):80-83.

[6] 赵东艳,原义栋,石磊,等. 用于智能电网建设的北斗/GPS高精度授时方案关键技术[J]. 电网技术, 2013, 37(9):2621-2625.

[7] 刘爱东,李知宇,王丰,等. 基于GPS授时同步的标校系统嵌入式设计[J]. 电子设计工程, 2018, 26(7):55-58.

[8] 周琴. 数字电子系统抗干扰分析与设计[D]. 合肥: 合肥工业大学, 2009.