图1 PLL合成频率源的原理图

汽车防撞雷达可大幅降低交通事故的发生率,具有广阔的应用前景,因而备受世界各国的关注。而防撞雷达系统中频率源的参数直接影响到雷达的可靠性和测距测速的性能,所以频率源也成为整个汽车防撞雷达系统设计中的重要部分。目前,实现频率源常用的技术主要有两类,一类是基于直接数字频率综合(Direct Digital Synthesizer,DDS)技术以及DDS组合方式的技术;另一类是锁相环(Phase-Locked Loop,PLL)合成频率技术。前者虽然频率转换较快且频率分辨率高,但由于受到数字集成电路速度和奈奎斯特原理的限制,其输出信号上限频率不高,且DDS组合方式结构复杂[1-3],输出信号频谱的杂散难以抑制。后者由于锁相环路对输入信号含有的噪声和环路内部的噪声具有过滤作用,因此输出信号的相位噪声低,这使得它在低噪声合成频率中得到广泛应用。此外,PLL合成频率源电路相对简单,具有输出频率范围宽、寄生频率抑制性能良好、频谱纯度高和输出频率易程控等优点[4-6]。本文的频率源采用PLL合成频率技术。

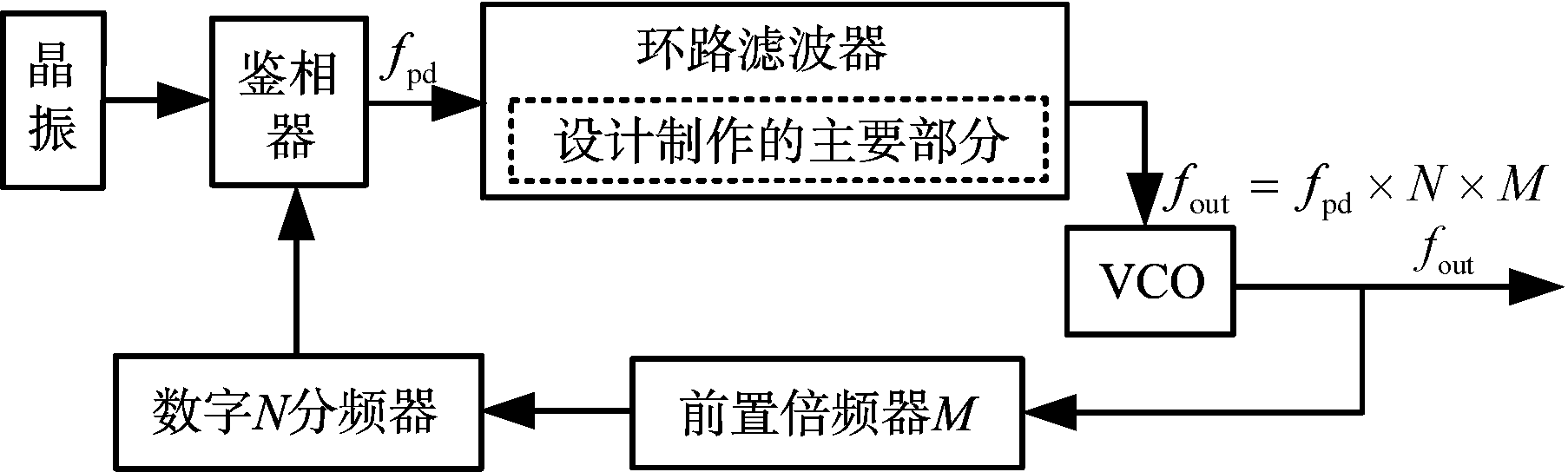

PLL电路是一个相位负反馈环路,由鉴相器、环路滤波器和压控振荡器(VCO)组成,它将输入信号与VCO输出信号的相位进行比较,控制两个信号使其保持同相位。若在PLL输入信号中加上由晶振等产生稳定的频率信号,在VCO输出与鉴相器输入之间接入分频器,通过切换分频器的频率,便得到VCO的输出与输入频率同样精度的分频信号[7]。这就是PLL合成频率源的工作原理,如图1所示。

图1 PLL合成频率源的原理图

在PLL合成频率源的设计中,为得到高精度的输出信号,一般由高精度的有源温补晶振提供高稳定性的输入信号。若在VCO与数字N分频器之间接入前置倍频器,PLL合成频率源的输出频率便可达到GHz数量级。

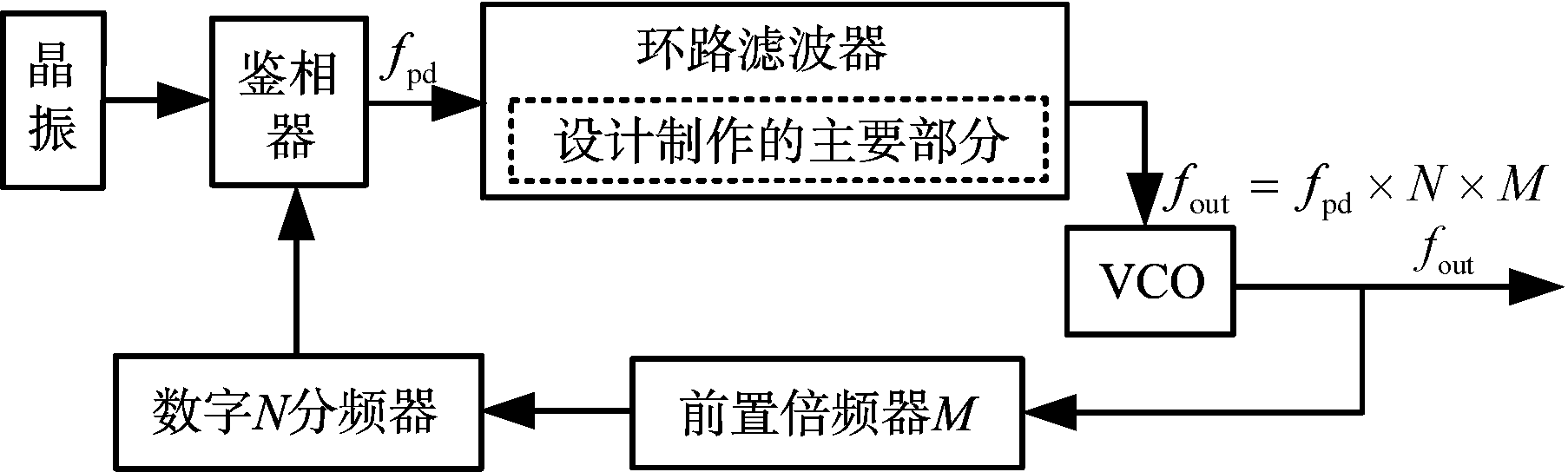

相位噪声是PLL合成频率源衡量其频谱纯度的重要参量。PLL合成频率源的噪声主要来源于4个部分,分别是参考信号源、鉴相器、VCO以及数字N分频器,图2为PLL合成频率源的相位噪声模型。其中,Kd为鉴相器的增益,Kv为压控灵敏度,θnr,θnd,θnv,θnn,θno分别为参考信号源、鉴相器、VCO、数字N分频器和PLL合成频率源输出信号的相位噪声。

图2 PLL合成频率源的相位噪声模型

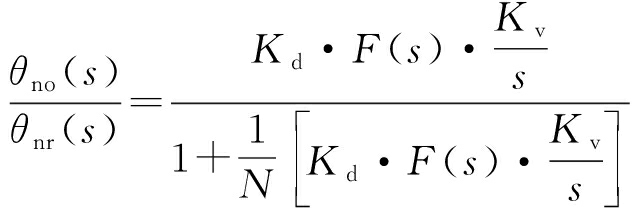

根据经典闭环系统控制理论,采用系统线性分析方法,以参考信号源引入的相位噪声为例,结合图2的相位噪声模型计算分析各噪声源的相位传递函数。假定此时系统中的相位噪声仅有参考信号源的输入引起,其他噪声源均为零输入,则由系统相位噪声模型框图,可得

![]()

(1)

整理可得

(2)

令![]() 则由参考信号源引入的相位噪声的传递函数为

则由参考信号源引入的相位噪声的传递函数为

(3)

同理,由鉴相器引入的相位噪声的传递函数为

(4)

由N分频器引入的相位噪声的传递函数为

![]()

(5)

由VCO引入的相位噪声的传递函数为

![]()

(6)

在PLL电路中,由环路滤波器的传递函数F(s)呈低通特性可知,开环传递函数G(s)呈低通特性,闭环传递函数G(s)/[1+H·G(s)]也呈低通特性,所以由参考信号源、鉴相器和N分频器引入的相位噪声的传递函数均呈低通特性,而由VCO引入的相位噪声的传递函数呈高通特性。也就是说,PLL合成频率源环路的带内相位噪声由参考信号源、鉴相器和N分频器决定,而环路的带外相位噪声则是由VCO决定。由此可知,为使PLL合成频率源的相位噪声性能达到最优,环路带宽的恰当选取便显得至关重要。

根据24 GHz汽车防撞雷达的要求,本设计的PLL合成频率源的输出频率为24~24.25 GHz,相位噪声优于-85 dBc/Hz@1 kHz。为使该频率源满足设计指标,首先进行器件的选型与评估。这里选择相位噪底低的鉴相芯片ADF4159[8]和24 GHz VCO芯片HMC533[9]。在工程上,通常使用式(7)估算PLL环路的带内相位噪声:

PNTOTAL=PNSYNTH+10lg(FPFD)+20lgN

(7)

由N=FVCO16/FPFD知,则式(7)又可写为

PNTOTAL=PNSYNTH-10lg(FPFD)+20lgFVCO16

(8)

式中,PNTOTAL为整个PLL的相位噪声,PNSYNTH为鉴相芯片归一化的相位噪底,FPFD为鉴相频率,FVCO16为VCO十六分频端口的输出频率,N为分频系数。

本设计中,鉴相频率为100 MHz,VCO输出的中心频率为24.125 GHz,ADF4159在小数模式下的相位噪底为-217 dBc/Hz,根据式(8),可估算出由VCO十六分频反馈至PLL环路的带内相位噪声:

PNTOTAL=-217-10lg(100×106)+

20lg(24.125/16×109)=

-113.43 dBc/Hz

频率源在输出频率24.125 GHz处,此相位噪声会恶化24 dB,最终相位噪声为-89.43 dBc/Hz,可见估算的相位噪声值高于设计要求值,表明本设计选用的芯片组合方案满足汽车防撞雷达频率源的指标要求。

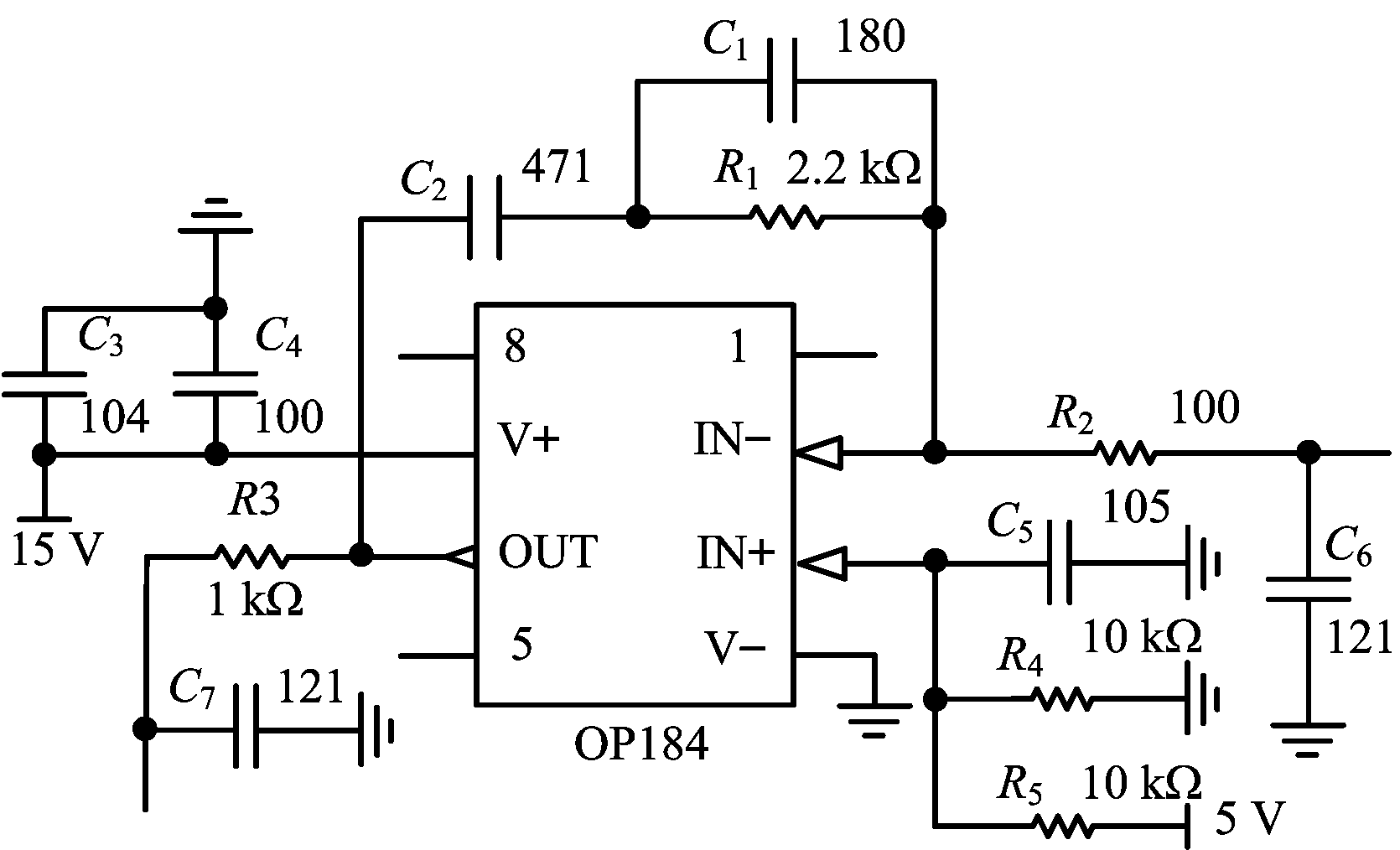

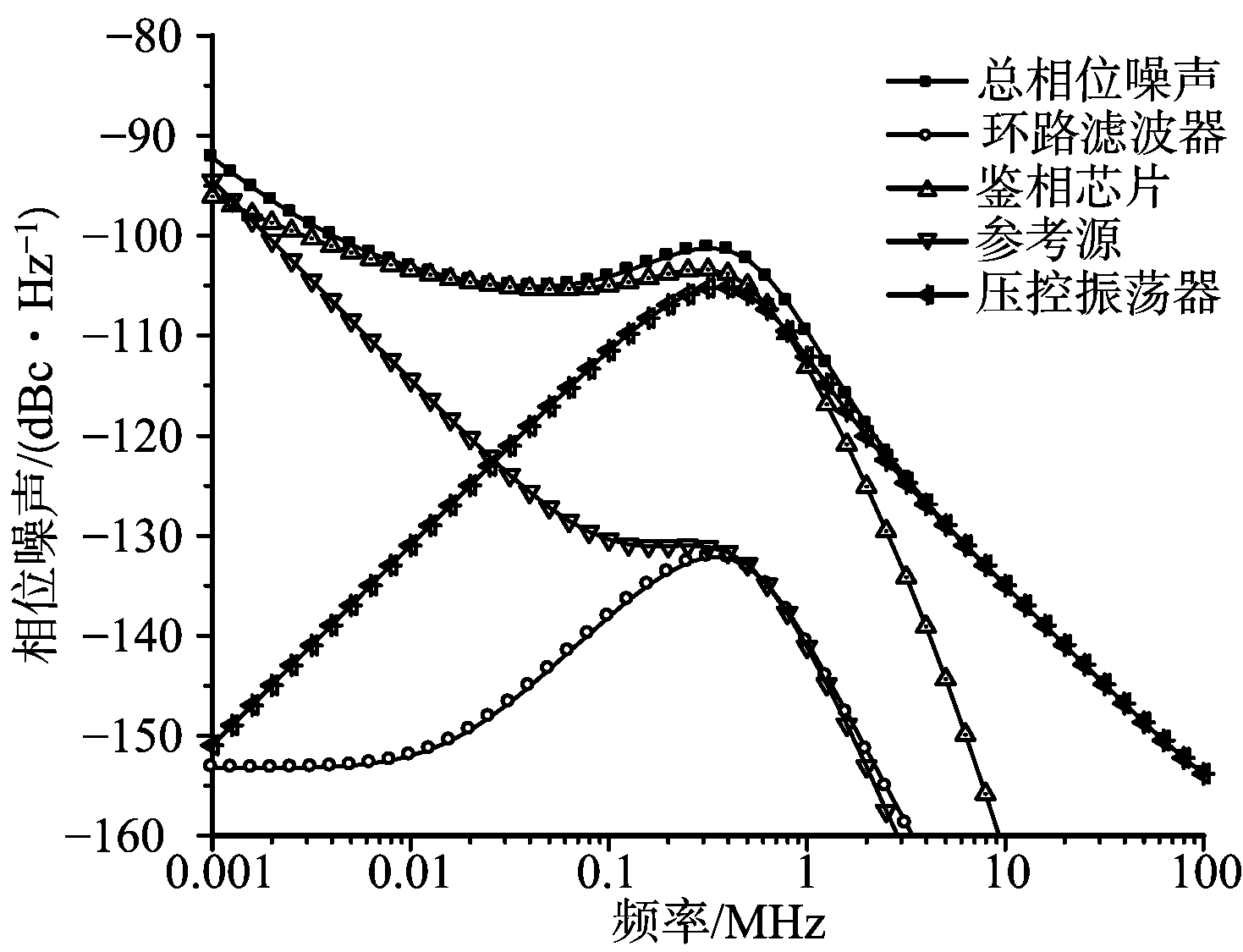

根据第2节分析,环路带宽的选取对维持环路稳定性和控制环路带内外噪声起着重要作用。选取环路带宽可借助ADIsimPLL4.10软件,通过该软件调整环路带宽以完成环路滤波器的设计,并使其满足汽车防撞雷达频率源相位噪声的要求。图3为借助ADIsimPLL4.10软件设计出的有源环路滤波器电路图。

虽然设计中采用有源环路滤波器产生的相位噪声性能比无源环路滤波器的差,成本也高,但由于本设计使用的VCO芯片HMC533的调谐电压超出了ADF4159的电荷泵电压,就需用到有源环路滤波器结构。此外,上电时电荷泵可能会对不具有Rail-to-Rail输入电压范围的运算放大器造成影响。因此,图3采用Rail-to-Rail的运算放大器OP184[10],OP184最大电源电压可达到36 V,增益带宽积(GBP)为4 MHz,并具有低噪声特性,该特性使OP184成为有源滤波器的理想选择。

图3 有源环路滤波器的电路设计图

由于环路带宽与参考信号源、鉴相器和环路滤波器相位噪声成正比关系,与VCO的相位噪声、锁定时间和分辨率成反比关系。兼顾以上,通过对不同阶数的有源环路滤波器的仿真,得出滤波器阶数越高,滤波效果越好,锁定时间越快,且在OP184的输出端添加一个电阻和电容,组成进一步的低通滤波级,会使系统的相位噪声进一步降低,故环路滤波器选用图3中的拓扑结构。此外,设计中将偏置电平设置为电荷泵电源(VP)的一半,既满足输入电压范围要求,又留有充足余量,并获得最佳的电荷泵杂散性能。本电路采用VP 等于5 V进行测量,运算放大器共模偏置电压为2.5 V。为了将基准噪声馈通降至最小,在同相运算放大器输入引脚附近放置1 μF的去耦电容。经过多次调整环路带宽和相位裕度,当最佳环路带宽为425 kHz,相位裕量为45°时,开环增益为0,环路稳定,此时系统的相位噪声为-91 dBc/Hz@ 1 kHz,如图4所示,满足设计要求。

图4 相位噪声仿真结果

PCB板加工完成后,进行实物测试,图5为其实物图。

图5 汽车防撞雷达频率源实物图

测试时,先准备好测试仪器并检查焊接完成的PCB板,看其是否有虚焊、漏焊等问题。接着对频率源上电。上电时,应注意上电顺序,先对PLL电路上电,再对控制电路模块上电。器件上电后,核查电源输出电压电流是否正常,确认正常后,配置编程序列。根据ADF4159数据册,由以下公式决定频率合成器的编程方式:

RFout=[N+(FRAC/225)]×fPFD

(9)

fPFD=REFIN×[(1+D)/(R×(1+T))]

(10)

式中,RFout为射频输出,fPFD为鉴相频率,N为整数分频系数,FRAC为小数分频系数的分子,REFIN为基准频率输入,D为REFIN倍频器位,R为基准分频系数,T为基准二分频位。此频率源的基准频率和鉴相频率同为100 MHz,VCO输出点频频率为24.125 GHz信号,VCO十六分频输出反馈至ADF4159。根据式(9)和式(10),和配置芯片内部的寄存器数值,通过单片机控制ADF4159内部各寄存器,使电路达到锁定。完成以上操作后,再将待测试的信号连接到安捷伦N9010A频谱分析仪,进行相位噪声测试。

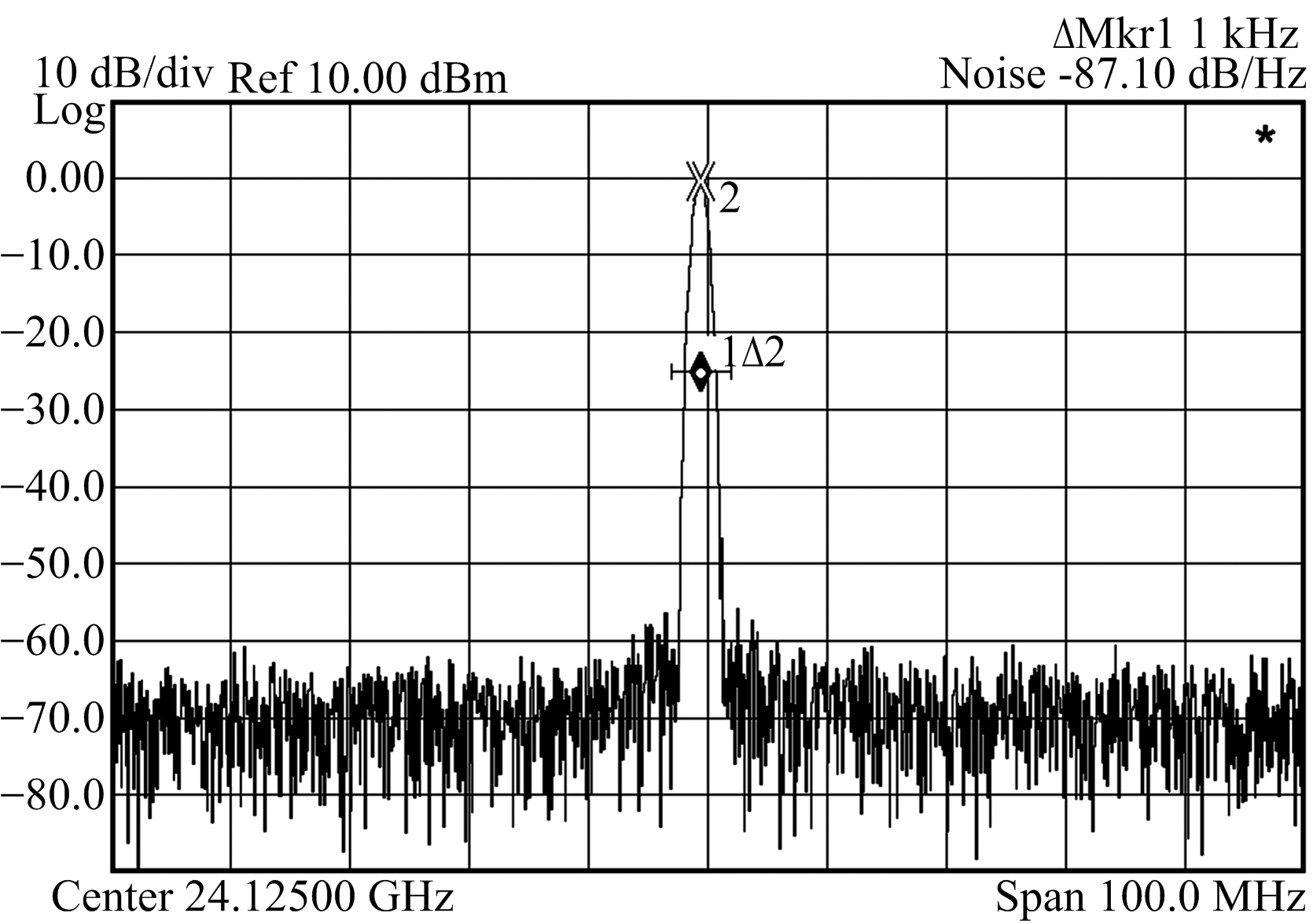

经过多次调试和优化,测试结果显示,频率源输出中心频率为24.125 GHz时,其相位噪声可达-87.1 dBc/Hz@1 kHz,如图6所示。

图6 中心频率24.125 GHz处的相位噪声

由于受到鉴相器闪烁噪声的影响,在偏移载波1kHz处相位噪声的测试结果与估算结果、仿真结果略有偏差,但高于设计要求-85 dBc/Hz@1 kHz,如表1所示。由此可见,基于相位噪声分析设计汽车防撞雷达频率源的方法是可行、有效的。

表1 本文的汽车防撞雷达频率源相位噪声

相位噪声估算值仿真值实测值dBc/Hz@1kHz-89.43-91-87.1

本文与其他同频段文献的相位噪声对比,如表2所示。本文设计的频率源的相位噪声实测值可达-87.1 dBc/Hz@1 kHz,比文献[11]中的车载防撞雷达频率源的相位噪声改善了24 dB,比文献[12]中的24 GHz调频连续波雷达频率源的相位噪声改善了21 dB。

表2 本文与其他同频段文献的相位噪声对比

相位噪声文献[11]文献[12]本文dBc/Hz@1kHz-62.23-65.75-87.1

本文结合PLL合成频率源的相位噪声模型,计算分析了各噪声源的相位传递函数特性,并对汽车防撞雷达频率源的相位噪声进行估算与仿真,测试结果为-87.1 dBc/Hz@1 kHz,满足要求。与其他文献相比,本文基于相位噪声分析设计的频率源具备低相位噪声的显著优势,这也为汽车防撞雷达频率源的研制提供了一种可借鉴的设计思路。

[1] 付钱华,易淼.参数灵活配置的通用雷达捷变频源设计[J].雷达科学与技术,2016,14(4):427-432.

[2] WANG Hongyu,WANG Haofei,REN Lixiang,et al.Low Spurious Noise Frequency Synthesis Based on a DDS-Driven Wideband PLL Architecture[J].Journal of Beijing Institute of Technology,2013,22(4):514-518.

[3] CHAE M H,KIM J H,PARK B J,et al.Phase Noise Analysis of 2.4 GHz PLL Using SPD[J].Journal of the Korea Institute of Military Science and Technology,2016,19(3):379-386.

[4] ZHOU Guangyao,WA Shunli,LI Ning,et al.A Monolithic K-Band Phase-Locked Loop for Microwave Radar Application[J].Journal of Semiconductors,2017,38(2)[025002]:1-9.

[5] 屈八一,宋焕生,周渭,等.一种新型不同频直接鉴相的锁相环[J].西安电子科技大学学报(自然科学版),2014,41(2):172-177.

[6] GOLESTAN S,GUERRERO J M,VASQUEZ J C.A Nonadaptive Window-Based PLL for Single-Phase Applications[J].IEEE Trans on Power Electronics,2018,33(1):24-31.

[7] 远坂俊昭.锁相环(PLL)电路设计与应用[M].北京: 科学出版社,2006:1-7.

[8] Analog Devices.Direct Modulation/ Fast Waveform Generating,13 GHz,Fractional-N Frequency Synthesizer: ADF4159[EB/OL].[2017-10-20].http://www.analog.com/media/en/technical-documentation/data-sheets/ADF4159.pdf.

[9] Analog Devices.HMC533LP4/ 533LP4E [EB/OL].[2017-10-20].http://www.analog.com/media/en/technical-documentation/data-sheets/hmc533.pdf.

[10] Analog Devices.Precision Rail-to-Rail Input and Output Operational Amplifiers: OP184/OP284/OP484 [EB/OL].[2017-10-20].http://www.analog.com/ media/en/ technical-documentation/ data-sheets/ OP184_284_484.pdf.

[11] 徐伟波,陈嘉成,蒋奕蕾,等.K波段防撞雷达收发前端研究与设计[C]∥ 第十一届中国通信学会学术年会,南昌:中国通信学会,2015:32-36.

[12] 汤家俊.24 GHz调频连续波雷达前端的研究和设计[D].合肥: 安徽大学,2017.