0 引 言

数据处理系统是雷达整机的重要组成部分,其任务是完成雷达点迹和航迹跟踪处理、雷达时间和能量资源的调度管理和目标情报显示,并将目标参数进行通信上报[1]。数据处理平台是数据处理系统软件工作运行的硬件载体,其设计的先进性、稳定性和可靠性对雷达整体性能的提升具有至关重要的作用。

随着现代相控阵雷达任务对目标运算处理速度、系统响应时间、总线传输带宽、数据处理能力和高可靠性等需求不断提高,传统雷达数据处理系统已经很难满足技术发展的要求。基于VPX架构的数据处理平台具备强大的数据处理能力、高性能网络交换能力以及丰富的I/O接口能力[2]。因此,VPX架构代表了新一代雷达数据处理平台系统的发展趋势和方向。鉴于此,本文结合某项目实际应用,主要介绍一种基于VPX架构的雷达数据处理平台的设计。

1 数据处理平台的设计

1.1 系统功能需求和平台设计思路

现代雷达数据处理系统的主要功能是:完成雷达目标点迹、航迹的实时处理;完成雷达时间和能量资源的调度管理;完成雷达回波显示和目标点迹、航迹信息显示;雷达目标情报信息的通信上报。

为了实现雷达数据处理系统的优越性能,结合VPX总线的特点,基于VPX总线架构的雷达数据处理平台设计思路是:1)运用高性能VPX计算刀片,利用其高速数据运算能力,实时完成雷达大容量目标的点迹处理和航迹跟踪等运算处理和信息显示;2)充分运用VPX总线的高速传输性能,实现雷达内外部数据的高速实时传输和交换;3)利用VPX总线的低时延特性,实现相控阵雷达波束实时编排和扫描;4)利用VPX可带电热插拔、结构紧凑抗震性好等优点,可在复杂恶劣环境下可靠工作[3],从而实现系统高可靠性。

图1 数据处理平台的总体设计

1.2 平台的总体设计

根据雷达数据处理系统的功能需求和平台的设计思路,基于VPX总线架构的高性能雷达数据处理平台的总体设计如图1所示,由多块VPX功能板卡组成,主要包括VPX计算刀片、VPX架构的时序接口板、VPX通信处理计算机、VPX显示计算机、交换刀片以及平台底板。该平台设计按功能划分为3个功能处理单元:1)数据处理单元 由两块高性能VPX计算机板组成,完成雷达大容量目标的点迹处理和航迹跟踪等数据处理功能。2)任务管理单元 主要由1块VPX计算机板、1块VPX架构的时序接口板和1块VPX通信处理计算机,完成雷达回波信号的接收和转发、雷达情报信息的通信上报。VPX计算机板和时序接口板通过高速SRIO(Serial RapidIO)总线连接,实现数据的高速传输和实时控制。3)显控处理单元 主要由3块VPX显示计算机组成。显示计算机通过SRIO总线和千兆网与航迹计算机和波束调度计算机互联,实现雷达回波数据和点迹、航迹数据的传输,完成雷达的回波显示、点航迹显示以及人机交互等功能。上述3个功能处理单元通过交换刀片,实现数据交互,使VPX数据处理平台具有易于扩充、便于维护等优点。

1.3 平台组成单元的详细设计

1.3.1 时序接口板

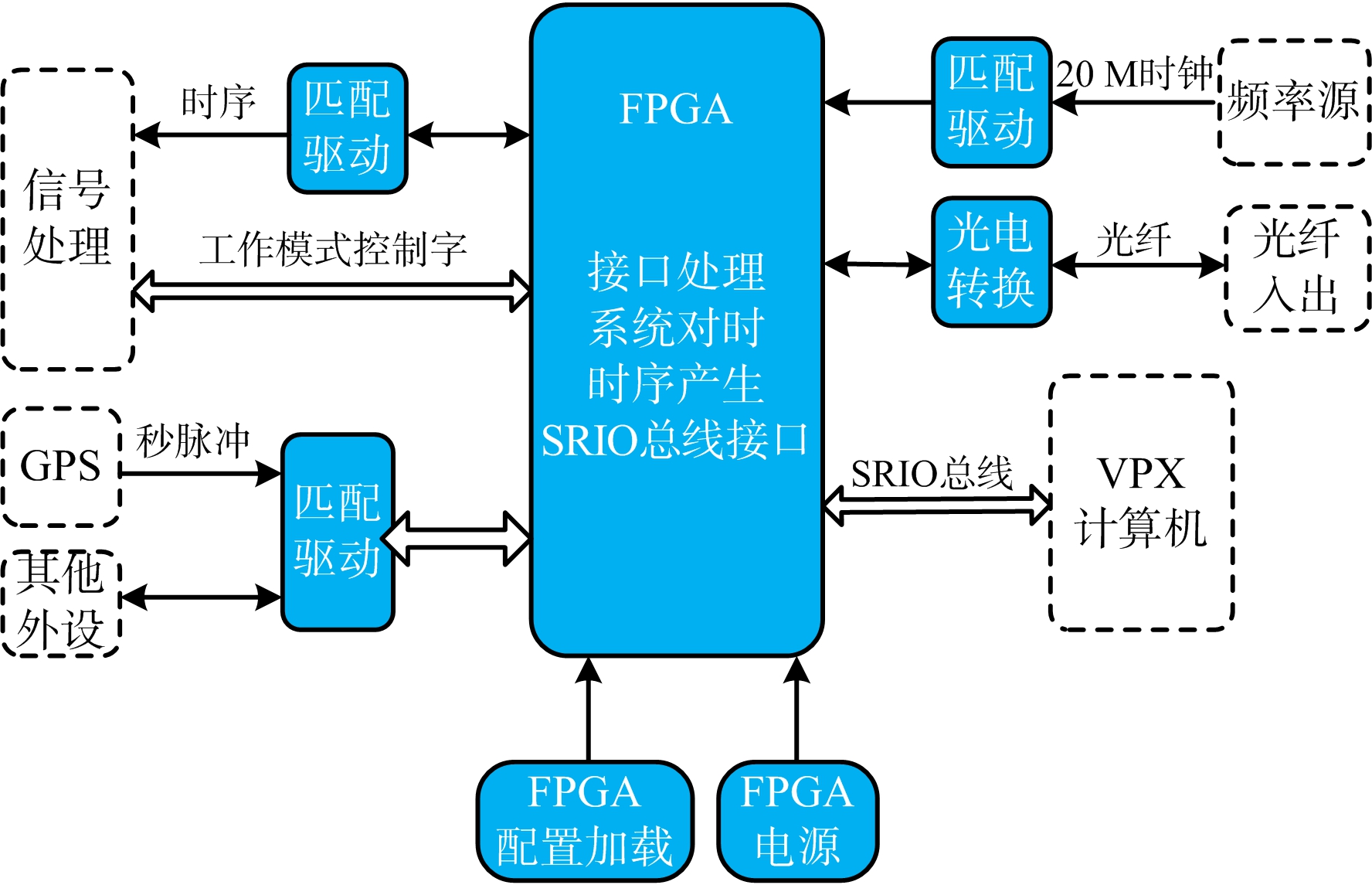

时序接口板为符合VPX总线标准的6U插件,该板卡硬件原理框图如图2所示。FPGA芯片采用高性能FPGA,容量大,处理速度快,支持高速传输。本设计中选用的芯片型号为EP2SGX90FF1508,器件中等价逻辑单元(LE)高达90 960个,片内存储器达到4.3 Mbit,可满足对存储器要求较多的应用。时序接口板主要功能电路模块包括匹配驱动电路、VPX高速总线接口电路、系统对时、方位信息处理、光电转换电路、FPGA外围电路等。除匹配驱动电路、光电转换电路、FPGA外围电路外,相关功能处理模块均在FPGA内部实现。时序接口板主要完成以下功能:1)通过SRIO总线,接收来自波束调度计算机的控制参数,产生雷达整机时序,并可通过TTL或RS422电平送出,波束编排信息可通过光纤输出至其他分系统。2)接收来自时统系统的秒脉冲信号和时间信息,完成整机时统设计,为雷达各分系统提供统一的时间基准。3)根据雷达各种工作模式,完成雷达频率源的变频控制功能。

图2 时序接口板设计原理

时序接口板对外信号接口如下:1路SRIO×4接口;12路光纤入/出,每路光纤最高传输速率可达6.375 Gbit/s;128路TTL电平接口;64路RS422电平接口。

1.3.2 VPX计算机板

计算机板在本数据处理平台中担任两个角色:1)作为数据处理计算机,完成雷达点迹处理和航迹跟踪任务;2)作为波束调度计算机和通信处理计算机,完成雷达资源管理、波束调度处理和通信控制功能。

VPX计算机板主要性能指标如下:

1) 处理器性能:Intel Xeon E5处理器或以上,单个CPU为12核或以上,单精度浮点理论峰值计算能力≥490 GFLOPS;

2) 内存:容量≥32 GB;

3) SRIO传输接口:2路SRIO 5 G×4接口;

4) 网络接口:不少于3路千兆以太网;

5) 40 G以太网接口:2路40 G以太网接口;

6) 管理与监控:2路IPMB(Intelligent Platform Management Bus)接口[4]。

1.3.3 VPX显示计算机

显示计算机是一款基于通用处理器和高性能GPU的VPX计算机,通用处理器负责业务数据流的管控和调度,GPU负责2D/3D图形计算。显示计算机主要性能指标如下:1)处理器 性能优于Intel CoreTM I7处理器及以上,主频2.2 GHz及以上;2)内存 板载32 GB DDR3双通道内存,数据速率1 333 MHz以上;3)GPU控制器 AMD Radeon E6760嵌入式显示控制器,4 GB独立显存,驱动接口符合OpenGL2.2及以上和OpenGL4.2标准,支持2D/3D硬件加速;4)显示分辨率 最高分辨率 1 920×1 200@60 Hz,支持1 920×1 080,1 600×1 200等常用分辨率。

显示计算机通过40 G以太网与航迹计算机、波束调度计算机和通信处理计算机进行雷达点/航迹信息、波束调度指令和雷达通信控制信息的交换;完成雷达参数显示、二维显示、三维显示和监控信息显示,接收显控台输入指令,完成人机交互功能。显示计算机通过SRIO总线接收来自信号处理送来的回波数据,通过回波显示软件模块实现雷达的原始回波的显示。显示计算机的功能框图如图3所示。

图3 显示计算机功能框图

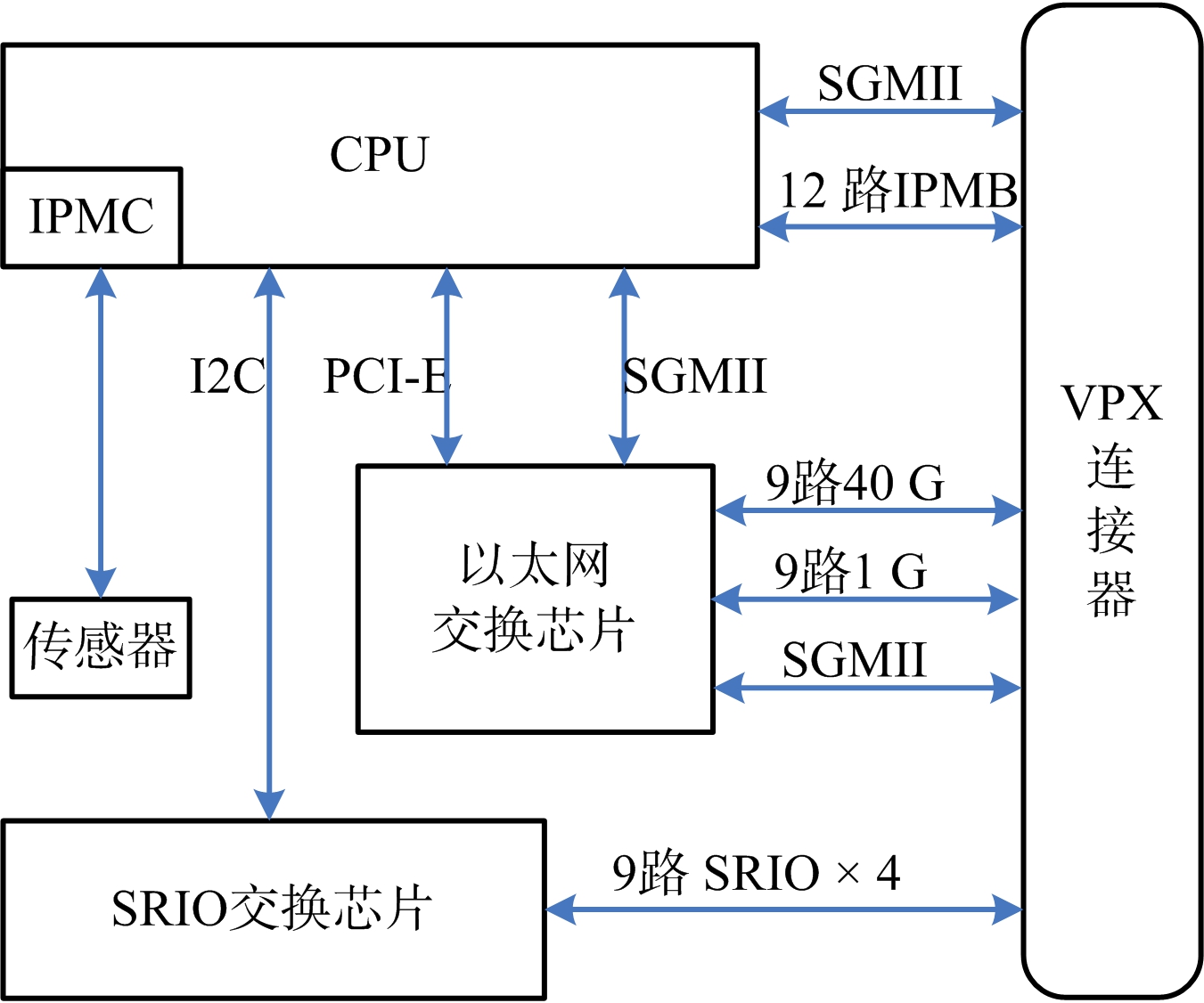

1.3.4 交换刀片

本数据处理平台交换刀片的主要功能包括两个部分:数据分发和机箱管理。

1) 数据分发:交换刀片支持SRIO和以太网双交换,负责建立平台内各计算机之间以及各计算机与外部其他设备之间的通信链路。以太网交换支持千兆以太网和40 G以太网交换。

2) 机箱管理:交换刀片负责整个数据处理平台的监控和管理,收集各功能模块的电压、温度和工作状态等参数信息,据此进行风扇调速和设备切换等管理。交换刀片的原理框图如图4所示。

图4 交换刀片原理框图

1.3.5 平台背板设计

根据数据处理平台各处理单元的任务划分和各处理板卡的性能特点,进行平台印制背板的设计。分机高度为6U,19英寸宽度,共有16个槽位。槽位布局如图5所示,具体分布如下:最左侧4个槽位为两个电源模块;背板中间为两个交换模块,同时工作,互为备份;交换模块左侧为航迹处理计算机、波束调度计算机和时序接口槽位;交换模块右侧为3个显示计算机槽位和通信处理计算机槽位。这种采用将交换板放置在中间的布局设计,可方便背板信号的互连互通。

图5 数据处理平台底板板卡的槽位布局

背板信号互联示意图如图6所示,主要信号连接关系如下:1)平台供电设计 电源槽位为各功能板卡提供+12 V的电源;2)高速信号互联 各功能模块通过交换模块实现1路SRIO×4交换;

各功能模块除时序接口模块外,通过交换模块实现1路40 G以太网和1路千兆以太网交换。

1.4 平台内外接口设计

1) 内部接口设计:平台内部各功能板卡通过交换模块实现SRIO、40 G以太网和千兆网接口互连,进行数据交互和传输。

2) 对外接口设计:光纤接口主要用于接收雷达回波数据,发送波束调度参数等;网络接口主要用于接收信号处理送来的雷达点迹参数等信号,发送控制指令至其他雷达分系统;时统接口接收来自北斗/GPS等时统设备送来的时统信号;时序输出接口输出TTL电平或RS422电平的时序信号至其他分系统。

图6 数据处理平台背板信号互联示意图

数据处理平台的内外接口设计示意图如图7所示。

图7 数据处理平台内外接口示意图

2 平台设计的关键技术

2.1 VPX总线技术的开发和应用

在雷达数据处理平台的工程设计中,时序接口板、航迹计算机板、通信处理计算机板、显示计算机板和平台印制背板全部基于标准VPX总线架构和协议设计。各功能板卡通过高速串行SRIO总线或者40 G以太网实现大容量数据的高速交换,突破了传统地面雷达的数据处理平台并行低速总线为主的技术路线。VPX总线是基于VITA46协议的新一代工业总线标准,采用了最新的接插件技术和高速串行技术,其传输速度快,理论传输速率可达10 Gbit/s[5],实时响应好,可显著提升系统实时处理和控制性能;VPX采用专用的RT2高速高密度接插件,可提供更多的自定义信号,扩展性强[6];同时VPX总线支持热插拔,也便于系统维护,全面提升平台性能。

2.2 基于物理位置的板卡槽位自动识别技术

在数据处理平台的总体设计中,航迹处理计算机和通信处理计算机的硬件板卡是相同的,3块显示计算机对应不同的任务席位,但其硬件板卡也是相同的。以上各功能计算机板卡通过运行各自的应用程序来实现航迹处理、通信处理、显示处理等不同的任务。各计算机板卡运行的操作系统也是不同的。例如,波束调度计算机和通信处理计算机因实时性要求采用嵌入式实时操作系统;显示计算机因便于雷达界面显示和人机交互采用Windows桌面操作系统。为了实现各种不同功能的计算机板卡在同一数据处理平台中混合使用,需要采用板卡槽位自动识别技术来解决以上问题。具体实现如下:

1) 在平台背板上的各个计算机板卡槽位设计硬件拨码开关,本平台共有7块计算机板卡,需要采用三位二进制拨码开关。

2) 依序对各计算机槽位的拨码开关进行编码设置,如图5所示,2块航迹计算机、1块波束调度计算机、3块显示计算机和1块通信处理计算机依次编码为000,001,010,011,100,101和110。

3) 计算机在启动后,首先识别该槽位已分配的硬件编码值,根据编码值在引导区自动选择运行对应的操作系统和工作软件,同时根据已分配的槽位编码,各应用软件自动实现本计算机板卡IP地址的分配,可避免IP地址冲突等问题。

3 结束语

本雷达数据处理平台在设计中采用了先进的VPX总线技术,合理划分并设计了各功能模块,具有高性能、模块化设计、数据传输速率高、设备易于扩充等技术特点,同时具有较高的可靠性。能适应现代大规模相控阵雷达对数据处理的计算能力和外部接口的需求。本数据处理平台主要性能指标为:1)数据处理能力 点迹处理能力10 000点/10秒,航迹处理能力1 000批/10秒;2)显示能力 能对雷达目标进行P显、A显、B显和三维显示;3)对外接口能力 具备网络和光纤等数据接口,支持TTL,RS422等硬件接口。该雷达数据处理平台已成功应用于工程项目中,通过各种环境试验和测试验证,性能优越,稳定可靠。

VPX总线以其超大带宽、高速传输能力和高可靠性成为了军用新一代总线的较佳选择,将会得到越来越广泛的应用。

[1] 丁岐鹃,王志红. 雷达数据处理的双系统设计[J]. 雷达科学与技术, 2005, 3(4):240-243.

DING Qijuan, WANG Zhihong. Dual System Design of Radar Data Processing[J]. Radar Science and Technology, 2005, 3(4):240-243. (in Chinese)

[2] 蒋迺倜,张玉喜,任延平,等. 基于VPX标准的主动雷达信号处理系统设计[J]. 雷达与对抗, 2012, 32(2):28-35.

[3] 张德智,曾星星,刘建妥,等. 基于VPX架构的测控通信综合测试系统设计[J]. 计算机测量与控制, 2016, 24(5):53-54,70.

[4] 张小林,向海斌,钟洪. 基于VPX硬件架构的新一代雷达终端[J]. 中国新技术新产品, 2016(22):4-6.

[5] 胡彦君,姜威,张会新,等. 基于VPX总线的SAR接口板卡设计[J]. 现代电子技术, 2017, 40(12):140-143.

[6] 黄泳铭,陈济民. 基于VPX总线的车载计算平台设计[J]. 测控技术, 2011, 30(4):94-96.