0 引言

本文所采用的边坡监测雷达是一种以FMCW信号为发射波形的地基SAR系统,其核心控制和数字信号处理模块架构为DSP+FPGA的异构模式。因DSP的浮点计算能力和大量函数库等优势,所以传统的雷达信号处理是在DSP中进行,但这就造成大量未经处理的回波数据在FPGA和DSP之间流动,导致二者之间的数据传输压力巨大;而FPGA除了采集和控制之外,其大部分资源处于闲置状态。若FPGA能同时承担部分信号处理任务,便可均衡下位机之间的工作量,从而提高整体的运算速度。

针对该问题,本文借助Xilinx ISE14.7开发平台所带有的RAM/ROM、Divider、FFT IP核[1],对FPGA内剩余的硬件资源进行有效利用,完成回波数据的任意数量PRT数据相干积累、汉宁加窗滤波、距离向压缩三项实时预处理功能,从硬件的角度减小了数据传输压力并完成了距离向高分辨处理。

1 FMCW地基SAR实时处理需求

1.1 系统工作原理

边坡监测雷达系统主要有雷达系统、位移台伺服系统、稳压电源系统三大部分组成。当边坡监测雷达开始运行之前,首先由上位机配置数字处理系统参数并通过以太网网口将参数包传送至下位机中,其数字系统参数如表1所示。在FPGA和DSP成功接收各自所需的采样、成像等参数,并反馈给上位机后,边坡监测雷达系统开始正常运行。

在雷达工作过程中,位移台伺服系统驱动雷达在位移台上作重轨匀速直线运动以实现合成孔径的效果[2]。FMCW雷达发射波形由雷达发射机产生,经接收天线接收原始雷达回波,并在雷达接收机中完成差拍处理、信号放大滤波等操作,将回波信号降低至稳定可被数字处理的中频信号。此后,数字板的FPGA负责整个系统的初始化、FMCW产生、AD采样、距离向降采样、数据打包以及高速传输等控制任务,而DSP执行数据存储传递以及方位向成像算法。

对于FPGA部分,根据系统参数配置,在100 MHz采样率、0.5 ms脉宽、距离向分辨率以及截取位置的限定下,AD采样经动态调相后将在一个慢时间内采集48 000点16 bit实时数据,同时由2 m合成孔径和轨道移动速度决定了方位向将会采集128 000个PRT回波,AD采样之后,数据会以差分方式传送至FPGA内部。

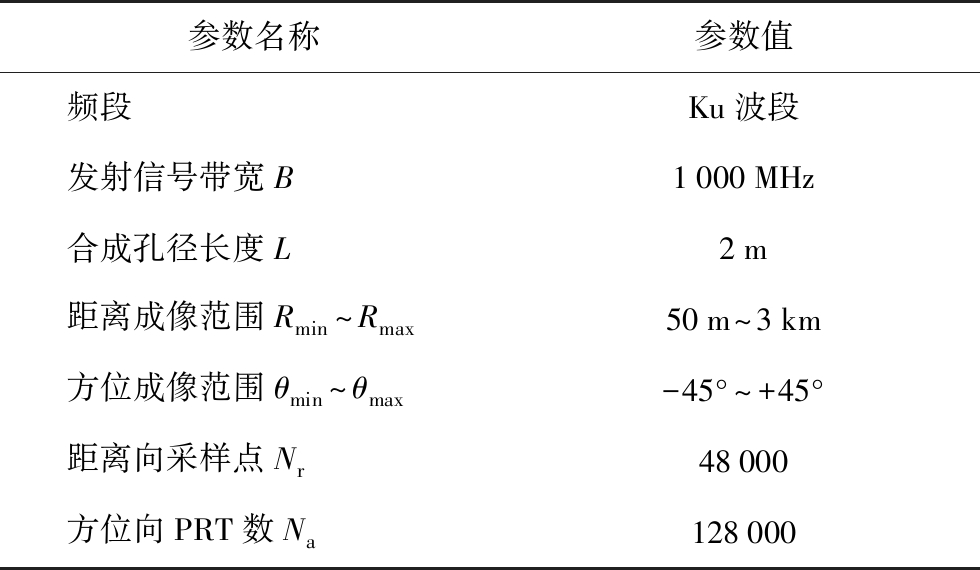

表1 数字系统参数

参数名称参数值频段Ku波段发射信号带宽B1000MHz合成孔径长度L2m距离成像范围Rmin~Rmax50m~3km方位成像范围θmin~θmax-45°~+45°距离向采样点Nr48000方位向PRT数Na128000

1.2 实时处理需求

由边坡雷达系统的工作原理和表1所示的数字系统参数可知,FPGA和DSP所组成的下位机之间将会产生巨大的数据传输压力,即存在128 000×48 000×16 bit的数据量,FPGA除了采集和控制之外并没有进行任何有效的数据处理,而是直接将原始回波数据传给DSP。面对如此庞大的数据量,DSP不仅不能减少计算量,而且还会因为后续的成像算法扩大计算量,这又加大下位机的数据运算压力。再加上此时的FPGA还存有一定未被利用的内部硬件资源,所以在硬件上就有了实现数据实时预处理的可能性。

综上,若充分利用FPGA剩余的硬件资源来进行数据预处理,实现雷达信号处理中的任意倍数相干积累、汉宁加窗滤波以及距离向压缩三项功能,那么经过数据预处理后,系统的数据运算和传输压力不仅会大大降低,而且均衡了下位机之间的任务量,由此可显著提高系统的运算速度。此外,也实现了回波信号的实时数字处理,在传入至DSP之前就可得到高信噪比、低旁瓣、距离向高分辨的新回波信号。

2 FMCW去斜处理算法

在精确测量雷达领域内,为满足距离向高分辨需求,雷达发射信号通常采用FMCW体制。因FMCW是一种常用的宽带信号,该信号的大带宽特性决定了其具有较高的距离向分辨率,同时由于雷达发射机的峰值功率限制,该信号往往采用大时宽设计[3]。

因此对于边坡雷达系统这类发射功率有限且又需精确测量的SAR来说,FMCW的大时宽带宽特性尤其适用,这不仅降低发射机功耗,同时也满足距离向高分辨需求;另一方面,由于FMCW系统不存在距离盲区,更适用于远近场兼顾的地基SAR系统。

2.1 FMCW信号模型

为了利于工程实现,本文所采用的是线性调频连续波即LFM信号,其发射信号和距离雷达Ri回波信号模型分别如式(1)和式(2)所示,其中fc为中心频率,Tp为脉宽,k为调频率,![]() 为快时间,m为整数, T为脉冲重复周期,tm=mT为慢时间。

为快时间,m为整数, T为脉冲重复周期,tm=mT为慢时间。

![]()

(1)

![]()

(2)

2.2 FMCW去斜处理实现

在边坡雷达系统中,通常采用针对FMCW而提出的解线调频技术即去斜处理来获得距离向高分辨,这也是本系统需要实现的关键功能[4]。

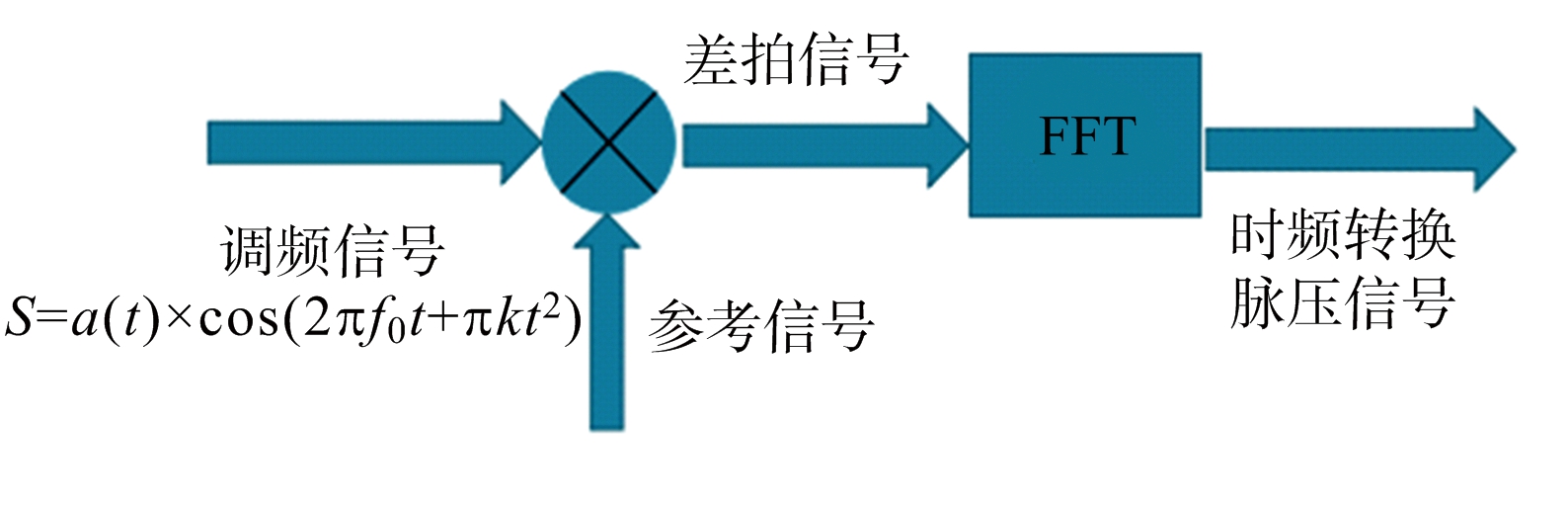

首先将参考信号与回波信号作共轭相乘即差拍处理,使回波信号变成拍频信号,并对拍频信号作FFT便可得到距离压缩结果,其去斜处理框图如图1所示。由于目标距离与差拍频点一一对应,单点目标的拍频信号经过FFT处理后得到的频谱就会产生sinc状波形,再根据频率与距离对应关系即![]() 将频率轴转换成距离轴就实现了距离向高分辨处理。此时其脉冲宽度为1/Tp,由此可知,去斜处理后的分辨率与匹配滤波的结果是一致的,且利用线性调频信号的频域特性来实现距离向高分辨使计算更为简便,同时对设备的要求也有所降低[5]。

将频率轴转换成距离轴就实现了距离向高分辨处理。此时其脉冲宽度为1/Tp,由此可知,去斜处理后的分辨率与匹配滤波的结果是一致的,且利用线性调频信号的频域特性来实现距离向高分辨使计算更为简便,同时对设备的要求也有所降低[5]。

图1 去斜处理框图

对于本系统而言,由于中频信号的频率远远超出FPGA 的处理能力,所以将差拍处理放置在雷达接收机中进行,因此去斜处理在FPGA中只需进行FFT即可。

3 实时预处理系统设计与实现

3.1 数字板硬件架构

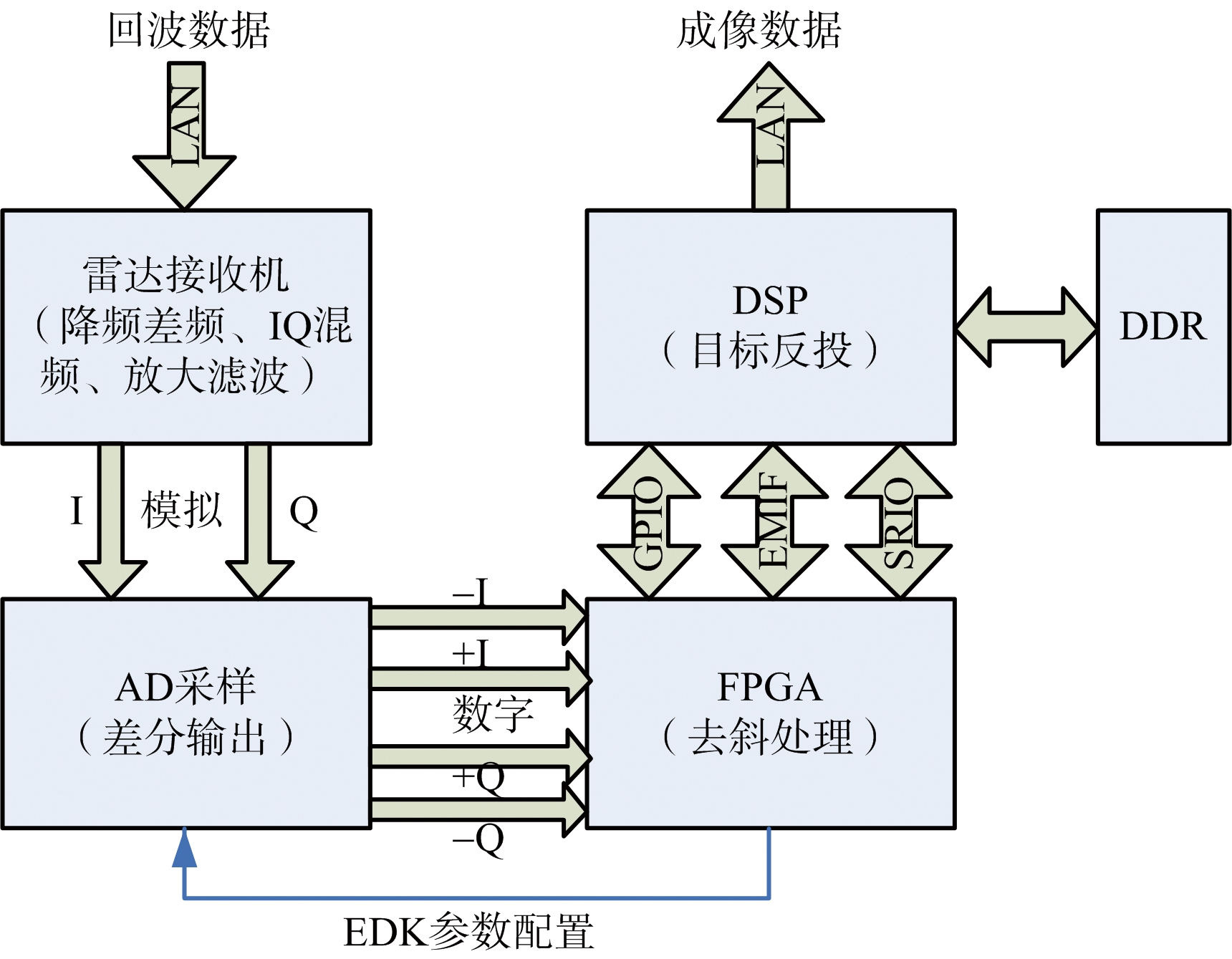

本系统采用了FPGA与DSP相结合的异构处理平台[6],其整体架构如图2所示。

系统上电后,回波信号先经雷达接收机完成射频信号的差拍处理,并以IQ两路信号方式输出至AD,经FPGA的EDK软核配置与AD采样将IQ模拟信号转化为-I,+I,-Q,+Q两对差分数字信号,之后将两对数据接入至FPGA中进行合成,生成虚实两路数字信号。接着分虚实两路同时进行实时预处理操作,最后将处理之后的数据通过SRIO(Serial Rapid I/O)输出至DSP进行目标反投,其中的GPIO(General Purpose I/O)与EMIF(External Memory Interface)协议实现DSP与FPGA的控制与反馈,使下位机之间产生交互作用,以达到可靠传输的要求。

图2 系统结构框图

3.2 软件设计与实现

FPGA作实时处理主要依靠其硬件的可重构性、并行性与高速性,以及内部查找表(LUT)的高效性,但要保证本系统实时处理的优良效果,其关键在于保证高相干性采样、最小截断效应影响以及大点数FFT精度。根据预处理流程将FPGA除顶层外分为相干积累、加窗滤波和去斜FFT三个子模块[7]。

3.2.1 实时预处理顶层模块

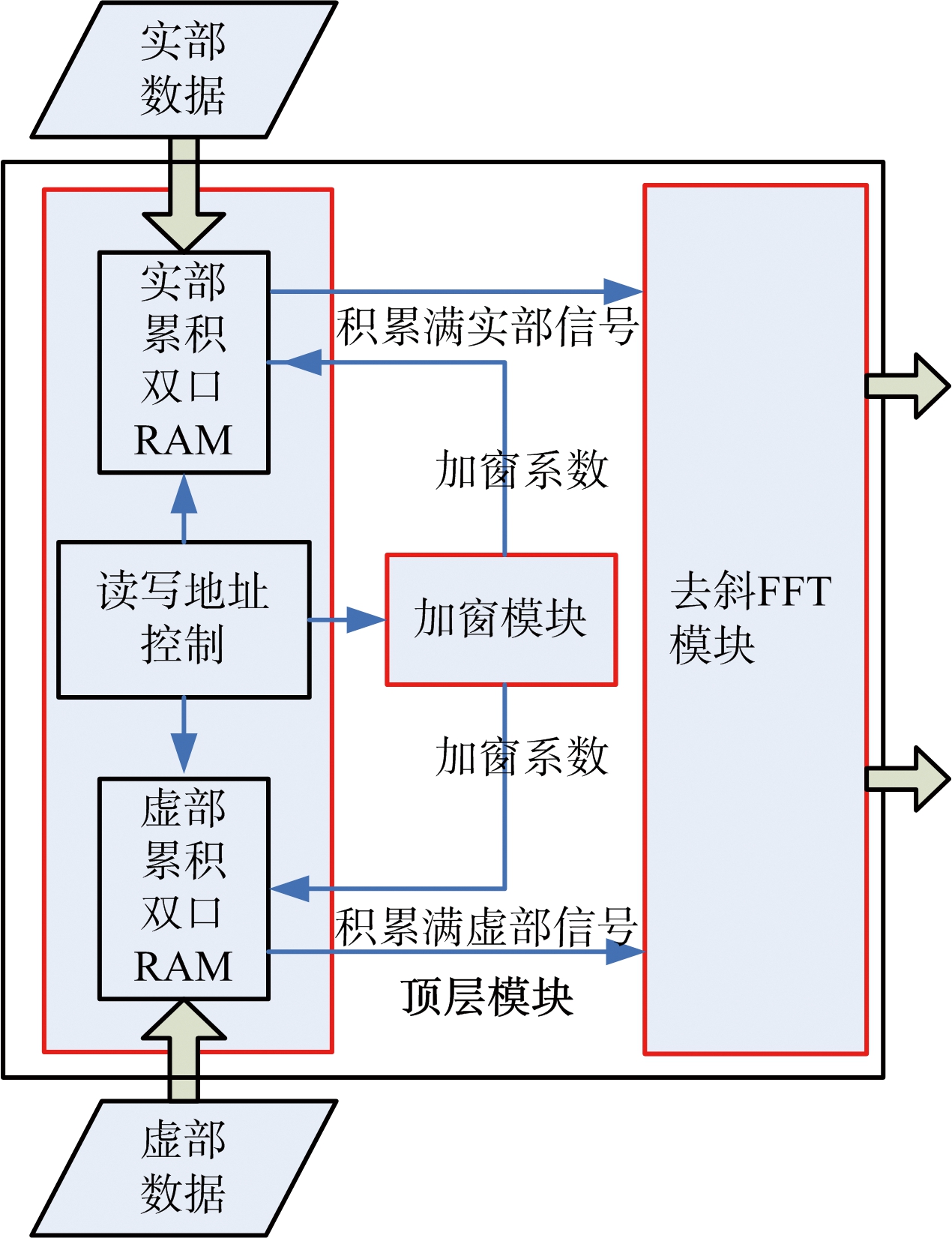

实时预处理模块是以总分结构为基础,通过顶层来实例化调用各功能模块,实现各子模块之间的物理连接和数据传递。各模块均在100 MHz的同步时钟控制下运行,保持严格的同步性,同时顶层还包括将AD采样之后的数据差分接入FPGA和处理完成之后的数据输出至DSP,其顶层结构图如图3所示。

图3 顶层结构图

为了保持数据在各模块之间的连续流入状态,所以当积累的最后一次开始时,逐点完成数据的相干积累、加窗和向FFT传输数据,又FFT采用的是流水线结构,所以每帧输出结果互不影响。于是对于整个处理过程而言,数据就能自然流入流出各模块,即实现模块间流水状态。

3.2.2 相干积累模块

相干积累就是将一定数量的存在确定相位关系的回波信号求和并平均,其信噪比就会提高积累个数倍。但信噪比提高的根本原因是,存在于雷达系统中的噪声大都服从高斯分布,所以在积累求平均后噪声信号的能量相对之前就降低了积累个数倍,相对于信号能量而言信噪比就提高了积累个数倍。本文为了得到较高信噪比与较大数据压缩比,因此以128个PRT为积累倍数。

由于数据是自然流入,要想实现积累的功能,就必须有能够缓存一个PRT回波数据的空间,同时为了抑制定点除法的量化效应,就采用先积累再求平均的方法,所以相干积累模块是利用到ISE开发平台的双口RAM IP核,开辟出能够缓存128个48 000点16 bit数据累加后的内存空间。在该模块中,需要利用双口RAM和Divider IP核来实现数据缓存和累加求平均功能,其中数据缓存就是能够缓存一个PRT的回波数据,而循环累加就是将下一个PRT与缓存PRT相同距离门的点相加,并将结果又存在缓存的原RAM地址处。在累加完成后,通过除法器让原始回波数据缩小了128倍,这样就使累加后的数据与原始回波在一个数量级,同时也减小了后续实时处理数据溢出的风险,其FPGA内部结构图如图4所示。

图4 FPGA内部结构图

值得注意的是,双口RAM其数据写入时序特点是在时钟上升沿触发写操作时,写入的数据和写入地址要在当前时刻的前一个时钟保持稳定即数据和地址数值确定,而数据读出时序特点是在时钟上升沿触发读操作时,所需要读出地址上的数据必须在当前时刻的前一个时钟已经存入该地址即读出数据稳定。只有满足上述两个时序特点才能确保输出正确波形,而对于Divider来说,本文选择的是24 bit被除数和16 bit除数,所以在片选CE信号有效26个时钟周期后才会开始连续输出正确数据。

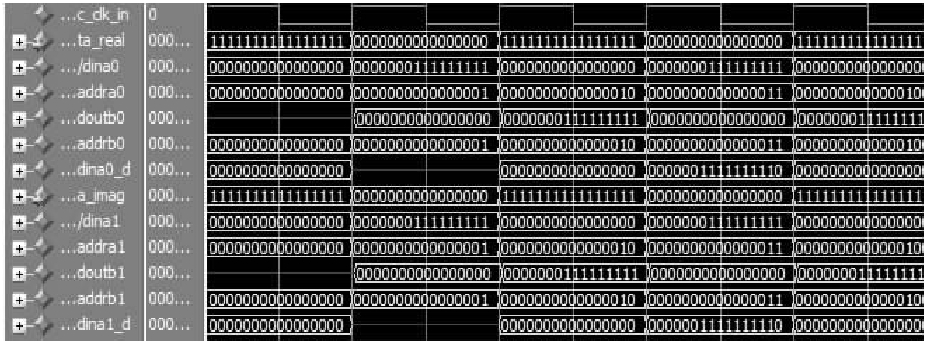

在累积过程中,存在对RAM相同存储位置的读写操作,若写入读出的数据不是积累所需,则会严重降低相邻PRT之间相干性甚至积累错误,所以参与积累的PRT起始位置一定要对齐。在积累之前,利用混合时钟管理模块 (MMCM)的动态调相能力来相参触发AD采样使能信号,从而严格控制采样起始点,以同样的初始相位来保证积累前每个PRT数据都是相干的;而积累时相干则通过同步有限状态机(FSM)来精确控制RAM的读写使能和读写地址寄存器,以每一点为单位进行逐点操作,当累加到最后一个PRT时,逐点依次进行累加、除法、加窗、向FFT中传输,直至最后一个PRT处理完毕,任意倍数相干积累RAM、Divider ModelSim波形图如图5和图6所示。

图5 RAM-ModelSim波形图

图6 Divider-ModelSim波形图

3.2.3 加窗滤波模块

当回波数据积累满128次时,就应该对数据进行加窗处理,其目的是抑制距离向压缩结果的旁瓣,使目标能量更为集中在主瓣。本系统所选择的窗为汉宁窗即升余弦窗,其数学表达式如式(3)所示:

(3)

本设计为了加快处理速度,节约FPGA中LUT(Look-Up-Table)资源,就不在FPGA中进行较难实现的余弦计算,改为由Matlab直接生成加窗系数初始化文件即.COE文件,将该文件载入ROM IP核即可立即实现加窗功能。又在FPGA中进行浮点运算将会消耗大量硬件资源,同时又要确保加窗系数的精度,所以将Matlab生成的小数加窗系数扩大2的16次幂并取整,即间接保留原有的6位小数,由此用定点计算代替浮点计算,并通过扩大倍数的方式来减小截断效应的影响,减少能量的损失[8]。当加窗操作完毕之后,将加窗后的数据右移16 bit即可消除因扩大倍数而引入的溢出风险,同时成功加窗,其ROM-ModelSim波形如图7所示。

图7 ROM-ModelSim波形图

3.2.4 FFT距离压缩模块

在经过相干积累和加窗处理后,数据得到了有效压缩和优化,之后将IQ数据输入至FFT之中,进行最重要的距离压缩处理。为了保证高精度FFT输出结果,本模块采用的是16 bit 65 536点全精度定点FFT计算,即在FFT处理过程中保留每一位有用数据,不压缩输出数据,并使用Pipelined-Streaming I/O结构。其核心算法是基于DIF抽取的基2算法,对一系列基2蝶形计算单元采用流水线设计。当FFT输入点数不满足65 536点时即当输入只有48 000点时,必须在后面继续补零至65 536点,这样才能开始进行FFT计算。

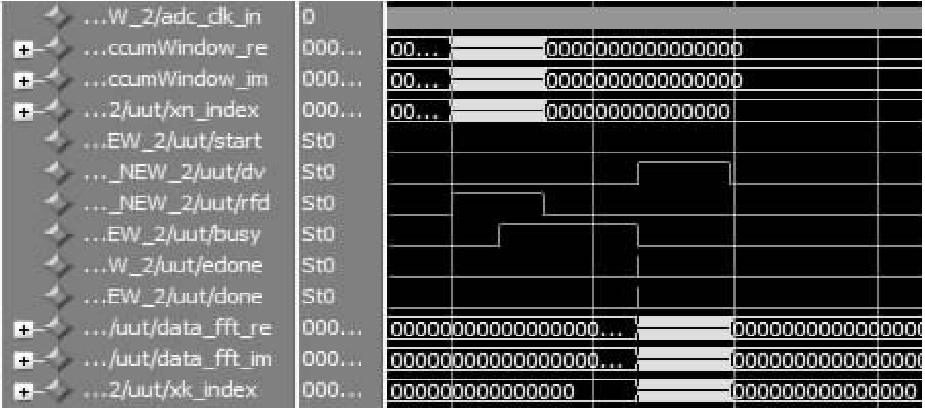

对于FFT全精度计算,其输出位数大于其输入位数,这就要将原有的寄存器数据位数扩展至预定位数,即输入位数与点数位数之和再加1,以达到防止数据溢出的效果。又FFT模块是分虚部实部两路输出,所以当虚部实部同时缩小相同的倍数将不影响整体所携带的信息,因此为了减小数据的输出位,在输出数据截取虚部实部的高16 bit,利于后续的数据打包和SRIO传输,其FFT-ModelSim波形图如图8所示[9]。

图8 FFT-ModelSim波形图

4 实验验证与结果分析

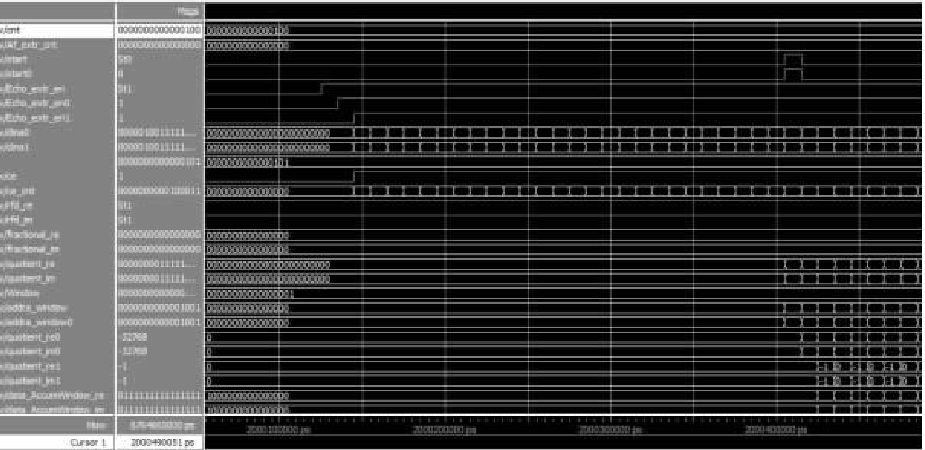

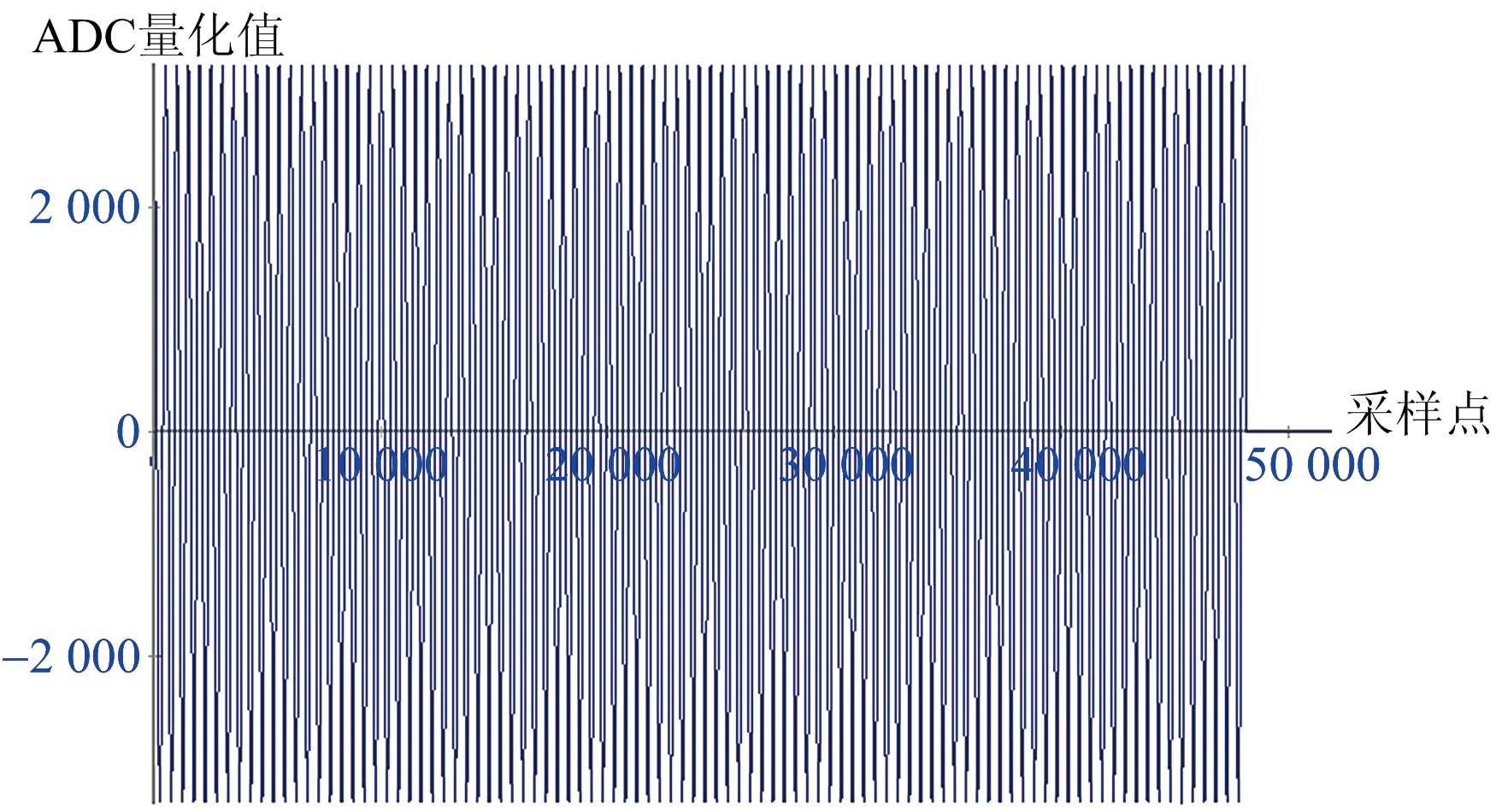

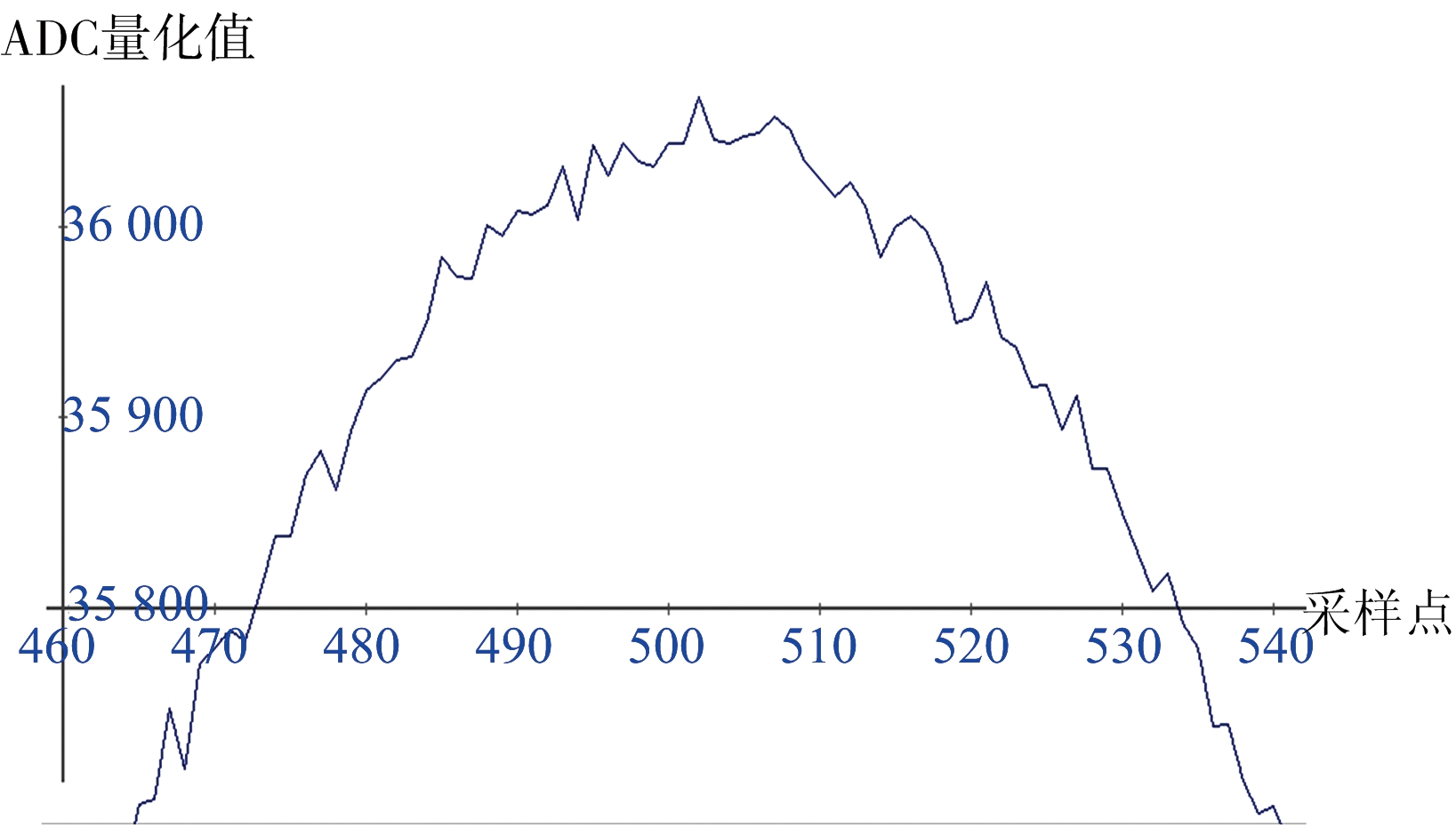

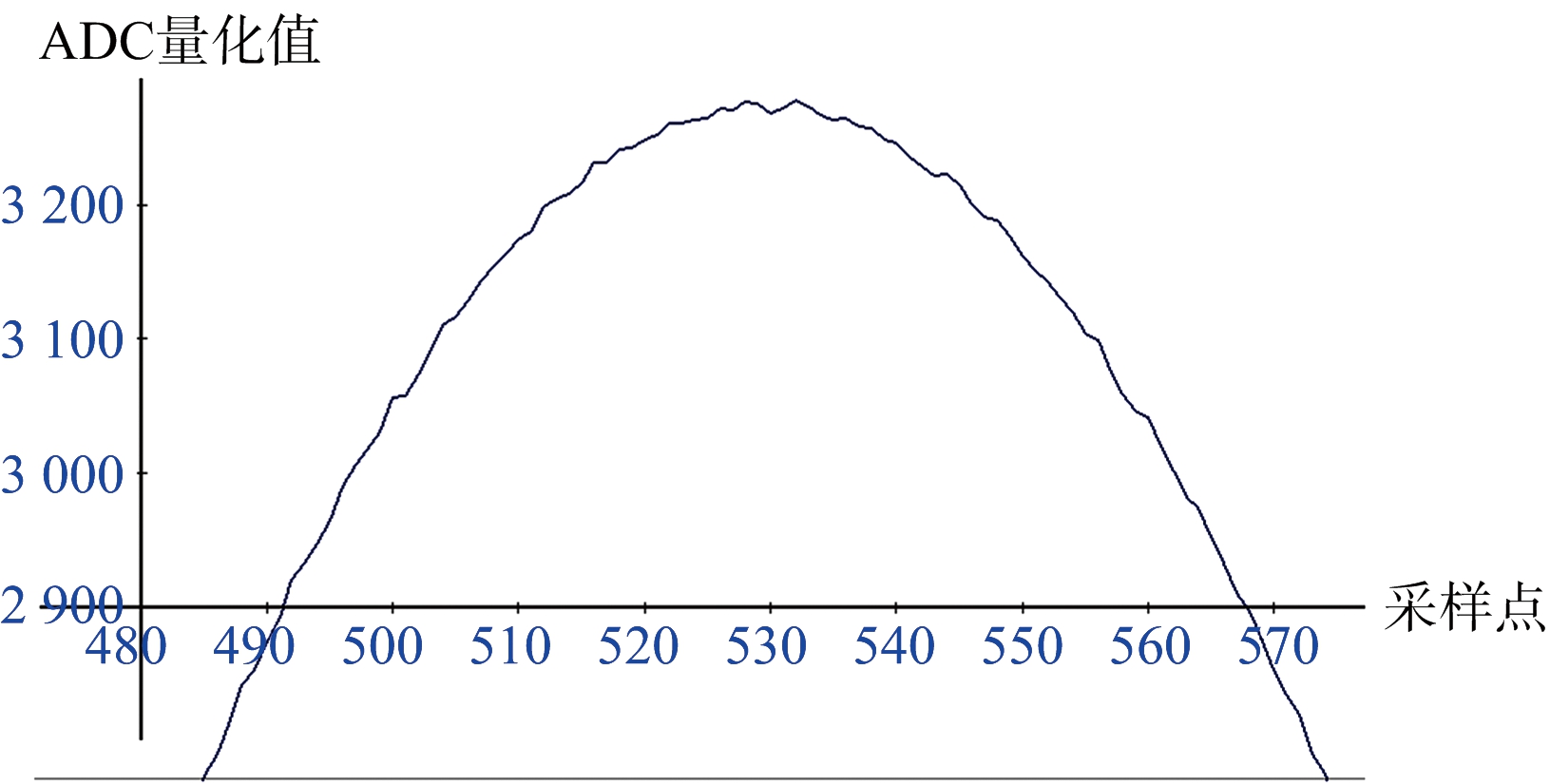

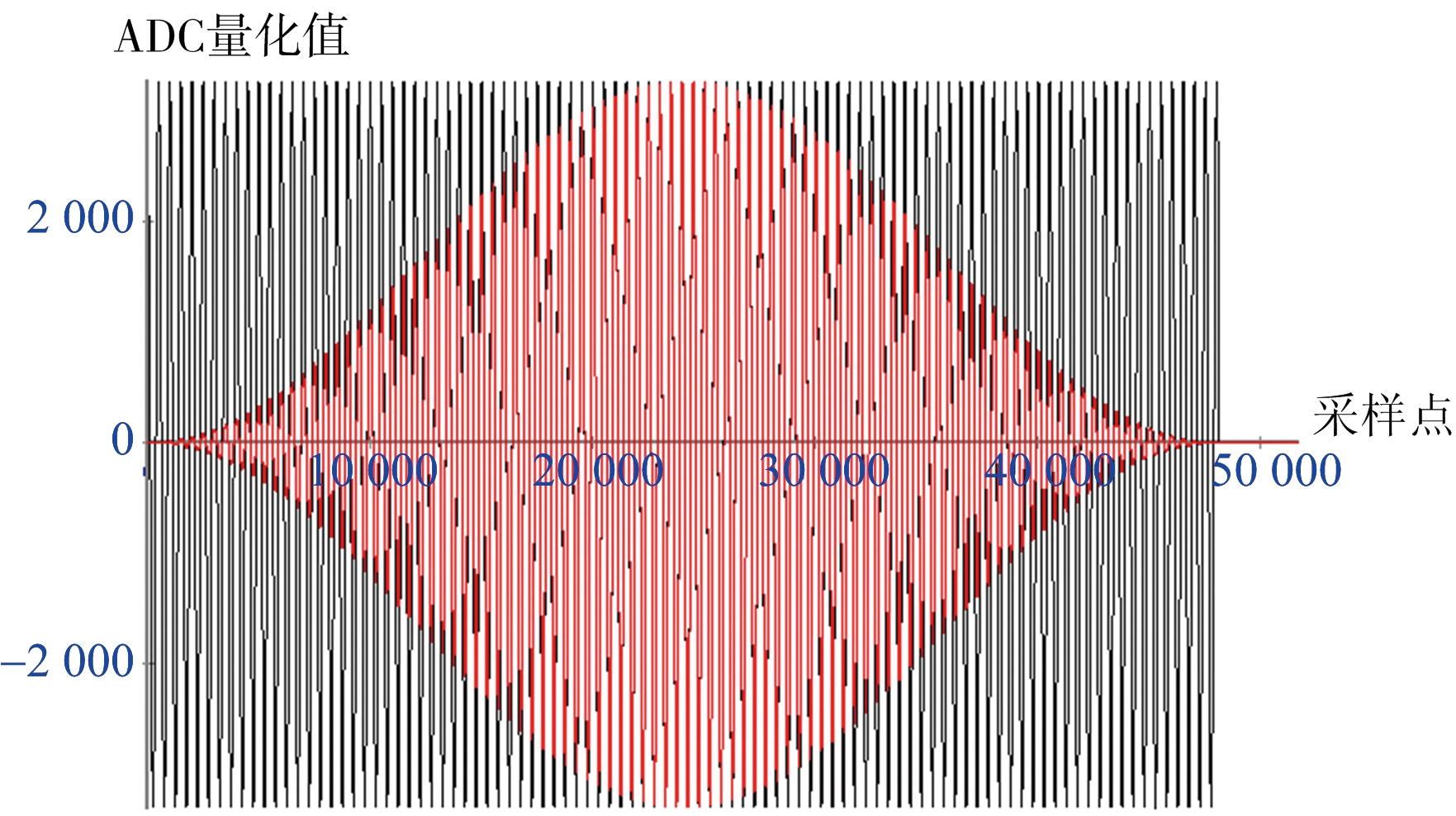

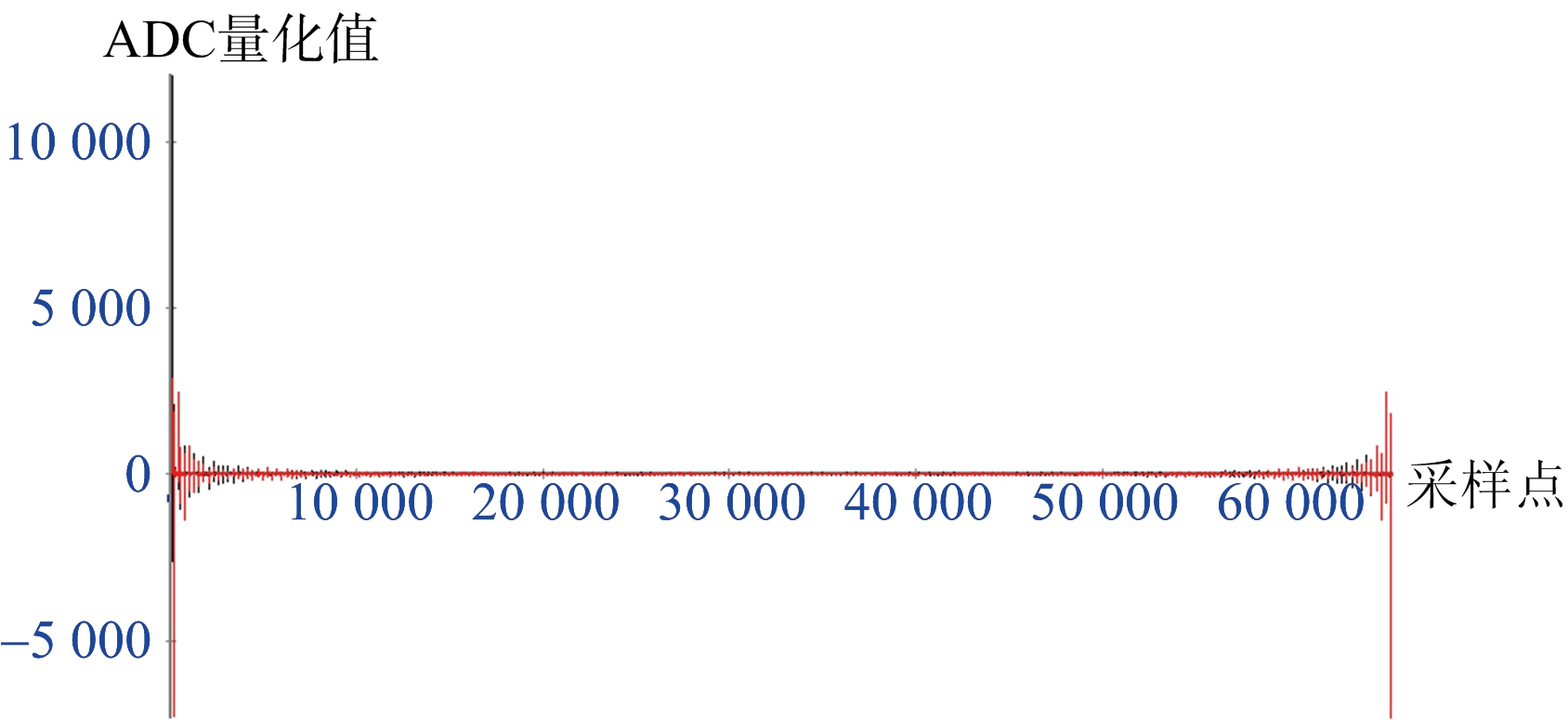

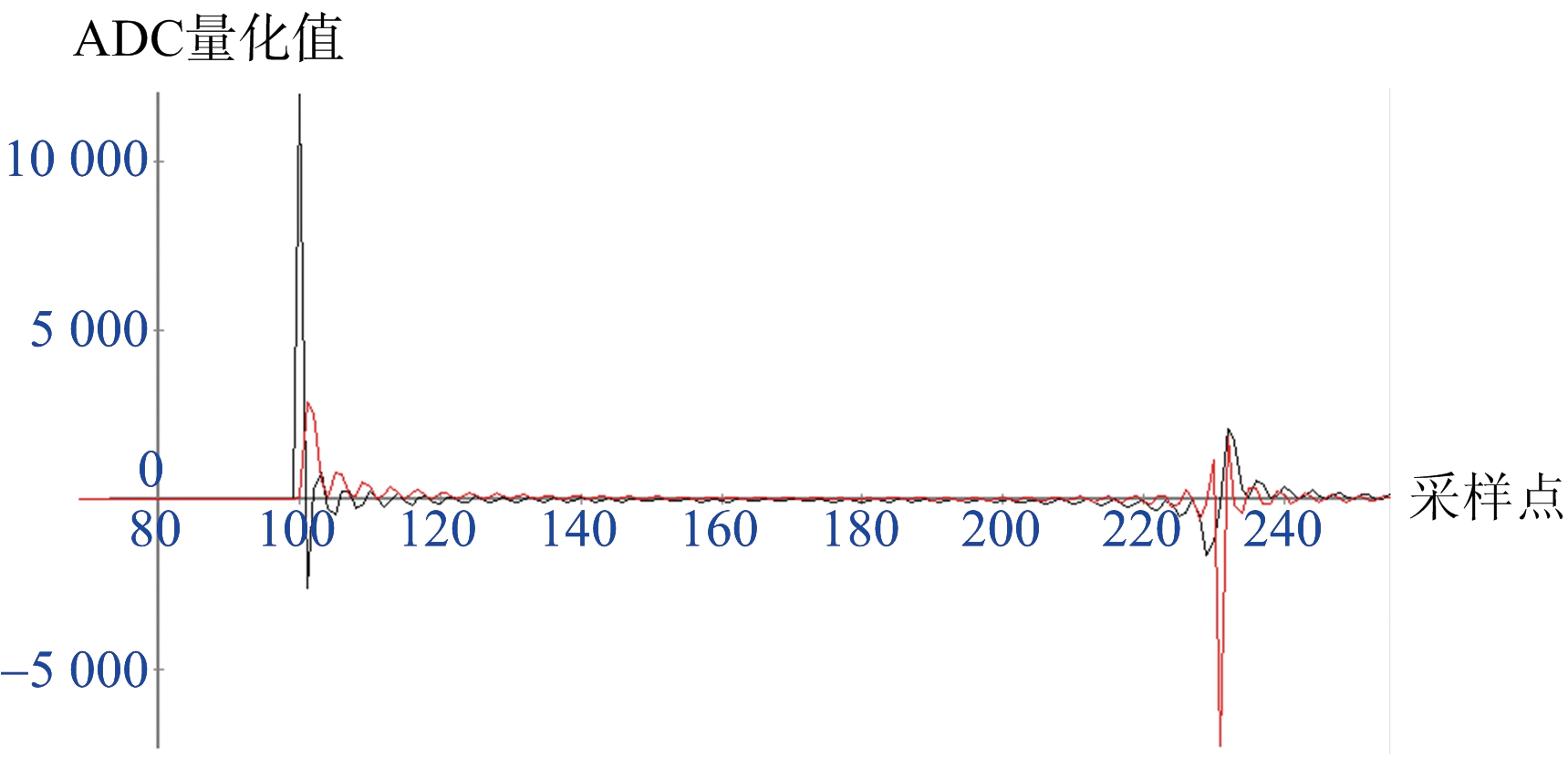

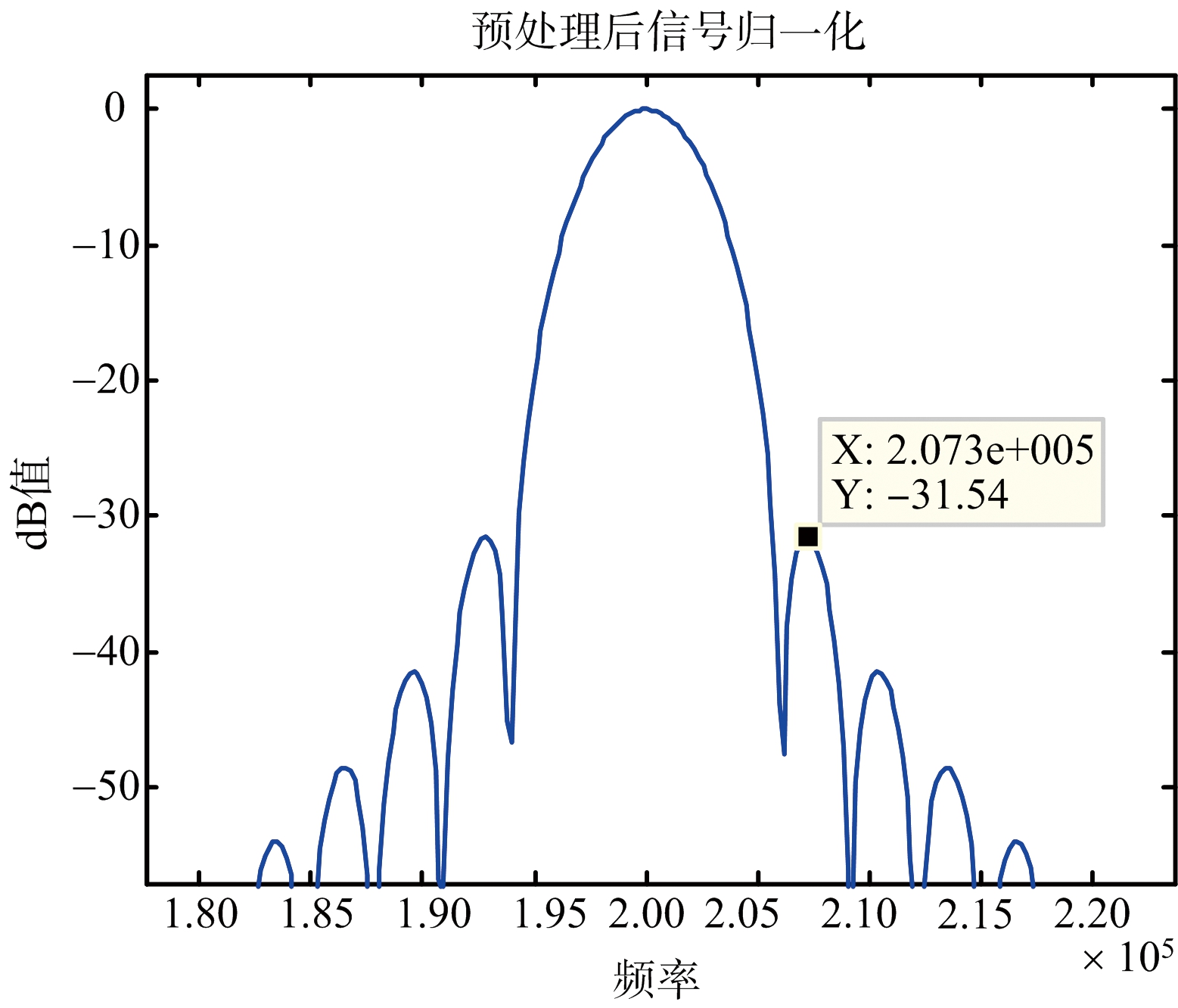

根据系统硬件架构搭建实验平台,并以200 kHz正弦波为系统输入。利用Chipscope实时抓包软件观测到,其积累后去直流波形图、原始波峰图和积累后求平均波峰图分别如图9、图10和图11所示。由图9可知,积累完毕后其波形仍为正弦波,充分证明其实时预处理模块完成了相干积累功能,并由图10和图11可明显看出,积累后的波形比不积累的要平滑很多,证明其显著地提高了信噪比。又由积累后加窗波形图和去斜FFT处理结果图即图12和图13可知,实时预处理模块正确的对积累后波形进行加窗和FFT操作,实现了距离向压缩和旁瓣抑制,并由图14去斜处理波形图可明显看出所加的200 kHz正弦信号在100 MHz采样率下准确地出现在相对直流分量的横坐标131点处即N≈200 kHz/(100 MHz/65 536),与理论值吻合,且直流分量在理论量级下[10]。另外,将预处理后的数据提出至Matlab中,可观测旁瓣降低至预期的-31.54 dB处,其Matlab仿真图如图15所示。

图9 积累后去直流波形

(ADC量化值与参考电压和量化精度有关,采样点与采样频率和回波信号频率有关)

图10 原始波峰图

图11 积累后求平均波峰图

图12 积累加窗波形图

图13 去斜FFT处理结果

图14 去斜处理波形图

图15 Matlab仿真图

5 结束语

本文所设计的FPGA系统实现了回波数据在到达DSP之前的预处理,其一次处理过程即128PRT数据采样至FFT输出所需时间为(128×48 000+26+65 536×3)×10 ns≈37.25 ms,且数据压缩率可达(128 000-1 000)/128 000×100%≈ 99.2%,距离向压缩结果的旁瓣降低至 -31.54 dB。

由以上数据可得,本系统有效地减轻了下位机之间的数据传输和运算压力,极大地提升了地基SAR系统的数据处理效率,使得该系统能够更好地满足边坡监测的实时性需求。

[1] 夏宇闻. VERILOG数字系统设计教程[M]. 2版. 北京:北京航空航天大学出版社, 2008.

[2] BAROWSKI J, ROLFES I, BAER C. Real-Time Imaging System for Millimeter Wave Synthetic Aperture Radar Sensors[C]∥First IEEE MTT-S International Microwave Bio Conference, Gothenburg, Sweden: IEEE, 2017:1-3.

[3] 龚志浩,陈章友. 基于FPGA的多模式频域脉冲压缩系统实现[J]. 雷达科学与技术, 2017, 15(4):433-438.

GONG Zhihao, CHEN Zhangyou. Implementation of Multi-Mode Frequency-Domain Pulse Compression System Based on FPGA[J]. Radar Science and Technology, 2017, 15(4):433-438. (in Chinese)

[4] 潘世伟,葛俊祥,金良. 基于FPGA的LFMCW雷达信号处理算法及实现[J]. 雷达科学与技术, 2017, 15(4):392-396.

PAN Shiwei, GE Junxiang, JIN Liang. A New LFMCW Radar Signal Processing Algorithm Based on FPGA and Its Implementation[J]. Radar Science and Technology, 2017, 15(4):392-396. (in Chinese)

[5] 刘记红,徐少坤,韩国强,等. 基于压缩感知的进动目标ISAR成像方法[J]. 雷达科学与技术, 2017, 15(4):403-409.

LIU Jihong, XU Shaokun, HAN Guoqiang, et al.ISAR Imaging Method for Precession Targets Based on Compressed Sensing[J]. Radar Science and Technology, 2017, 15(4):403-409. (in Chinese)

[6] 李艳华,肖文光. 一种基于FPGA的宽带SAR信号数字化方法[J]. 空军预警学院学报, 2016, 30(5):313-318.

[7] 陈珞,白雪杨. 基于FPGA的雷达实时测速系统硬件设计[J]. 电子测量技术, 2017, 40(6):156-160.

[8] 黄翀鹏,王剑,徐保国. 旁瓣抑制对线性调频脉冲移频干扰的影响[J]. 雷达学报, 2012, 1(3):270-276.

[9] LI Bingyi, FANG Linlin, XIE Yizhuang, et al. An FPGA-Accelerated Doppler Parameters Estimation Engine for Real-Time Synthetic Aperture Radar Imaging System[C]∥ 4th International Conference on Information Science and Control Engineering, Changsha:IEEE, 2017:169-171.

[10] GUO W, KIM Y, TEWFIK A H. A Fully Passive Compressive Sensing SAR ADC for Low-Power Wireless Sensors[J]. IEEE Journal of Solid-State Circuits, 2017, 52(8):2154-2167.