0 引言

压控振荡器(VCO)是无线通信射频系统中必不可少的组成模块[1-3]。由于射频系统中的载频信号由VCO产生,所以VCO的性能直接影响到整个射频系统性能的优劣,随着无线通信系统的快速发展,射频集成芯片的功耗越来越低,成为目前研究的热点[4-6],并且亦有多个文献在努力改善CMOS VCO的功耗和相位噪声[7-10]。

为了降低VCO的功耗,目前采用最广泛的方法就是降低VCO的供电电压,然而,为了兼顾射频系统级的供电电压VDD,还需要一个额外的调制器电路产生VDD,VCO,为VCO供电。相应地,为了降低射频系统的整体功耗,也应该使得调制器的功耗降到最低。然而,直流-直流变换器结构式调制器的摆幅噪声恶化了VCO的相位噪声,并且内部的电感极大增加了系统芯片的尺寸,增加了流片成本。如果调制器采用低压差电路结构的话,虽然不需要电感,并且摆幅噪声也不会对VCO的相位噪声造成太大影响,但是相比较于直流-直流变换器而言,消耗的功耗更大。

因而,为了降低射频系统的整体功耗,需要重新考虑VCO的供电电压,在本文中,提出了一种全新的共源共栅交叉耦合结构的CMOS VCO。为了使得调制器的功耗最小化,增加了VCO的供电电压VDD,VCO,虽然增加了VDD,VCO,但是相比较于典型的VCO,取得了更高的输出功率。为了验证所提出的VCO结构的有效性,设计并流片实现了一款2.4 GHz的VCO。

1 典型的交叉耦合式VCO

交叉耦合式VCO具有低功耗、低相位噪声的优点,得到了业界广泛的应用,而且交叉耦合式VCO差分工作的模式也利于驱动下级电路模块,抑制奇次谐波分量,降低增益退化现象产生的概率。

图1所示即为一种典型的交叉耦合式VCO的简单结构图,如图所示,VCO的振荡频率主要由LC谐振回路的电感和电容值决定,为了实现电路的振荡状态,一个晶体管的栅极与另一个晶体管的漏极交叉耦合连接。通常而言,为了降低VCO所消耗的功耗,研究者们经常降低VCO的供电电压VDD,VCO,此时,虽然晶体管漏极的峰值电压可能会高于VDD,VCO,但不会引起可靠性问题。

图1 典型的交叉耦合式VCO

虽然,VDD,VCO的降低缓和了电路的可靠性问题,减小了VCO电路本身的功耗消耗,但是考虑到整个射频系统中时,并不会降低射频系统的整体功耗。假设调制器采用低压差电路结构,并且调制器和VCO的偏置电流大小相等,都为IDD,VCO,则VCO和低压差电路的可分别表示为

PDD,VCO=VDD,VCOIDD,VCO

(1)

PDD,L=(VDD-VDD,VCO)·IDD,VCO

(2)

式中,PDD,VCO和PDD,L分别代表的是VCO和调制器的功耗,将这两个功耗相加,得到VCO和低压差电路的总功耗PDD为

PDD=PDD,VCO+PDD,L=VDD·IDD,VCO

(3)

如式(3)所示,为了改善总功耗,需要降低偏置电流IDD,VCO,而不是降低供电电压VDD,VCO。

2 提出的共源共栅交叉耦合式VCO

在本文中,设计了一种新颖的VCO,其供电电压略高于移动通信系统中的VCO电路的供电电压,鉴于VCO连接下级电路模块(例如频率分频器或者混频器),因此VCO需要驱动较大的负载电容。为了使下级电路模块的性能最优化,需要改善VCO的输出功率。因此,设计一款具有较高输出功率的CMOS VCO。

图2所示为应用了共源共栅结构的VCO电路,借助于共源共栅结构,虽然VDD,VCO的增加不会引起与晶体管漏源级间击穿相关的可靠性问题,但是共源晶体管的栅极可能面临着过大的电压,导致栅源级间和栅漏级间的击穿问题。

图2 共源共栅VCO电路

为了解决与共源晶体管栅极相关的可靠性问题,提出了一种全新的共源共栅式结构,该结构中,共源晶体管的栅极与共栅晶体管的源级相连,如图3所示,图中包含有提出的共源共栅式VCO电路核心部分、缓冲级以及电流源电路。核心部分由LC谐振回路、共源共栅结构和偏置电流源电路组成。两个变容二极管、两个电容和两个电感组成差分LC谐振回路,共源共栅结构部分用于补偿谐振回路的损耗以满足电路的起振条件。考虑到共栅晶体管的漏端电压分为共栅晶体管和共源晶体管的漏源级间电压,而且,由于共栅晶体管的源端和漏端电压彼此相等,将共源晶体管的栅极和共栅晶体管的漏极相连就不会破坏电路的振荡状态。因而,尽管增大了VDD,VCO,提出的共源共栅式VCO也不会出现可靠性问题。

图3 提出的VCO电路

为了验证本文提出电路理论的合理性,采用90 nm RF CMOS工艺对本文提出的电路进行设计,利用Cadence软件对其进行仿真。本文为了在合理的功耗消耗下实现较高的输出功率,核心电路部分的晶体管采用相对较小的尺寸,而在缓冲级部分晶体管采用相对较大的尺寸,如此,既可以通过调大输出缓冲级偏置电流的大小实现高输出功率,又可通过降低核心电路偏置电流来抑制功耗的过快增加。

图4 振荡频率和输出功率的仿真结果

通过软件仿真,图4给出了振荡频率和输出功率的仿真结果,由仿真可见,振荡频率为2.36~2.88 GHz,振荡频率随着调谐电压发生平缓的变化,并没有出现突变的情况,另外输出功率为3.54~8.11 dBm,也取得了较高的数值。为了检验电路输出信号的频谱纯度,图5给出了相位噪声的仿真结果,在调谐电压发生变化时,相位噪声在整个振荡频率范围内,取得了-135.6 dBc/Hz@1 MHz的最优值,平均值约为-133.2 dBc/Hz@1 MHz。

图5 相位噪声仿真结果

3 测试结果与分析

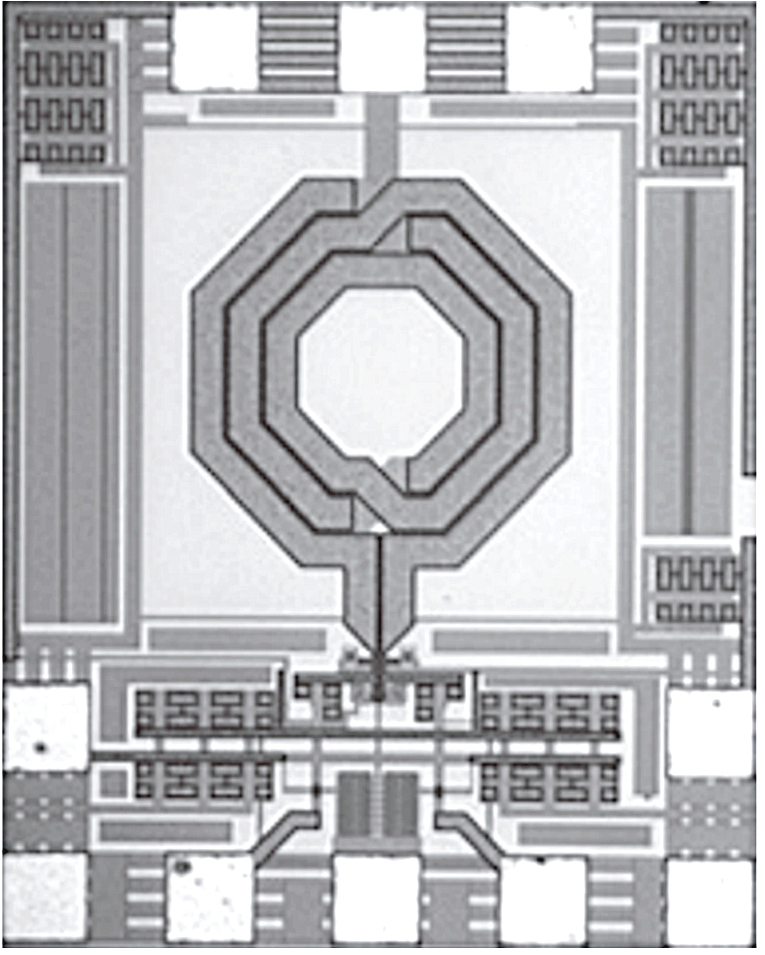

图6 VCO芯片照片

图7 振荡频率测试结果

图8 相位噪声测试结果

图9 输出功率测试结果

图6给出了本文所设计的VCO芯片照片,该VCO采用90 nm RF CMOS工艺实现,芯片大小为0.35 mm2,该VCO的供电电压为2 V,测试得到的VCO核心电流大小5.5 mA,VCO整体电路所消耗的电流为15.3 mA。图7给出了振荡频率随着调谐电压的变化情况,振荡频率范围为2.21~2.73 GHz,测试得到的调谐范围约为21.1%,与仿真结果相比,测试数值略有下降,主要原因可能是由于器件射频模型不够精确造成的。在2.43 GHz处测试得到的相位噪声结果如图8所示,由图可见,VCO的相位噪声为-129.2 dBc/Hz@1 MHz,与仿真结果相差无几,这主要得益于所采用的器件噪声模型是基于最先进的噪声理论模型所建立的,因而取得了足够高的精确度。图9给出了VCO输出功率的测试结果,由图可见,VCO在2.73 GHz操作频率时取得了最大的输出功率,为9.58 dBm,与仿真结果也相差不大。在整个振荡频率范围内,输出功率平均值约为7.1 dBm。

VCO的重要参数指标包含有振荡频率fosc、偏移频率Δf处的相位噪声PN、输出功率Pout、功耗PVCO、调谐范围TR、调谐电压的变化量ΔVtune。为了衡量VCO的总体性能,目前已有多个品质因数计算方法。

式(4)所示即为目前采用最为广泛的品质因数FOM计算方法[2-3],但是并没有将调谐范围TR考虑在内,即使一些系统实际只要求窄带VCO即可,但是由于寄生效应的存在,可能导致振荡频率发生偏移,因此VCO仍需要一个相对较宽的TR。另外式(4)也没有将Pout考虑在内,虽然可以假设已经将Pout考虑进相位噪声当中,但是相位噪声主要取决于谐振回路的输出电压摆幅,当电压摆幅增大时,如果设计输出缓冲器性能较差的话,输出功率仍可能很小。最后,ΔVtune是VCO另一个重要的性能参数,因为ΔVtune与TR直接相关,TR随着ΔVtune增大而增大,变小而变小。考虑到以上因素,文献[11]给出了如式(5)所示的品质因数FOMTVP计算方法。

(4)

表1展示了本文所设计的VCO与以往文献所报道的VCO比较结果[3, 12-14],其中给出了品质因数FOMTVP的计算结果。由表可见,本文所设计的VCO取得了最高的输出功率,相对较低的FOMTVP,综合性能指标较优。

表1 VCO比较结果

文献fosc/GHzTR /%PN /(dBc·Hz-1)Δf/MHzPout/dBmPVCO /mWΔVtune/VFOMTVP /dB本文2.4721.1-129.217.130.62-189.8[3]5.36821.4-117.341-52.812-183.0[12]3.87518.3-123.2811.454.82-188.9[13]2.1919.2-130.341-0.843.92-190.0[14]2.439.9-1221-2.490.461.8-185.4

4 结束语

本文提出了一种共源共栅式CMOS VCO结构,以改善射频系统的整体功耗。该VCO的核心电路部分采用一种共源共栅晶体管结构,此结构可以施加较高的电压,并且不会引起与晶体管漏极相关的击穿问题。为了减轻与晶体管栅源级间和栅漏级间相关的击穿问题,将共源晶体管的栅极与共栅晶体管的源级相连。采用所提出的VCO核心电路,在没有引起晶体管可靠性问题的情况下,成功提高了VCO供电电压。而且,借助于VCO电压的提高,提高了VCO的输出功率,以更好地驱动下级电路模块。为了验证所提出VCO的实用性和有效性,基于90 nm RF CMOS工艺流片实现了一款2.4 GHz的VCO,该VCO在2.0 V电压供电下,取得了较高的输出功率。

[1] CHANG Y T, LU H C. A K-Band High-Efficiency VCO Using Current Reused Technique[J]. IEEE Microwave and Wireless Components Letters, 2017, 27(12):1134-1136.

[2] SHIRAZI A H M, NIKPAIK A, MOLAVI R, et al. On the Design of mm-Wave Self-Mixing-VCO Architecture for High Tuning-Range and Low Phase Noise[J]. IEEE Journal of Solid-State Circuits, 2016, 51(5):1210-1222.

[3] HSU M T, LI W J, HSU S C. Design of Low Phase Noise CMOS VCO Using Cross Coupled Topology with Capacitor Feedback[J]. Microelectronics Journal, 2016, 54:32-39.

[4] KIM S, OH T. 2×3.2 Gb/s Single-Ended IO Transmitter with Low-Power Dynamic FIR Driver for the LPDDR4 Standard[J]. Electronics Letters, 2017, 53(24):1566-1568.

[5] LEE C J, KANG J S, PARK C S. A D-Band Low-Power Gain-Boosted Up-Conversion Mixer with Low LO Power in 40-nm CMOS Technology[J]. IEEE Microwave and Wireless Components Letters, 2017, 27(12):1113-1115.

[6] LIN J T, LIN H H, CHEN Y J, et al. Vertical Transistor with n-Bridge and Body on Gate for Low-Power 1T-DRAM Application[J]. IEEE Trans on Electron Devices, 2017, 64(12): 4937-4945.

[7] JANG S L, LIN Y C. Low-Power Three-Path Inductor Class-C VCO Without any Dynamic Bias Circuit[J]. Electronics Letters, 2017, 53(17):1186-1188.

[8] ZOU P, MA K, MOU S. A Low Phase Noise VCO Based on Substrate-Integrated Suspended Line Technology[J]. IEEE Microwave and Wireless Components Letters, 2017, 27(8):727-729.

[9] TU C C, WANG Y K, LIN T H. A Low-Noise Area-Efficient Chopped VCO-Based CTDSM for Sensor Applications in 40-nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2017, 52(10):2523-2532.

[10] 陈绍东,牛子昱. 基于电流复用技术的亚mW级CMOS VCO设计[J]. 雷达科学与技术, 2016, 14(5):558-560.

CHEN Shaodong, NIU Ziyu. Design of Sub-Milliwatt CMOS VCO with Current-Reuse Technique[J]. Radar Science and Technology, 2016, 14(5):558-560. (in Chinese)

[11] ZHANG Jincan, ZHANG Yuming, LÜ Hongliang, et al. A Ku-Band Wide-Tuning-Range High-Output-Power VCO in InGaP/GaAs HBT Technology[J]. Journal of Semiconductors, 2015, 36(6)[065010]:1-5.

[12] JAIN S, JANG S L, TCHAMOV N T. Oscillation Mode Swapping Dual-Band VCO[J]. IEEE Microwave and Wireless Components Letters, 2016, 26(3):210-212.

[13] JANG S L, LIN Y C, LAI W C, et al. A Class-C Quadrature VCO Using the Varactor Coupling Technique[J]. Microwave and Optical Technology Letters, 2016, 58(8):1961-1963.

[14] LEE C H, LIM C, YUN T Y. Swing and Phase-Noise Enhanced VCO with Capacitive-Division Dynamic-Threshold MOS[J]. IEEE Microwave and Wireless Components Letters, 2016, 26(3):219-221.