0 引言

毫米波雷达传感器因其可全天候工作、综合测量性能好、成本低等优点,成为目前智能驾驶及未来无人驾驶车辆中的主力传感器。毫米波汽车雷达的研究始于20世纪60年代,早期的雷达工作频段主要是24 GHz和35 GHz频段[1],随着微电子和雷达技术的发展,77 GHz频段因具有更宽的带宽、更高的分辨率及更小的模组尺寸,成为汽车雷达的主流并形成规范[2-10]。传统的毫米波雷达收发机主要由基于GaAs、SiGe等工艺的分立芯片搭建而成,成本高、体积大[4-6]。随着摩尔定律的进步,晶体管的速度越来越快,基于CMOS工艺的77 GHz毫米波雷达前端芯片开始出现,雷达的集成度和性能不断提高,成本持续降低;采用单颗芯片实现不同模式、不同场景的雷达感知需求,成为目前工业界和学术界热点研究方向[6,8,10]。

基于CMOS工艺实现77 GHz毫米波雷达收发前端芯片的研究工作在不断前进。文献[3]介绍了国际上第一个基于CMOS工艺的包含了完整的收发前端和FMCW雷达波形发生器的77 GHz收发前端芯片;文献[6]采用45 nm CMOS工艺,集成了3发射通道、4接收通道、FMCW波形产生器和ADC等功能模块;文献[7]针对车辆近距离感知场景,设计了一款包含1发1收雷达收发机和信号处理的SoC芯片,通过多点定位的方式实现雷达测量功能;文献[9]介绍了一种77 GHz 2发3收毫米波芯片,基于该芯片给出了一个综合性能良好的4×6 MIMO雷达解决方案。然而,针对未来高级别智能驾驶对毫米波传感器多模式、多场景感知需求,CMOS毫米波收发机设计因此仍面临诸多挑战。例如:毫米波收发前端需要具备更强的可配置性,而文献[3]、文献[7]仅适用近距离探测需求;发射前端需要产生更大的发射功率以达到更远的探测距离,文献[3]、文献[6]发射功率分别为5.1 dBm、11 dBm;此外,为了满足更高的分辨率和数据更新速率需求,FMCW需要具备更大的调频带宽和更快的调制速度。

本文设计并实现了一种高集成度76~81 GHz毫米波汽车雷达收发前端芯片,单片集成了3路发射和4路接收、FMCW波形发生器、模数转换器以及高速数据接口等电路,收发系统的发射功率、波形样式、接收增益和带宽等参数具有较好的可配置性,满足未来多模式、多场景汽车雷达传感器需求。

1 FMCW雷达基本原理及系统架构

1.1 FMCW基本原理

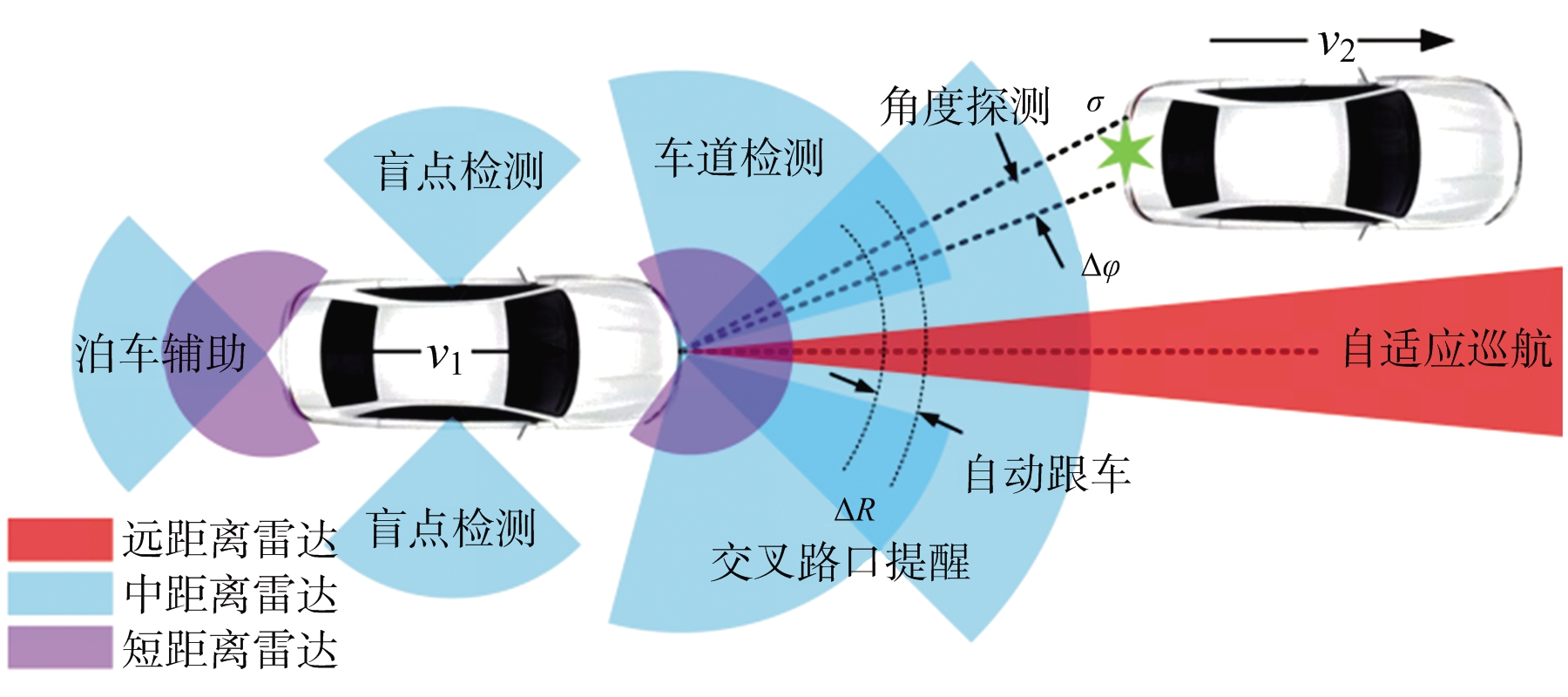

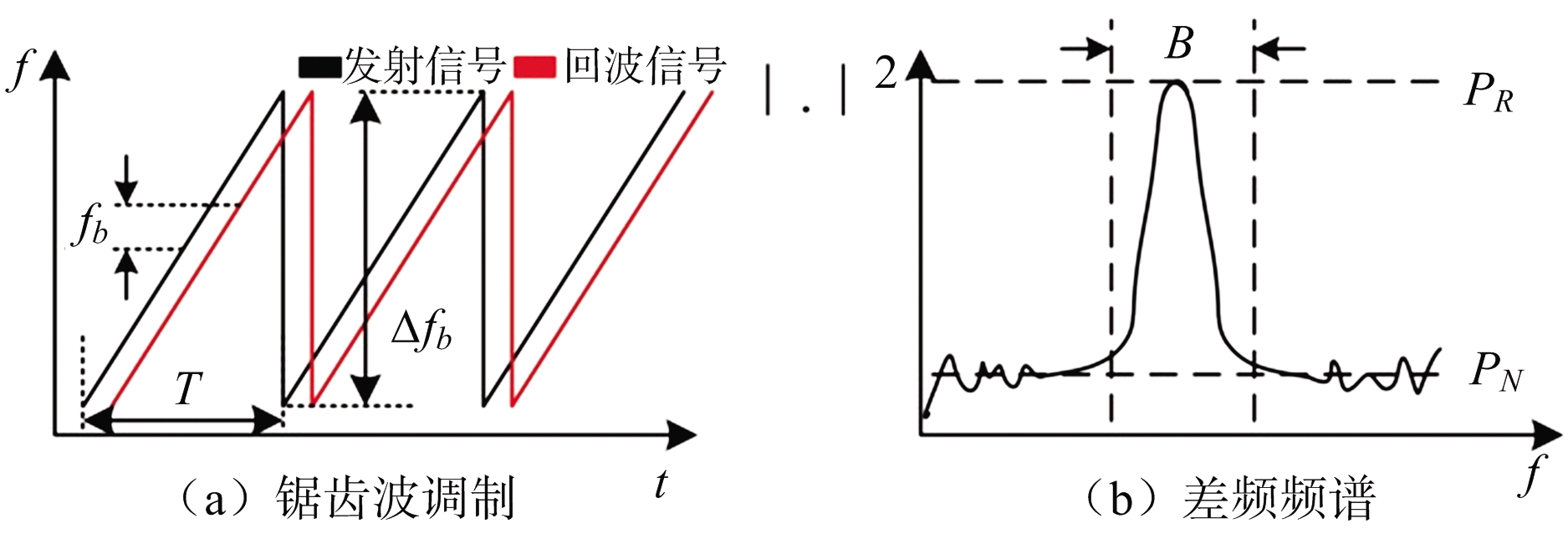

一个典型的汽车雷达使用场景如图1所示,FMCW雷达通过发射天线发射调频连续波信号,同时接收天线接收目标反射信号,通过分析二者混频得到的中频信号可以得到目标的距离、相对速度和角度等信息。线性调频连续波一般有锯齿波和三角波两种调制波形,图2示出其测量基本原理。

图1 多模毫米波汽车雷达在智能车辆上的应用

图2 FMCW雷达测量基本原理

发射机发射线性连续调频锯齿波,带宽为B=f2-f1, 每个chirp周期为T,经过时间τ后收到目标回波,两者频率差为![]() 其中

其中![]() 为目标与雷达的距离,c为光速。此时忽略了目标运动带来的多普勒频移,实际上,在快速扫描的情况下,车速造成的多普勒频移非常小,在此可以忽略。由上式可得目标的距离为

为目标与雷达的距离,c为光速。此时忽略了目标运动带来的多普勒频移,实际上,在快速扫描的情况下,车速造成的多普勒频移非常小,在此可以忽略。由上式可得目标的距离为

(1)

运动目标造成的多普勒频移也会反映在中频信号上,虽然其在频率上难以分辨,但是引起的相位变化是可分辨的,相邻两个chirp的中频信号相位差可表示为![]() 其中

其中![]() 为多普勒频率,v为运动目标与雷达的相对速度,λ为毫米波波长。比较相邻两个chirp中频信号相位差,可得到相对速度为

为多普勒频率,v为运动目标与雷达的相对速度,λ为毫米波波长。比较相邻两个chirp中频信号相位差,可得到相对速度为

(2)

目标角度的获得需要至少两个接收通道与其对应的天线,假设目标偏离雷达正前方的角度为θ,两个接收天线距离为D,回波到达两个天线的波程差为L=Dsinθ,两个接收通道的相位差为![]() 可得角度表达式:

可得角度表达式:

(3)

当θ较小时,可简化为![]()

1.2 收发机芯片系统架构和参数分析

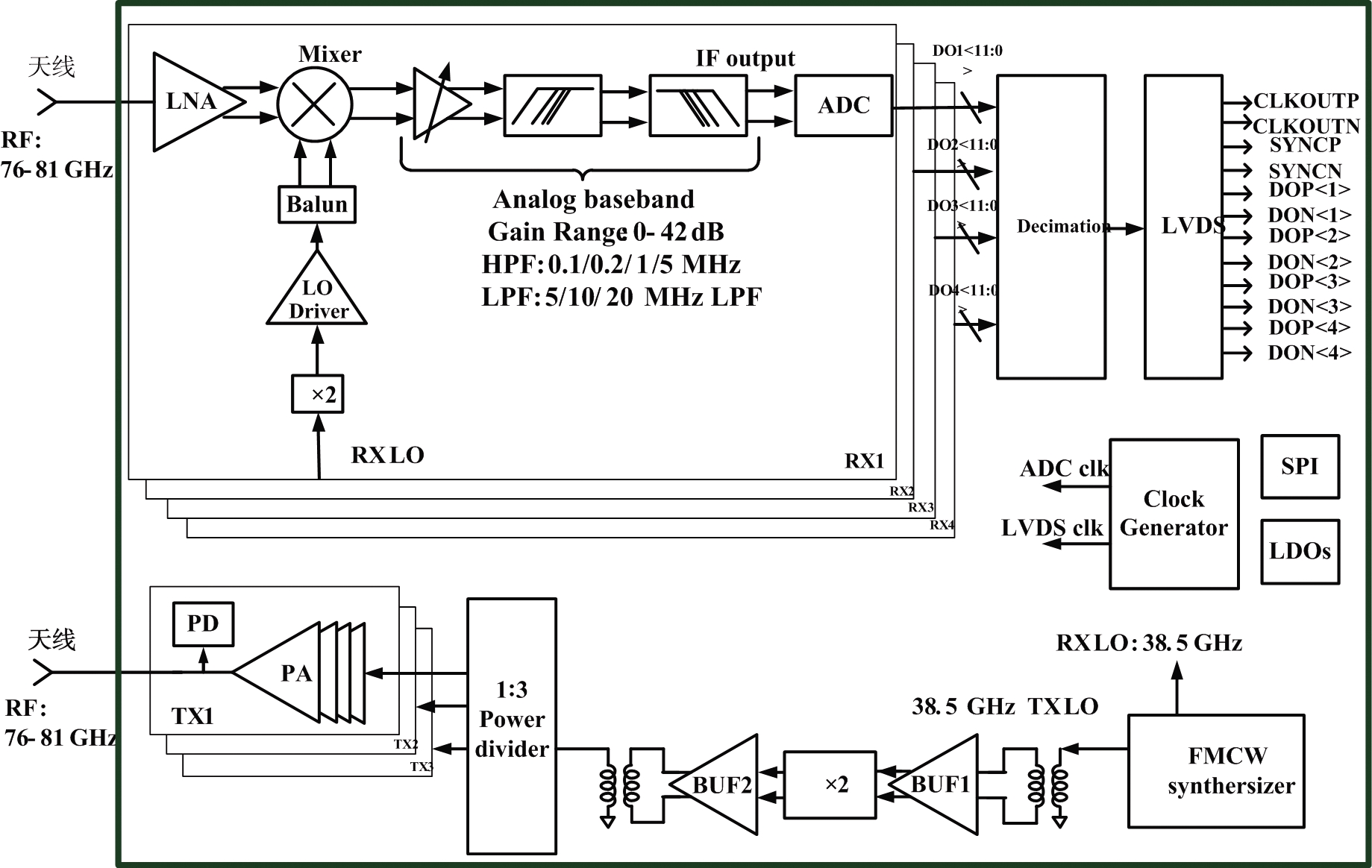

针对汽车雷达单芯片多模式、多场景应用需求,本文提出的收发机芯片架构如图3所示。片上包含了3路毫米波发射机、4路毫米波接收机(含ADC)、抽取滤波器(Decimation)和高速数据接口(LVDS)、FMCW波形产生器(FMCW Synthesizer)、时钟产生器(Clock Generator)以及通信接口(SPI)、电源管理(LDOs)等。考虑到锁相环设计难度,及链路折衷考虑,FMCW波形产生器设计为38.5 GHz频段,通过功分网络分别送至4通道接收机和3通道发射机。在接收机分系统中,FMCW波形产生器产生的38.5 GHz频段信号首先二倍频至77 GHz频段,再通过四功分器及放大链路送至接收机混频器;在发射机系统中38.5 GHz频段FMCW信号首先二倍频至77 GHz频段,再通过三功分器、放大链路及末级功放(PA)作为发射机输出。

图3 多模76~81 GHz雷达收发机芯片架构

根据雷达方程,雷达最大探测距离与发射功率、收发天线增益、接收机带宽及噪声系数等参数直接相关:

(4)

式中,PR为雷达接收机接收到的距离R处的目标回波信号功率,PT为雷达发射机发射功率,GR、GT分别为接收天线、发射天线的增益,σ为目标的雷达横截面积,kT为热噪声,NFtot 为总的接收机噪声系数,BWFFT为FFT分辨率带宽,SNRmin为最小可检测信噪比。若前端ADC采样率为fs,FFT点数为N,FFT带宽可以表示为

(5)

将式(5)代入式(4)可以得到

(6)

根据上述公式,假设收发天线增益为20 dBi,采样率50 MHz,FFT点数为2 048,对于小汽车目标,探测距离要求为250 m,噪声系数为12 dB时,发射功率要求为13 dBm左右。考虑到65 nm CMOS工艺性能,可设计雷达芯片最大发射功率为13 dBm、最低噪声系数为15 dB,通过增加FFT点数可做到远距离测量。对于近距离目标测量,可适当降低发射功率。当发射功率-7~13 dBm可调,对应于不同距离小汽车目标,接收机接收到的功率范围为-10.2~-114.1 dBm,其最大输入1 dB压缩点应设计为-10 dBm。考虑12 bit ADC噪声及最低可检测信噪比,接收机检测最小信号所需增益为71.2 dB,因此其最大增益可设计为72 dB。对于多模应用,设计接收机增益范围为30~72 dB,相应的输入1 dB压缩点大于-10~-30 dBm。由式(1)可知,距离分辨率与调频带宽成反比,带宽越宽,则距离分辨率越好。锯齿波调频时,由式(2)可知,速度分辨率与调频周期成正比,调频周期越短,则速度分辨率越好。为了提高Chirp带宽并降低周期,Chirp斜率要尽量大。

2 关键电路设计与实现

2.1 可配置多通道毫米波接收前端

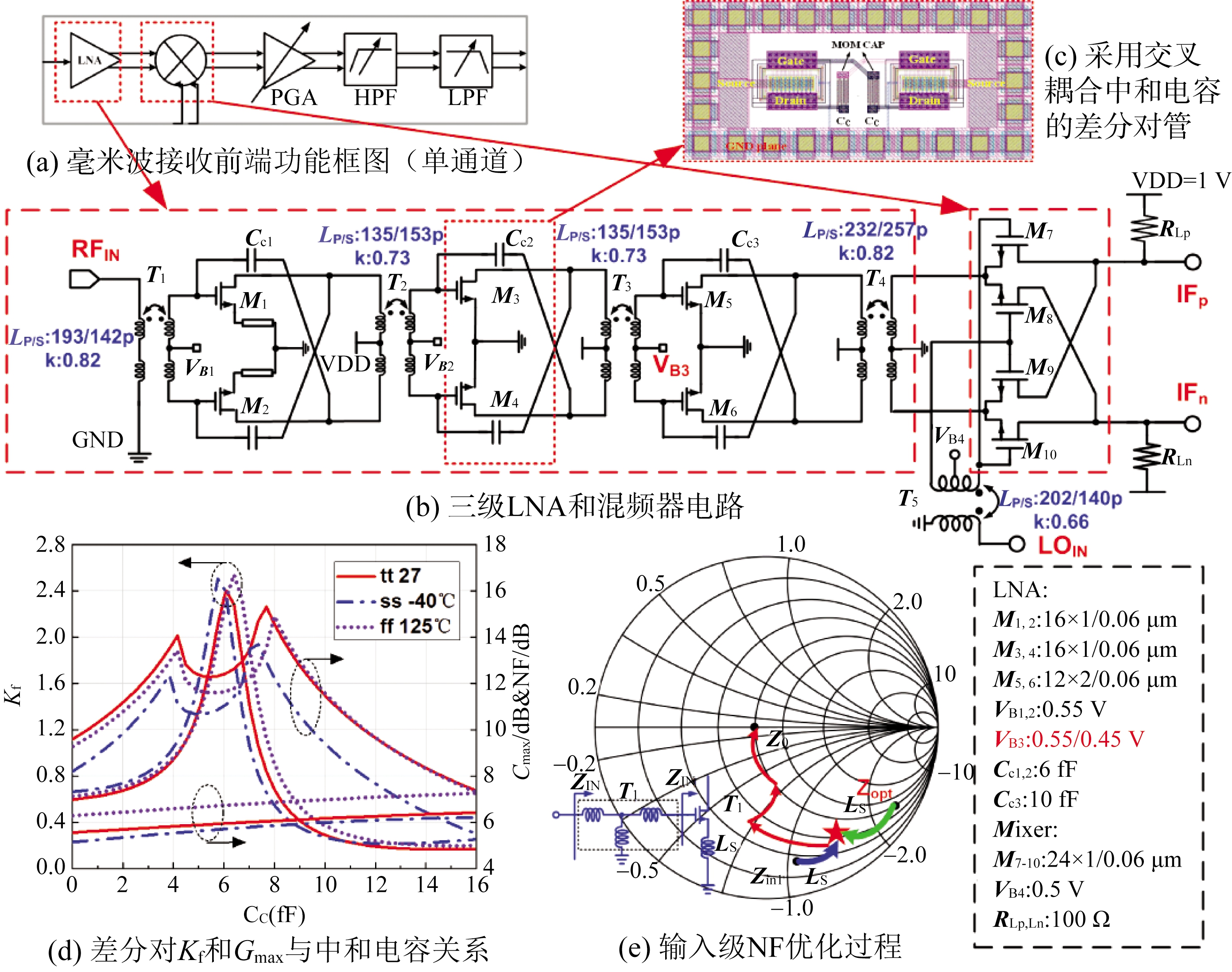

)多通道毫米波接收前端功能框图如图4(a)所示,主要包括两大部分:毫米波混频前端和可配置模拟基带电路,其中毫米波混频前端如图4(b)所示,主要包括三级差分低噪声放大器(LNA)及有源混频器。

差分LNA采用中和电容的共源级结构,如图4(b)所示。其中第一级采用源极传输线结构同时实现了噪声和功率匹配,输入变压器实现单端转差分的巴伦,并且能够提供一定的ESD防护能力。每级放大电路包括两个中和电容CC通过MOS管的栅和差分对管的漏极相连形成一种类似交叉耦合的差分放大单元,抵消了由于寄生电容CGD造成的密勒效应,一方面提高了放大器的功率增益,另一方面通过CC电容优化了稳定系数Kf。图4(d)显示了在不同的工艺变化和温度下,LNA的NF,Kf和Gmax与CC1的关系,其中当CC变化±30%时,中和电容共源级放大器是无条件稳定的。本设计中,为了获得最佳的Kf和Gmax,三级中和电容取值分别为6,6和10 fF。而LNA通过片上变压器级联,达到级间阻抗匹配和级间隔直的目的。放大器差分对管的尺寸以及偏置电压的选取根据65 nm工艺下NFmin对应的最佳电流密度为0.15 mA/μm确定。图4(e)给出了LNA第一级NF和匹配优化的过程。

图4 毫米波混频前端

传统Gilbert混频器的线性度主要受输入差分对的跨导限制,在CMOS工艺低电压电压下制约更为明显。本文提出了一种取消输入差分跨导级的有源混频器以提升混频器的线性度,如图4(b)所示。LNA的差分输出通过级间的变压器直接与吉尔伯特单元的开关对(M7-10)相连。级间变压器T1的次级线圈的中心抽头接地,提供混频器开关管源级共模点,次级线圈同时作开关对的源极带电感的反馈用来提高线性度。取消传统混频器中差分Gm对的另一个好处是,Gm对管需要更大电流偏置以实现高输入1 dB压缩点,更大的功耗也会让混频器对温度敏感。输入级变压器T1同时提供4个开关的源极负反馈电感,从而实现低电压工作,确保更好的线性度并降低开关对闪烁噪声的贡献。

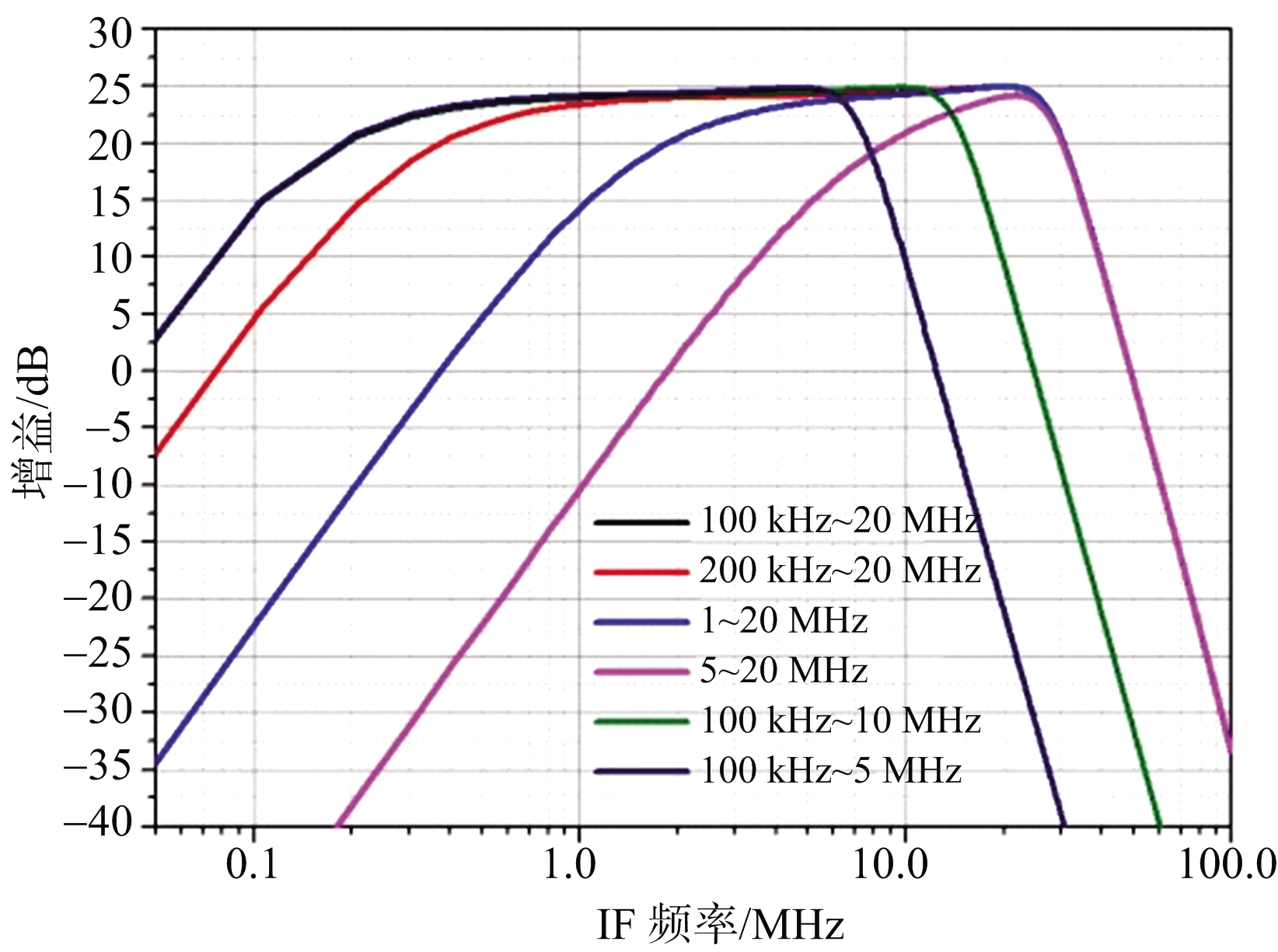

可配置模拟基带电路如图5所示,包括可编程增益放大器(PGA)、高通滤波器(HPF)、低通滤波器(LPF)等。多模汽车雷达应用要求模拟基带电路在增益和带宽方面可配置,以适应不同的应用场景。根据系统级设计指标,模拟基带电路的频率范围100 kHz~20 MHz,并可以实现0~42 dB的增益控制和100 kHz~20 MHz的3 dB带宽控制。为了增大输出IF信号摆幅,模拟基带电路的电源电压均为2.5 V。

图5(b)显示了本设计中的三级6 bit可编程放大器(PGA),通过改变反馈网络电阻设置反馈 系数,从而实现可变的增益,基于全差分运算放大器的闭环负反馈结构,放大器增益为

(7)

反馈电阻通过电阻阵列实现切换,该PGA的增益范围可以由式(5)得出电压放大倍数为1~128,即增益为0~42 dB。带电阻负反馈的闭环运放系统具有性能稳定且线性度高的特点,因此十分适用于高线性度的汽车雷达接收机。

通过信号流图的设计方法获得了二阶HPF的电路拓扑如图5(c)所示。本文提出了一种具有多反馈拓扑的二阶HPF,其传递函数可以表示为

(8)

本文所采用的LPF需要带外抑制Amin大于30 dB,通带允许最大衰减Amax为3 dB,fp和fs分别为10 MHz和20 MHz。可以计算出LPF所需的阶数n为4.98,则所需要的阶数为5阶,具体LPF的电路图如图5(d)所示。

图5 可配置模拟基带电路

2.2 毫米波发射机链路

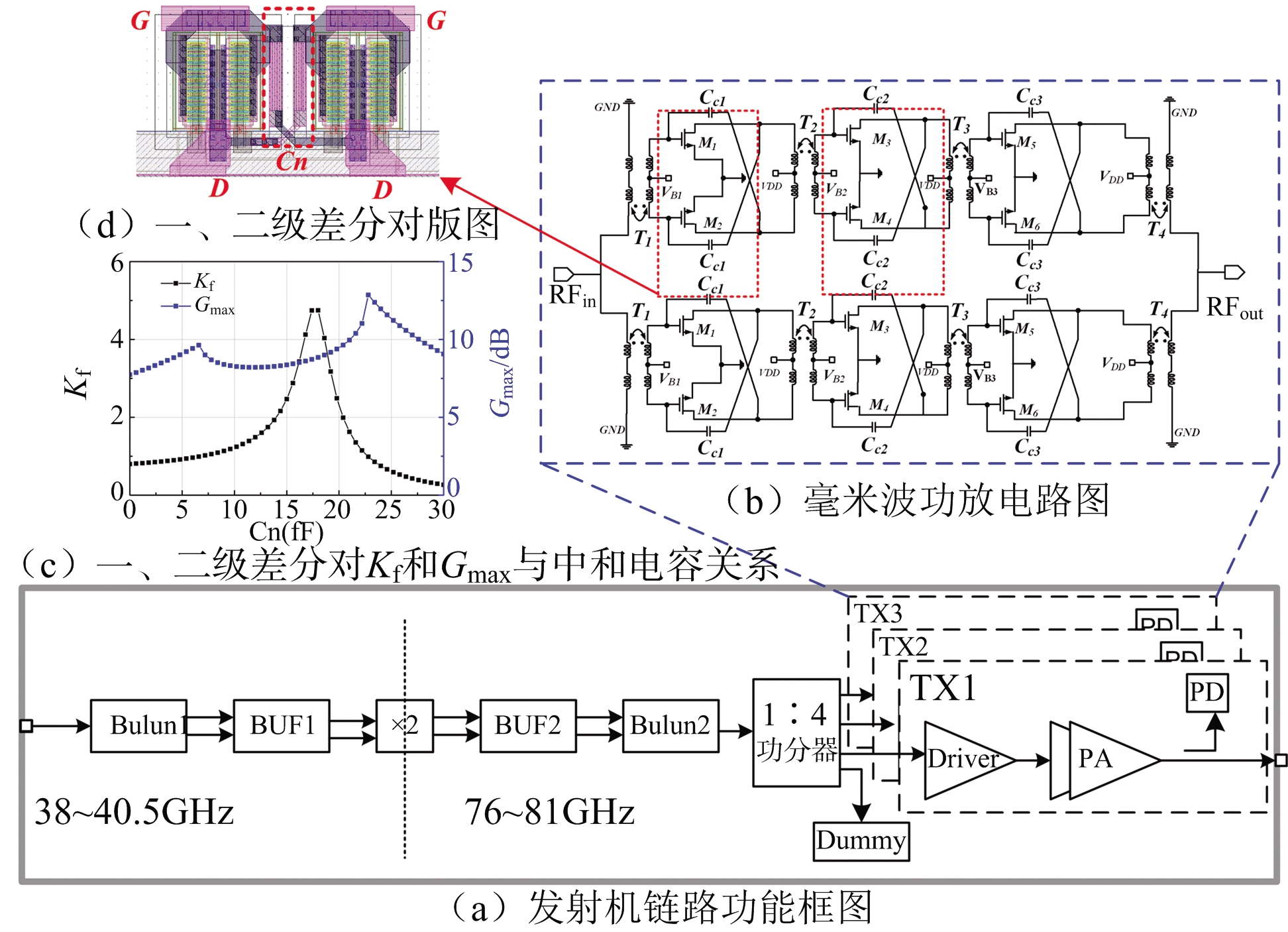

77 GHz毫米波发射前端主要包括倍频器、功分器和功率放大器等。图6(a)给出发射前端的功能框图。首先无源巴伦Balun1将本振分配网络送来的38~40.5 GHz单端信号转换为差分信号,经过第一级缓冲放大器BUF1后进入×2倍频器中。再经过第二个缓冲放大器BUF2后再进入第二个巴伦Balun2转换为单端信号。然后经过1∶4功分器后由1路信号转换为3路信号,分别通过驱动放大器Driver,最后送末级PA,再由PA放大至要求的输出功率大小,最终通过天线实现高输出功率发射。

图6 毫米波发射机

为克服CMOS工艺限制,基于变压器并联合成的片上功率合成技术,本文的PA采用3级放大,2路PA单元采用并联方式合成,各级之间采用变压器和传输线进行匹配,可实现高功率输出。PA电路如图6(b)所示。图6(c)显示了PA第一级和第二级的Kf和Gmax与中和电容Cn的关系,其中当Cn变化±30%时,中和电容共源级放大器是无条件稳定的。图6(d)是第一级和第二级差分对版图。

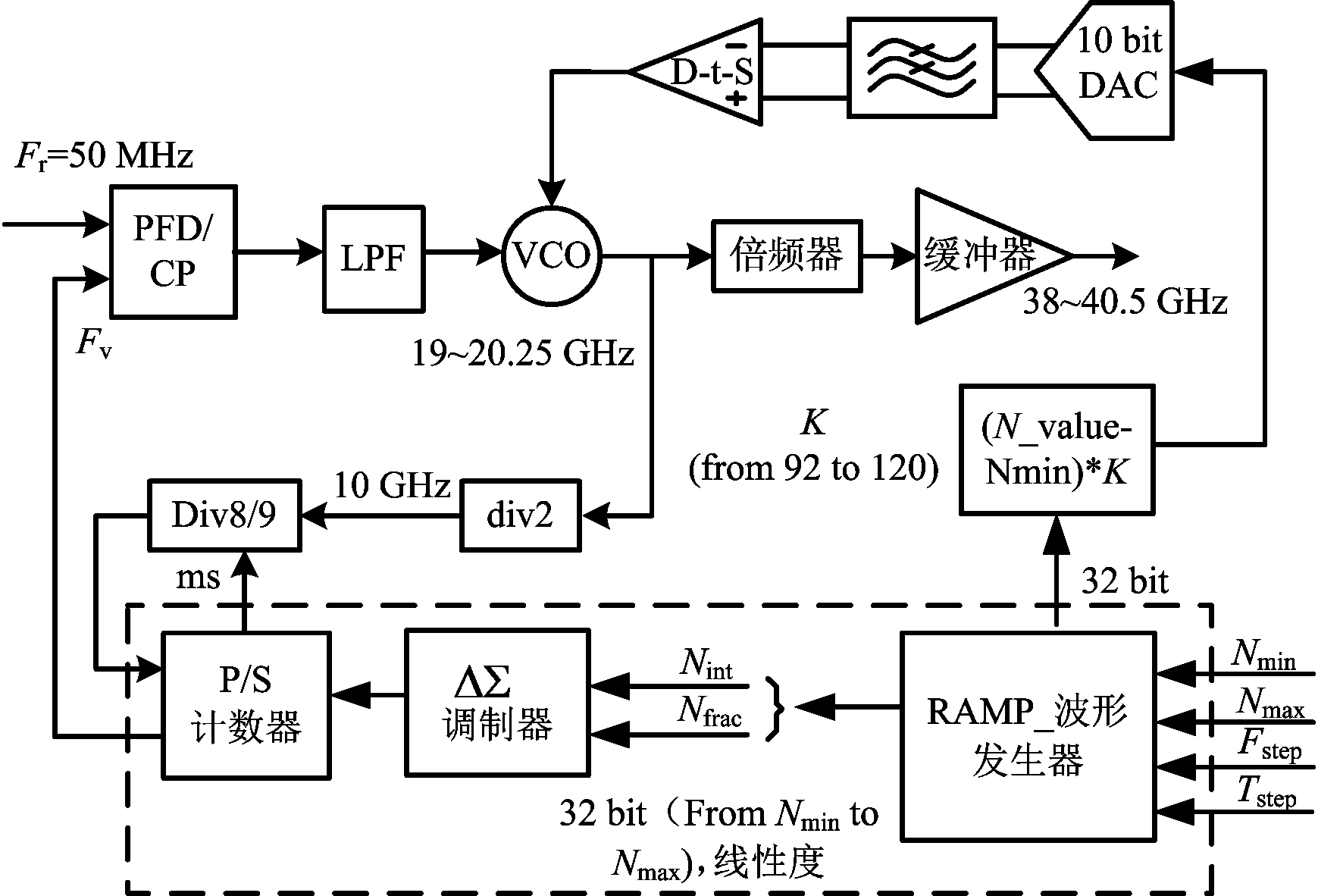

2.3 宽带快速FMCW信号发生器

从本振分配网络面积和倍频链路设计难度考虑,FMCW波形产生器输出为38.5 GHz频段,通过本振分配网络后,再进行二倍频至77 GHz的方案。然而,38.5 GHz频段电路寄生等对VCO影响较大,锁相环设计仍是难点,因此本设计中VCO振荡频率设计为19~20.25 GHz,再通过二倍频至38.5 GHz频段。图7给出了本文提出的FMCW波形发生器和分数锁相环的系统框图。设计基于两点调制锁相环,使锁相环控制不受环路带宽的约束,不失真地输出频率调制信号。整体FMCW波形发生器包括一个分数频率锁相环和chirp波发生器。分数频率锁相环包括一个除8/9的双模预分频器、固定除2分频器、P/S技术器、Δ-Σ调制器、压控振荡器(VCO)、鉴频鉴相器(PFD)、电荷泵(CP)等。参考时钟为50 MHz,VCO输出频率为19~20.25 GHz。其中锁相环系统采用两点调制模式,相较于传统的分数型锁相环,增加了由数模转换器(DAC)和低通滤波器(LPF)构成的调制支路。如此在增益匹配的情况下,输入到输出的传输函数呈全通特性。同时,在DAC模块后,加入LPF,滤掉输入信号的高频分量,可提高输出频率的线性度。

图7 FMCW波形产生器框图

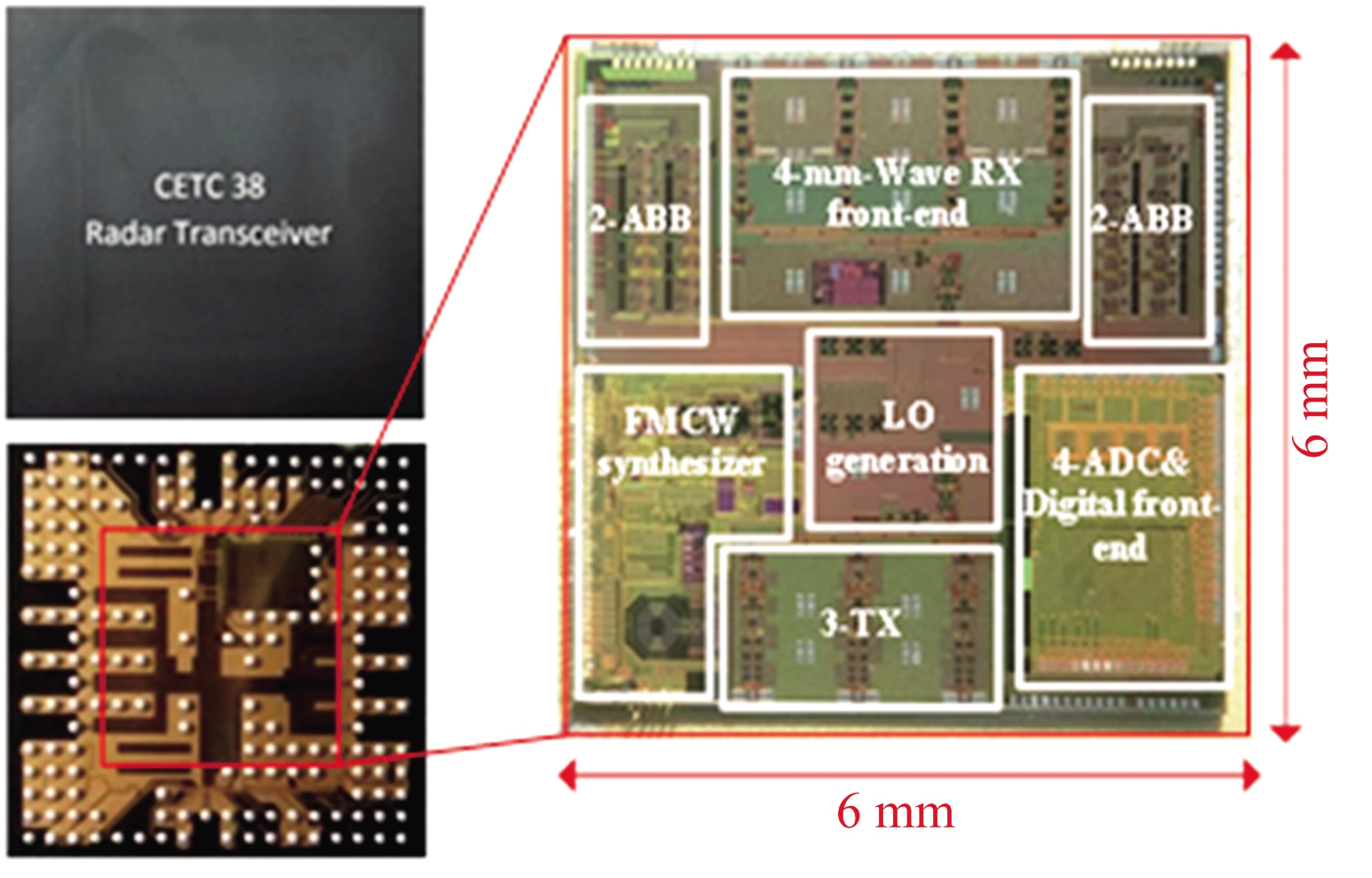

3 芯片实现与测试结果

本文设计的77 GHz多模毫米波雷达收发机芯片基于65 nm CMOS工艺实现,采用扇出型(fan-out)晶圆级封装,通过在芯片表面直接进行射频传输的再布线,将毫米波信号通过50 Ω共面波导结构以较低损耗传输出去。芯片与封装照片分别见图8。其中,裸芯片面积为6 mm×6 mm,封装芯片尺寸为10 mm×10 mm。

图 8 77 GHz毫米波收发机芯片照片

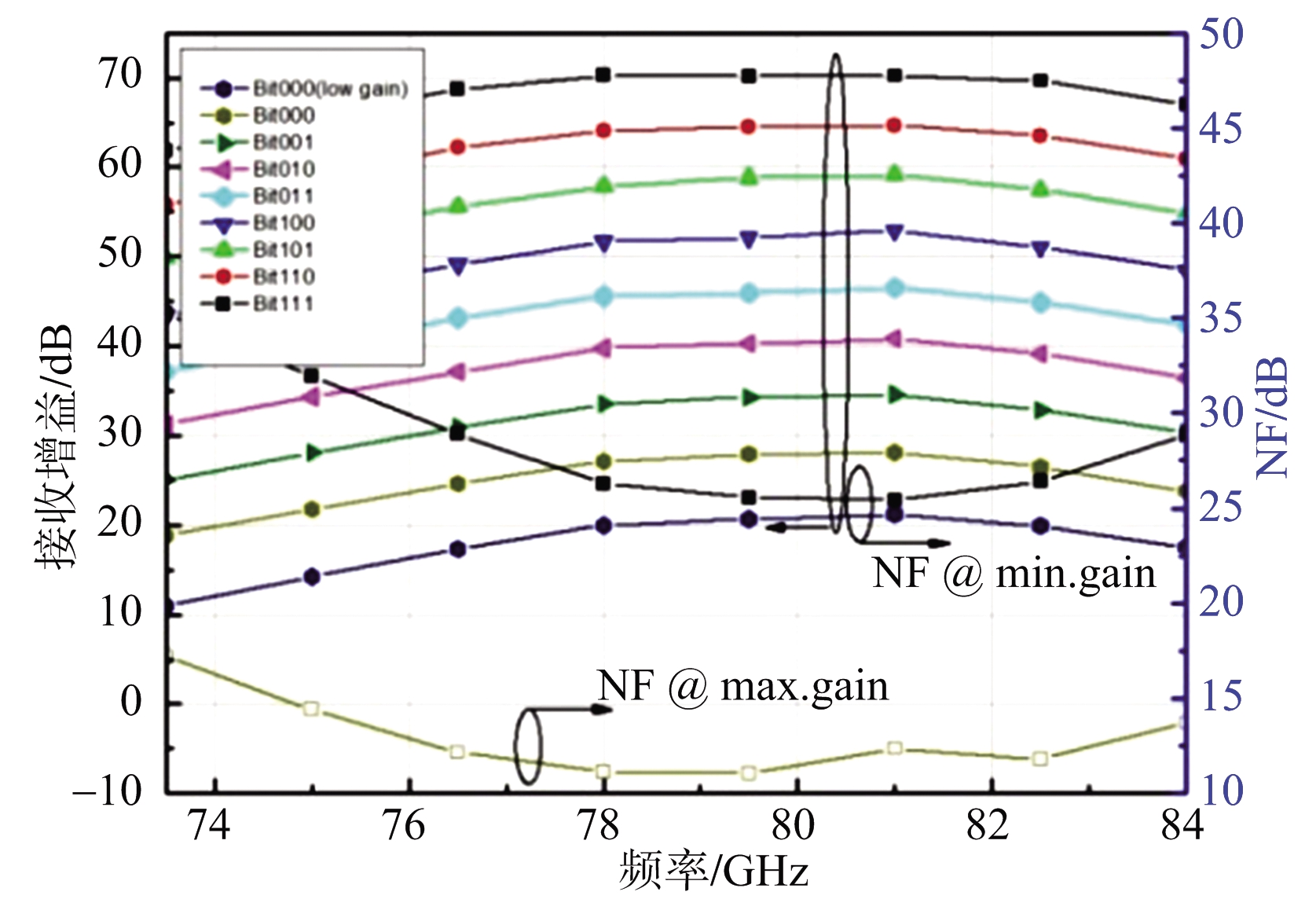

图9(a)给出了不同增益控制码下的接收增益以及最大和最小增益下的噪声系数的测试结果。通过调节PGA上的3 bit增益控制码,实现了42 dB增益控制,在此基础上,通过调节LNA的偏置电压,增益还可以继续减小约8 dB,将可调增益范围扩展至50 dB。最高增益时的噪声系数最小为11 dB,最低增益时,噪声系数最小为26 dB。图9(b)给出了接收机带宽的测试结果。测试结果显示接收机-3 dB带宽覆盖100 kHz/200 kHz/1 MHz/5 MHz到5 MHz/10 MHz/20 MHz,满足SRR/MRR/LRR多应用场景。

(a)增益控制和噪声系数

(b)中频带宽

图9 接收机测试结果

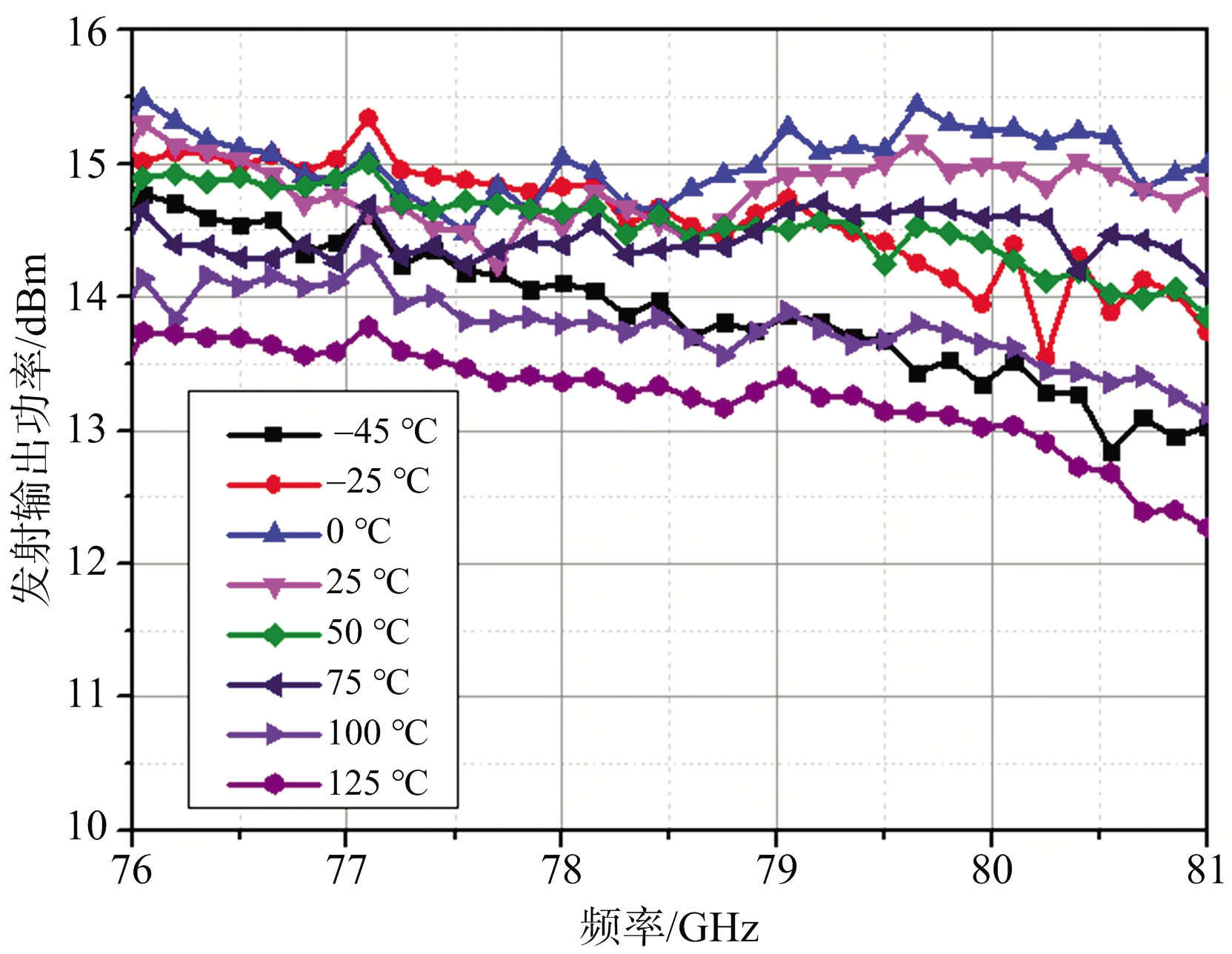

图10给出了-45~+125 ℃发射功率测试结果,结果显示76~81 GHz频率范围内发射功率最小为12.2 dBm,典型值大于13 dBm,起伏小于3.5 dB。

图10 不同温度下发射功率测试结果

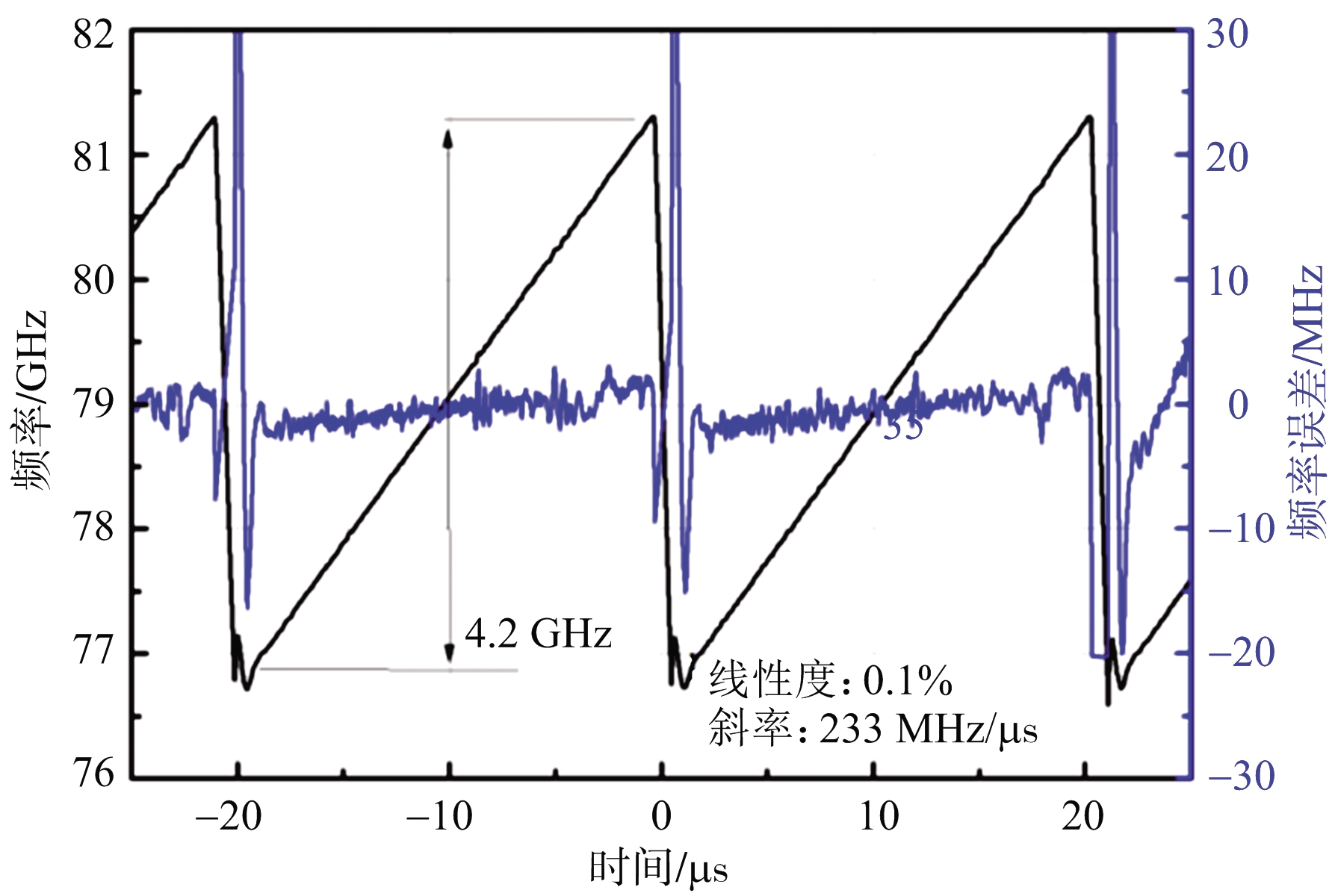

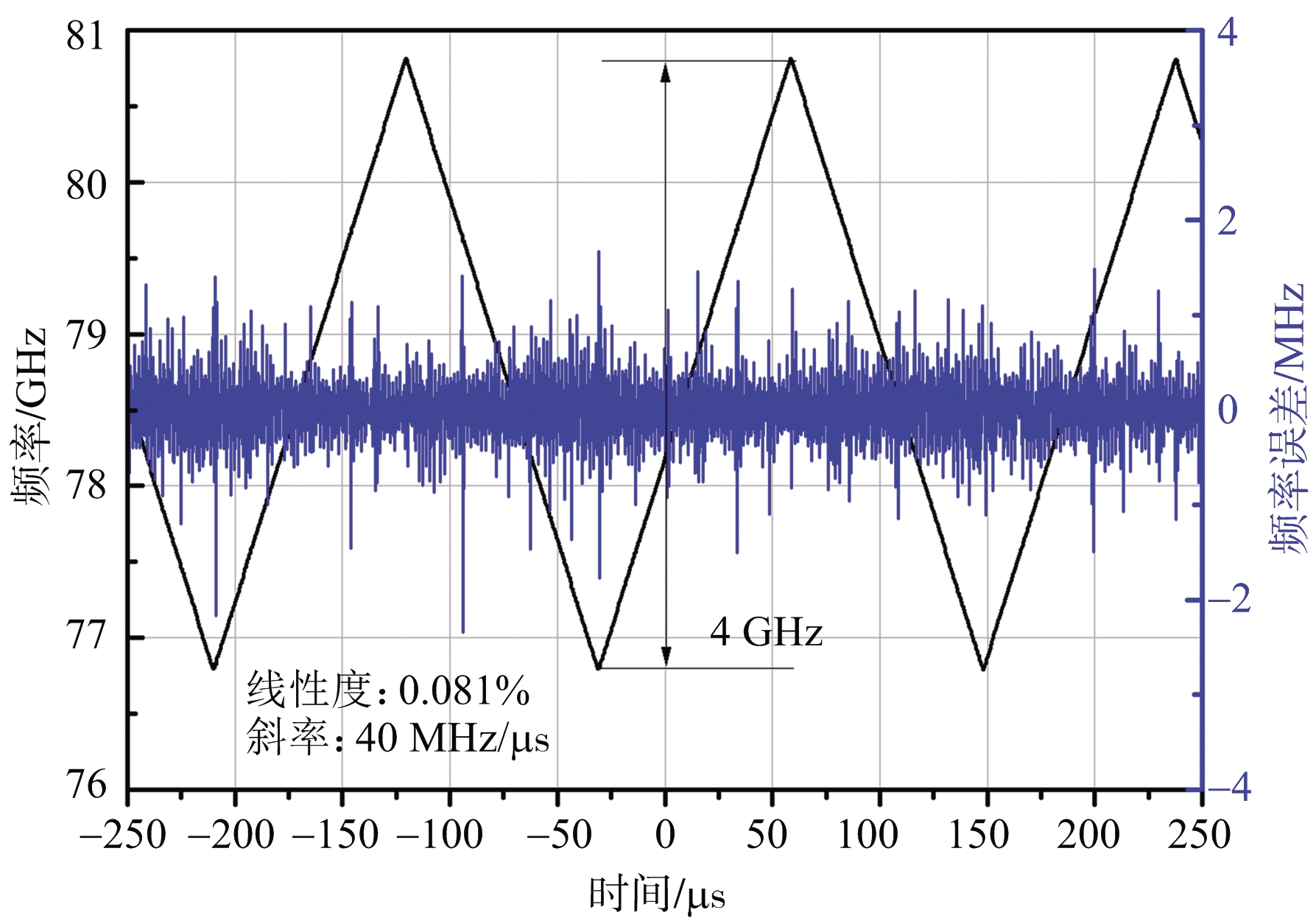

图11给出了FMCW chirp锯齿波和三角波调制波形。在锯齿波情况下,FMCW chirp信号调频带宽最大为4.2 GHz,最大调频速率达到233 MHz/μs,线性度0.1%。三角波情况下,FMCW chirp信号调频带宽最大为4.0 GHz,最大调频速率达到40 MHz/μs,线性度0.081%。

(a)锯齿波测试结果

(b)三角波测试结果

图11 FMCW chirp测试结果

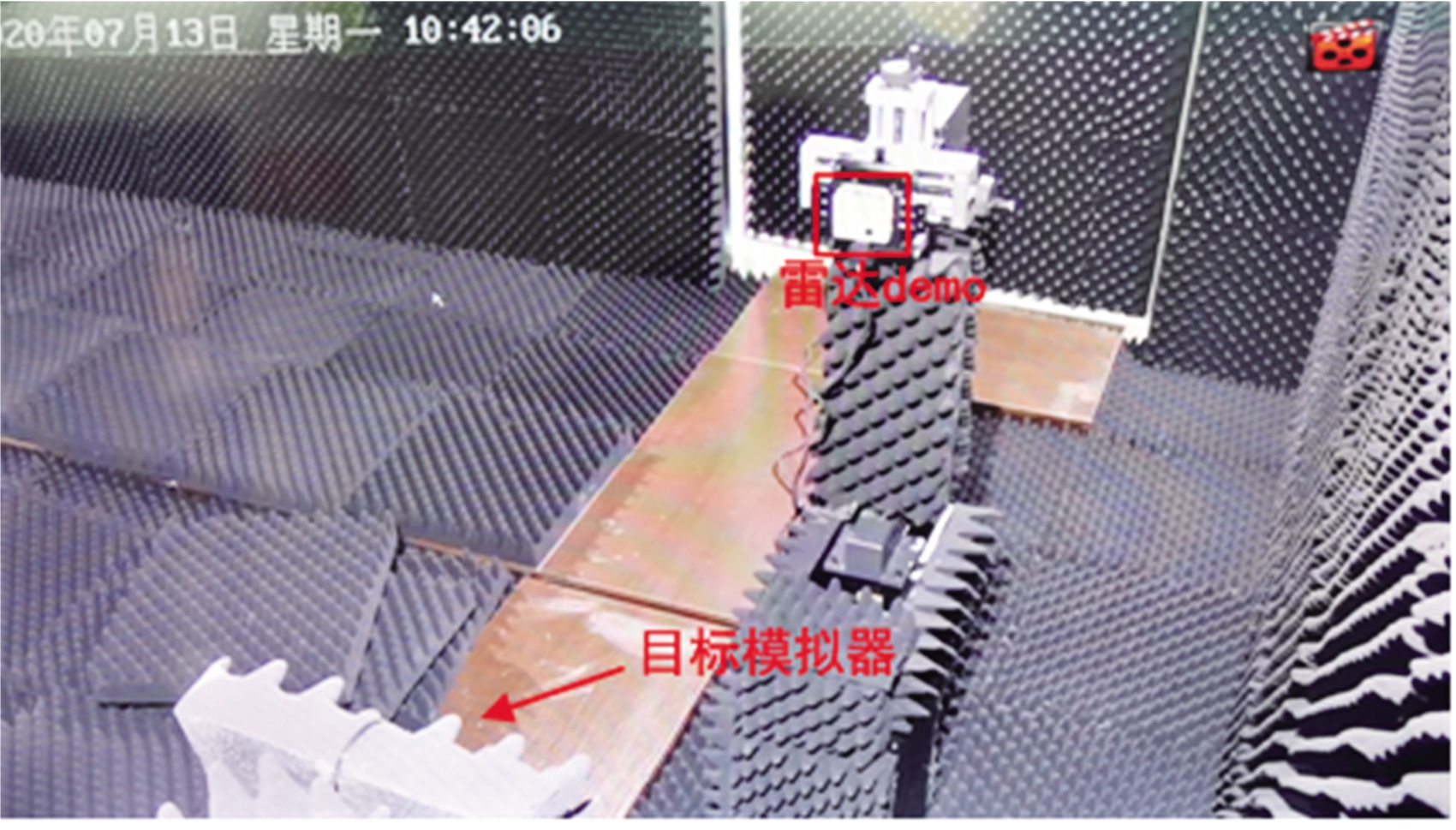

基于本文的毫米波芯片,完成应用于盲区检测(BSD)雷达的射频前端板级系统设计,并利用雷达模拟测试系统进行了测试,如图12所示。测试结果表明,77 GHz毫米波雷达在10~70 m距离范围内,最大测量误差为0.48 m; 0~85 km/h速度范围内,最大测量误差为0.32 km/h, 显示了很高的测距和测速精度。

图12 微波暗室雷达测试现场

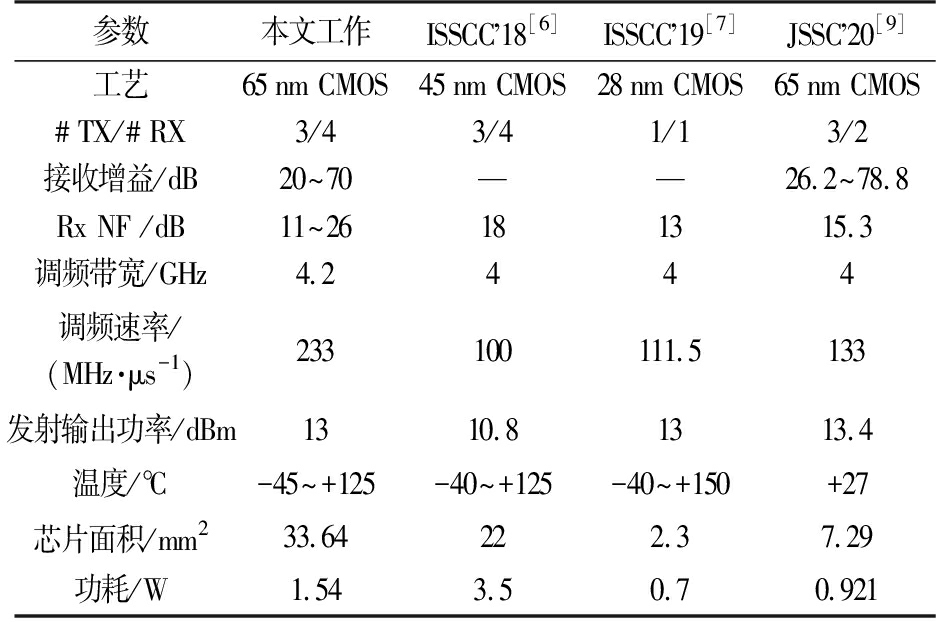

表1列出了本文设计的收发机指标总结以及与国际最新研究工作对比。可以看出,本文设计并实现的77 GHz毫米波芯片达到了较高的集成度,FMCW调制速度和带宽优于其他工作,收发通道参数可配置,满足未来高级别智能驾驶对毫米波传感器多模式、多场景感知需求。

表1 收发机指标总结及与文献工作对比

参数本文工作ISSCC 18[6]ISSCC 19[7]JSSC 20[9]工艺65nm CMOS45nm CMOS28nm CMOS65nm CMOS# TX/# RX3/43/41/13/2接收增益/dB20~70——26.2~78.8Rx NF /dB11~26181315.3调频带宽/GHz4.2444调频速率/(MHz·μs-1)233100111.5133发射输出功率/dBm1310.81313.4温度/℃-45~+125-40~+125-40~+150+27芯片面积/mm233.64222.37.29功耗/W1.543.50.70.921

4 结束语

本文提出了一种面向智能驾驶的77 GHz毫米波收发机芯片设计与实现。该芯片采用65 nm CMOS工艺,集成了3发4收、FMCW发生器、模数转换器及高速数据接口等电路。利用交叉耦合中和电容技术提升了CMOS工艺上毫米波低噪声放大器、毫米波片上功放等电路性能,采用两点调制锁相环技术提升了FMCW信号带宽和调制速率。收发机的发射功率、波形样式、接收增益和带宽等参数具有较好的可配置性,满足未来多模式、小型化和低成本汽车雷达传感器需求。

[1]HASCH J.Driving Towards 2020: Automotive Radar Technology Trends[C]∥IEEE MTT-S International Conference on Microwaves for Intelligent Mobility, Heidelberg, Germany: IEEE,2015:1-4.

[2]KAWANO Y, SUZUKI T, SATO M, et al.A 77 GHz Transceiver in 90 nm CMOS[C]∥IEEE International Solid-State Circuits Conference, San Francisco, CA, USA: IEEE,2009:310-311.

[3]LI Yian, HUNG M H, HUANG S J, et al.A Fully Integrated 77 GHz FMCW Radar System in 65 nm CMOS[C]∥IEEE International Solid-State Circuits Conference, San Francisco, CA: IEEE,2010:216-217.

[4]JIA Haikun, KUANG Lixue, ZHU Wei, et al.A 77 GHz Frequency Doubling Two-Path Phased-Array FMCW Transceiver for Automotive Radar[J].IEEE Journal of Solid-State Circuits,2016,51(10):2299-2311.

[5]GUERMANDI D, SHI Qixian, DEWILDE A, et al.A 79-GHz 2×2 MIMO PMCW Radar SoC in 28-nm CMOS[J].IEEE Journal of Solid-State Circuits,2017,52(10):2613-2626.

[6]GINSBURG B P, SUBBURAJ K, SAMALA S, et al.A Multimode 76-to-81 GHz Automotive Radar Transceiver with Autonomous Monitoring[C]∥IEEE International Solid-State Circuits Conference, San Francisco, CA: IEEE,2018:158-160.

[7]HUNG C, LIN A T, PENG B, et al.9.1 Toward Automotive Surround-View Radars[C]∥IEEE International Solid-State Circuits Conference, San Francisco, CA, USA: IEEE,2019:162-164.

[8]DUAN Zongming, PAN Dongfang, WU Bowen, et al.A 76-81 GHz FMCW Transceiver with 3-Transmit, 4-Receive Paths and 15dBm Output Power for Automotive Radars[C]∥IEEE Radio Frequency Integrated Circuits Symposium, Boston, MA, USA: IEEE,2019:39-42.

[9]MA Taikun, DENG Wei, CHEN Zipeng, et al.A CMOS 76-81-GHz 2-TX 3-RX FMCW Radar Transceiver Based on Mixed-Mode PLL Chirp Generator[J].IEEE Journal of Solid-State Circuits,2020,55(2):233-248.

[10]PAN Dongfang, DUAN Zongming, WU Bowen, et al.A 76-81-GHz Four-Channel Digitally Controlled CMOS Receiver for Automotive Radars[J].IEEE Trans on Circuits and Systems I: Regular Papers,2020,68(3):1091-1101.