0 引言

随着相控阵技术的飞速发展,相控阵雷达已然成为当今雷达的重要方向,其能够实现多目标跟踪、多波束扫描、指向灵活、可靠性高等优势,广泛应用于星载、弹载、机载、舰载雷达及地面预警、跟踪雷达与电子对抗、汽车防撞雷达等军民领域[1-2]。数字阵列雷达(DAR)是将数字技术和雷达阵列技术进行完美结合,在发射和接收模式下均以数字波束形成(DBF)取代传统模拟波束形成(ABF)。数字阵列模块将射频收发单元、本振功分单元、中频数字收发单元等功能电路一体化设计,作为数字阵列雷达的核心组成部分,其演进发展使得雷达阵列系统具有鲁棒、可扩充、可重构等特性,从而更好地应用于不同的领域和作战平台[3]。射频收发单元作为数字阵列模块的重要组成部分,数量众多,深入研究其性能指标、集成度、可靠性、可制造性,对数字阵列雷达技术发展具有重要意义。

伴随着电路及封装技术的飞速发展,系统级封装(SiP)技术作为一种新颖的封装技术应运而生,其定义为将一个或者多个具有不同功能的IC芯片及各种电子元器件整个在同一封装中,形成单个具有功能齐全的系统或者子系统[4-6]。相比于传统的封装技术,SiP技术具有多功能、高集成、成本低、高生产效率及简化系统设计等优点,在国内外掀起一股热潮。

Yeo等人设计了一款相控阵雷达X波段收发组件[7],该组件采用3D多层封装技术集成了射频收发电路与无源传输结构,尺寸仅为20 mm×20 mm×3.7 mm。在 0.1~10 GHz 插入损耗小于1.5 dB,回波损耗小于-13.5 dB,整体收发组件最大输出功率为39.8 dBm,发射增益为41 dB,接收增益为19.2 dB,噪声系数为6.3 dB。

吴喆等人设计了一款电路面积30 mm×30 mm的变频宽带收发前端模块[8],基于SiP技术和HTCC基板集成了收发支路和本振支路。测试结果得出接收频率为100~3 500 MHz,功率-100~0 dBm,输出功率大于-2 dBm,小信号噪声系数低于5 dB,杂散抑制度大于20 dBc,发射支路输出功率大于12 dBm。

武红玉等人研制了一种40 mm×40 mm×10 mm的S频段变频收发SiP模块[9]。模块主要的测试结果为接收通道动态范围-100~-40 dBm,输出信号0~2 dBm,噪声系数小于等于2.8 dB,带外抑制大于等于50 dBc;发射通道输出信号大于等于2 dBm,杂波抑制大于等于55 dBc。

本文设计了一款集成S波段和P波段的四通道变频SiP,满足高集成、多通道及多种工作状态切换的需求,希望对相关的工程应用和设计研究提供一定帮助。

1 双频段四通道变频SiP设计

本文中的双频段四通道变频SiP为了数字阵列模块射频电路部分的多功能和多通道集成提供了良好的解决途径,使得数字阵列模块的组成清晰,降低了系统的复杂度,便于调测、组装、维修和试验。双频段四通道变频SiP采用超外差接收原理,利用本振信号在内部变频器中完成前端射频收发与中频数字收发的信号频率转换功能,并且具有信号放大的功能,满足各级接口的工作电平需求,多通道的设计需要在高集成小型化的同时保证较高的通道间隔离度。

超外差式接收机变频器,在本振(LO)信号的作用下,把射频(RF)信号变成中频(IF)信号,这个过程可用调谐方程,即公式(1)来表示:

|m×fLO±n×fRF|=fIF

(1)

式中:m,n为正整数,表示谐波的次数;fLO为本振LO的频率,fRF为输入射频RF信号的频率,fIF为中频的频率。当m,n都等于1时,就可得到最基本的调谐方程式:

|fLO±fRF|=fIF

(2)

式中,fLO信号频率的连续可变就可以把较宽的fRF输入信号频率范围混频到固定的fIF信号频率,同时,对于一定的fIF信号频率和fLO信号频率,就会对应存在fimg镜像信号频率,在实际的电路设计中,我们采用镜像抑制混频器和镜像抑制滤波器来实现镜像干扰抑制。

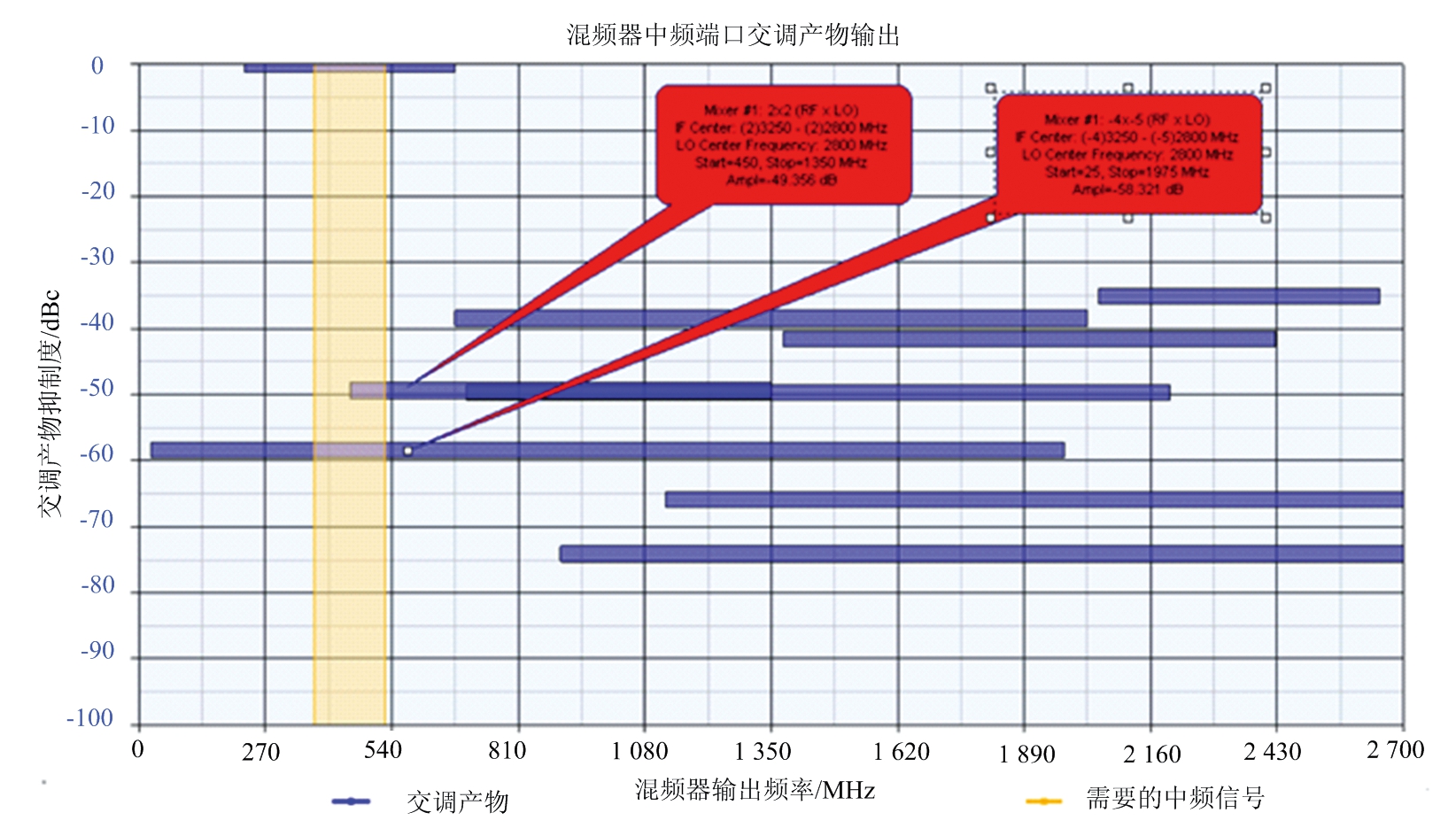

从公式(1)中,混频器除了输出所需要的频率外,还有产生许多其他的频率组合分量,其中m,n为正整数。除了所需要的频率之外,其他频率的信号一般都叫做虚假信号或者寄生信号,经过Genesys软件仿真,混频器输出工作频率窗口仿真结果如图1所示,具体电路设计中采用双平衡混频器,对偶次混频可实现较高的抑制度,所以可满足系统使用需求。

图1 混频器输出工作频率窗口仿真结果

1.1 SiP电路设计

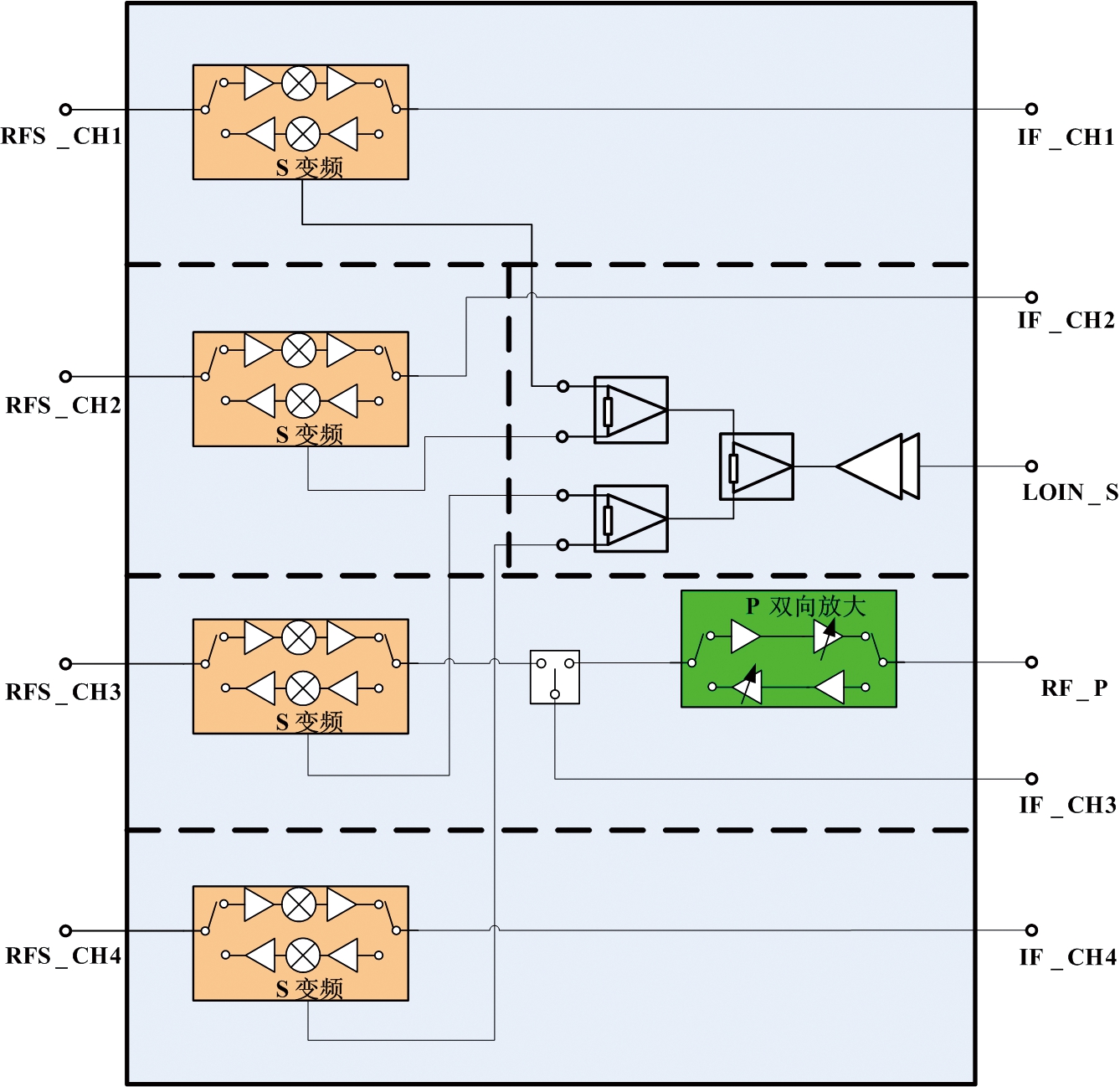

本文涉及的SiP采用双频段四通道一体化设计,集成4路S波段变频和1路P波段双向放大,S波段变频通道3和P波段放大共用中频接口,另外集成了低压差稳压器(LDO),本振放大和功分电路,SiP完整的功能框图如图2所示。SiP一共有多个控制端口,其中2个为LDO芯片的使能控制, 4个S变频芯片的收发切换及增益控制,5个控制P双向放大芯片的收发切换及增益,1个控制第三通道工作模式,可选择P双向放大或S变频收发。在通道之间利用金属隔墙独立分腔实现了高隔离度设计。

图2 双频段四通道变频SiP功能框图

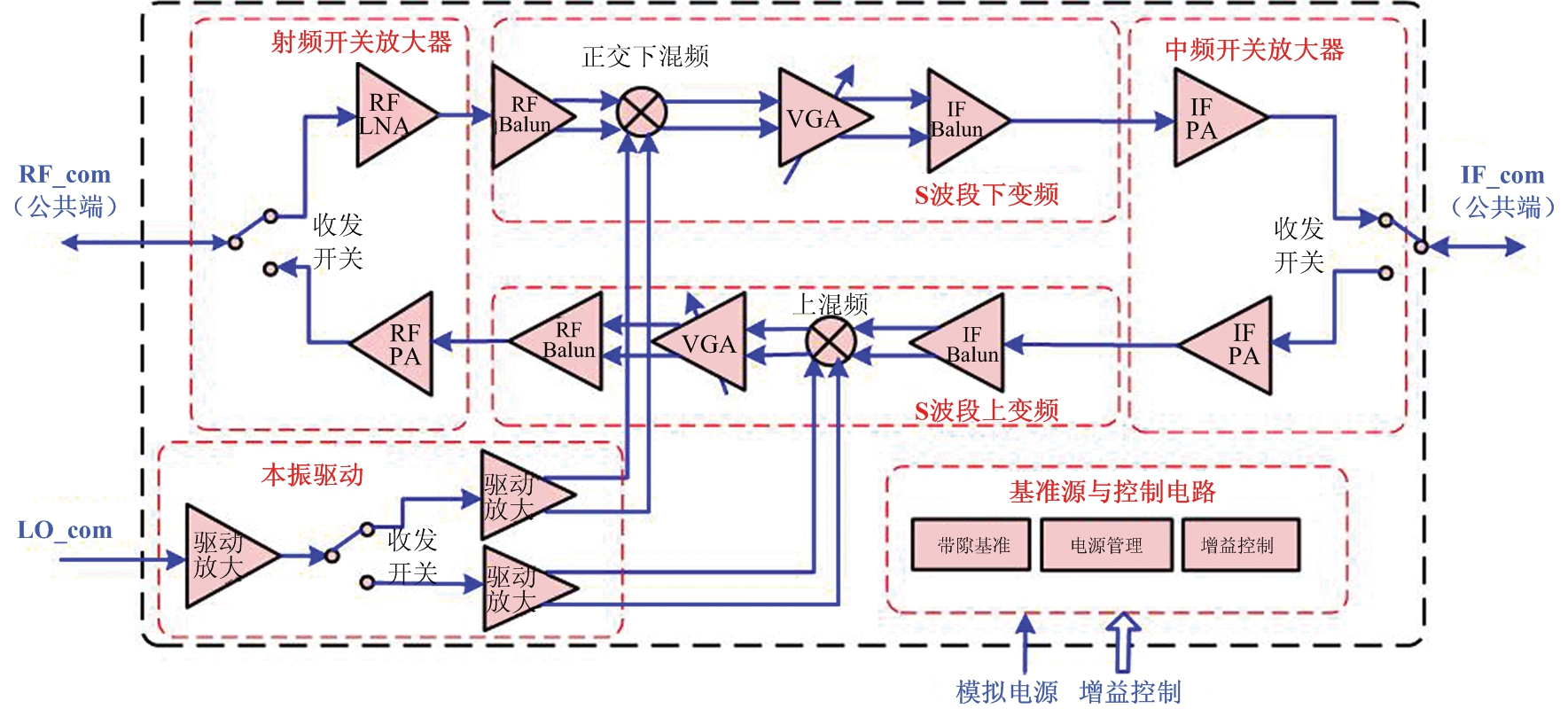

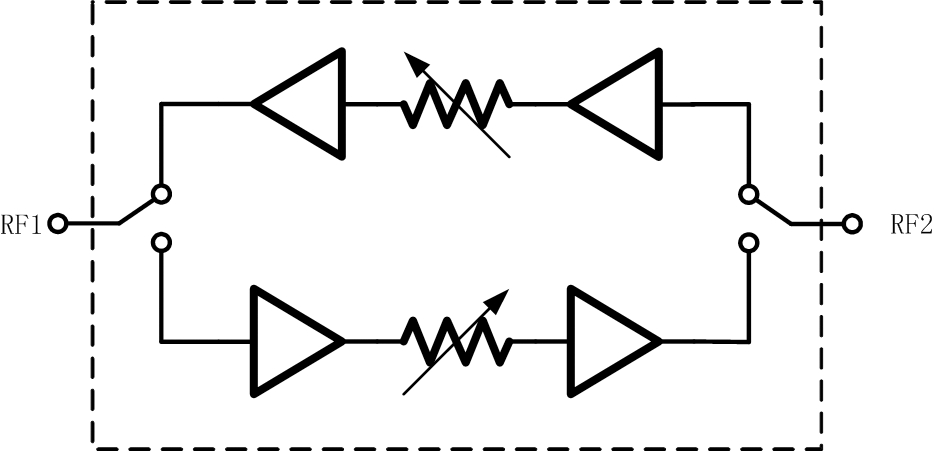

双频段四通道变频SiP内部主要功能芯片包括S波段变频多功能芯片和P波段双向放大器芯片。S波段变频多功能芯片的收发通道分别集成了收发开关、低噪声放大器、上变频器、下变频器、可变增益放大器和驱动放大器等多个射频单元,RF频率为S波段,中频为P波段,其芯片电路功能框图和增益曲线如图3所示。

(a) 原理框图

(b) 增益频响曲线图

图3 S波段变频多功能芯片原理框图和增益频响曲线图

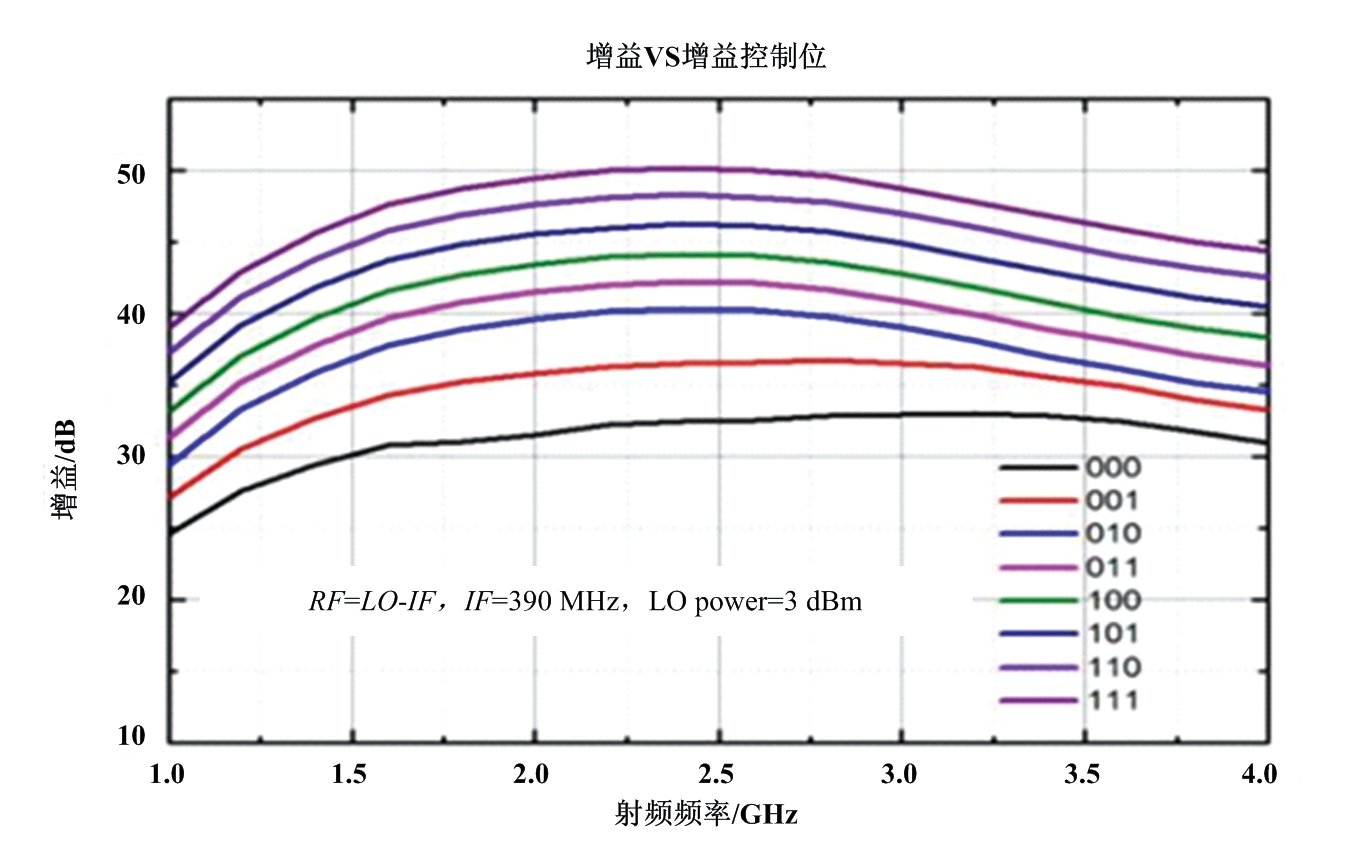

P波段双向放大器芯片集成了低噪声放大器、数控衰减器、驱动放大器、开关等单元电路,具有较高的集成度,工作频率为P波段,增益为38 dB,输出1 dB压缩点17 dBm。其原理框图如图4所示。

图4 P波段双向放大器芯片原理框图

SiP其余部分选用的放大器、功分器、开关等芯片,这里就不一一赘述了。

1.2 SiP封装设计

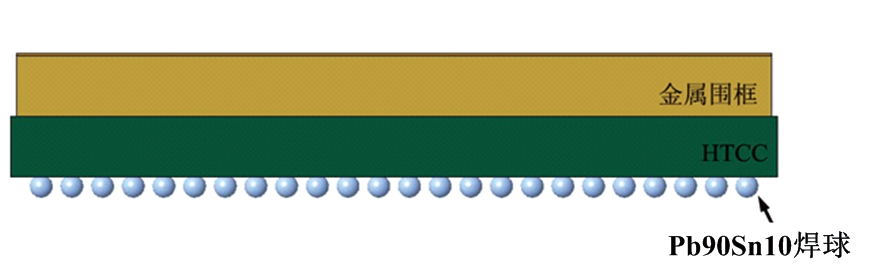

球栅阵列(Ball Grid Array,BGA)封装技术具有高的封装密度,同时又具有优良的电性能、低噪声、低寄生电感电容等优点,在高速PCB 设计中得到广泛的使用,针对射频SiP封装互联密度高、高频传输性能要求高、可靠性高、重量轻等需求,大量采用球栅阵列(BGA)的封装形式,BGA按封装基板材料分主要有4 种基本类型:PBGA、EBGA、CBGA 和TBGA。为满足灵活多层布线、气密封装、低传输损耗、高散热性能、高可靠性等需求,采用高温共烧陶瓷(HTCC)基板作为封装基板,通过基板内部垂直信号互连和芯片的堆叠集成,高温焊接可伐(Kovar)金属围框,平行缝焊盖板完成气密封装,即陶瓷焊球阵列封装(CBGA)。双频段四通道变频SiP采用气密性优良的CBGA金属陶瓷封装,平面尺寸为20 mm×25 mm,引脚形式为BGA引脚,BGA球直径为0.65 mm,焊球间距为1 mm,共包含452个引脚。其中厚度为2.0 mm的陶瓷基板选用高温共烧陶瓷(HTCC)基板,优势在于制作成本较低,与PCB板的热匹配性较好。图5展示了双频段四通道变频SiP的剖面示意图。

图5 双频段四通道变频SiP结构的剖面示意图

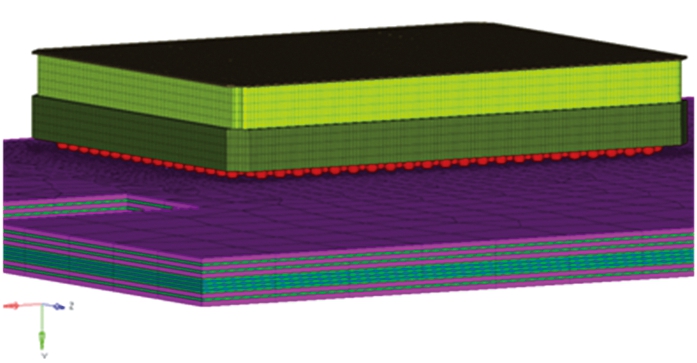

将变频SiP实际结构与载荷条件进行同步的仿真,图6展示出器件的仿真模型与焊球应力仿真结果,仿真结果表明器件最边缘的焊球应力最大,从中心位置沿边缘焊球应力逐渐增大。据研究表明,CBGA焊点的剪切应变往往影响着焊点的应力与形变,而剪切应变又被多个参数所控制,参考如下公式[10]:

![]() TΔα

TΔα

(3)

式中,γ表示焊点的最大剪切应变,L表示焊点到中心的距离(DNP),H表示焊点的高度,Tmax表示试验最高温度,Tmin表示试验最低温度,ΔT表示最高温与最低温之差,αb、αc分别表示PCB与SiP器件的热膨胀系数,Δα表示热膨胀系数之差。从式中可以看出当温差、热膨胀系数差和焊点高度一定时,距离中心点越远的焊点剪切应变越大,应力越大,焊球越容易变形,与试验和仿真结果相吻合。

(a) 仿真模型

(b) 焊球应力仿真结果

图6 变频SiP器件仿真模型及焊球应力仿真结果

2 电性能测试与可靠性验证

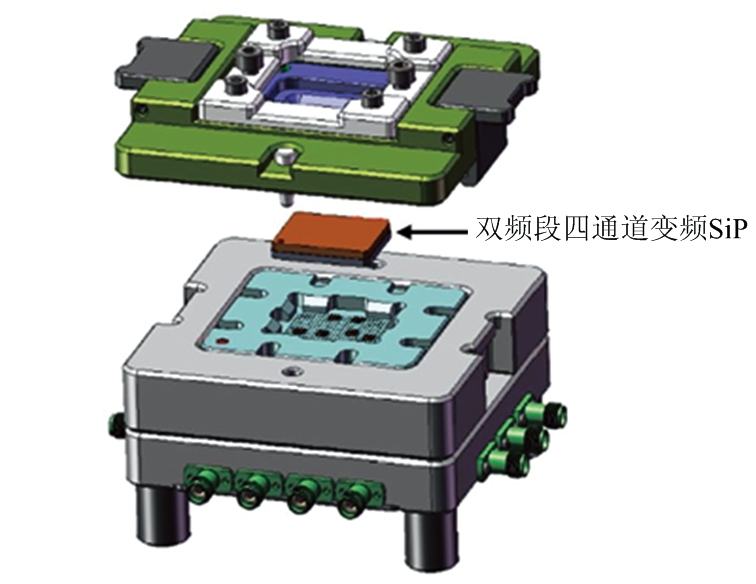

最终设计加工完成的双频段四通道变频SiP实物图如图7所示。

图7 双频段四通道变频SiP实物图

2.1 SiP电性能测试

针对双频段四通道变频SiP的封装形式,定制专用测试夹具,完成射频信号和低频信号从封装接口到可测试接口的适配与转换,使用效果图如图8所示。

图8 双频段四通道变频SiP测试夹具效果图

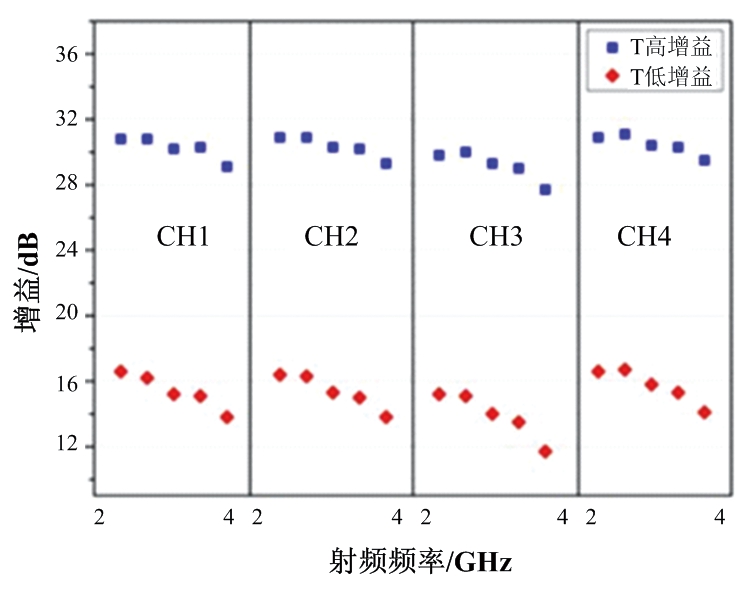

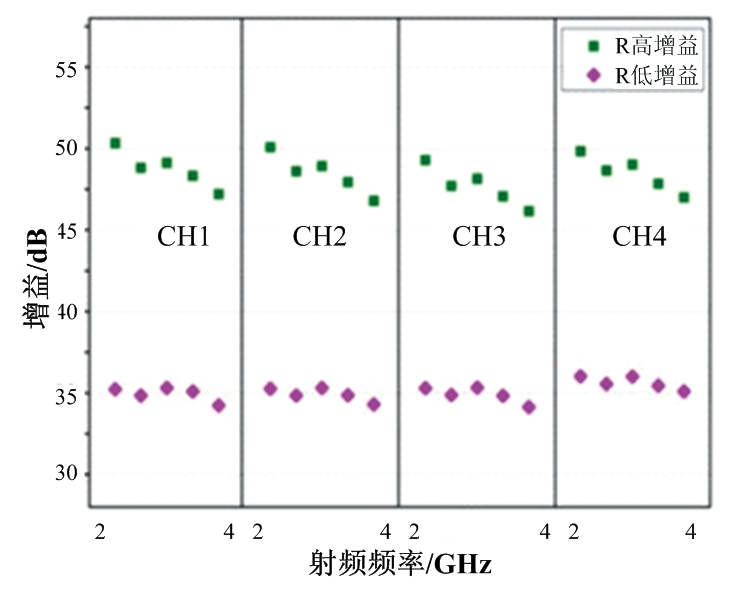

双频段四通道变频SiP共有4种工作状态,即发射高增益状态、发射低增益状态、接收高增益状态及接收低增益状态,通过P双向放大功能和S变频芯片功能的控制码进行调整控制,试验针对SiP在不同工作状态下对其进行性能测试验证。图9(a)展示了S波段发射状态下SiP 4个通道在工作频率范围内各频点的增益图,横坐标5个频点工作频率从左往右依次升高,从图中可以看出,4个S波段通道的发射高增益值在30 dB左右,发射低增益值在14 dB左右。与此同时,图9(b)展现了接收状态下SiP 4个S波段通道在工作频率范围内各频点的增益图,横坐标5个频点工作频率Flow到Fhigh从左往右依次升高,4个通道在各频点的接收高增益值在48 dB左右,接收低增益值在35 dB左右。在接收状态下高增益和低增益的平坦度分别为3.3和1.2 dB。在S波段发射状态下SiP四通道的增益平坦度测试结果显示,高增益下的平坦度值较小。在S波段接收状态下SiP四通道的增益平坦度测试,高低增益下平坦度一致性较好,四通道的高低增益平坦度差异在于相比于低增益状态,高增益状态下其波动性相应增大。

(a) 发射状态

(b) 接收状态

图9 S波段发射状态和接收状态下SiP四通道各频点的增益图

S波段相邻通道间隔离度大于42 dB,P波段接收增益29 dB, P波段发射增益30 dB, 输出P-1 dB大于17 dBm,各频段各通道信号输出信杂比均大于65 dB,满足系统的电性能指标要求。

2.2 SiP板级可靠性验证

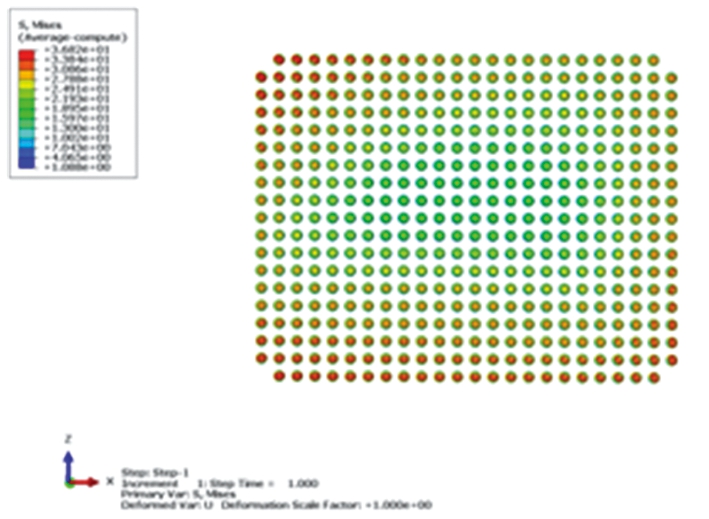

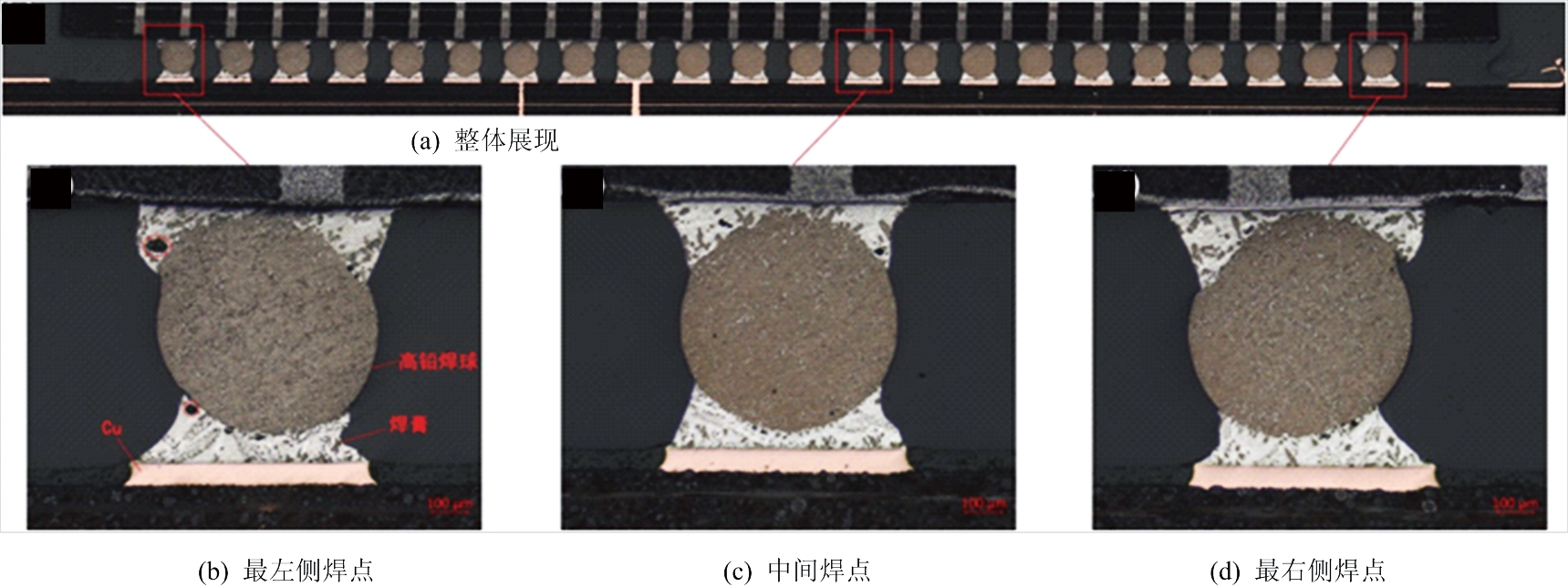

双频段四通道变频SiP通过CBGA方式装配在PCB板上,为了确保整个器件在使用环境下能达到可靠的效果,需要对其进行可靠性试验检测,常见的方法有温度循环试验,其目的是考核和验证器件承受极端高温、极端低温的能力,以及极端高温和低温交替变化对器件的影响。参照JESD22-A104-B的标准[11],本次温度循环试验设计为-55~125 ℃的温度范围,升降温速率10 ℃/min,最高温度和最低温度各保持15 min,每个周期约占1 h。

采用破坏性物理分析(DPA)方法将经历 100次温度循环试验后的变频SiP器件沿边缘切开,如图10所示,图10(a)整体展现出每个焊点的界面微观结构和形态,图10(b)显示的是器件最左侧焊点的放大图,图中高铅焊球未发生塌陷,上下端均被共晶焊膏包覆,爬锡效果较好。焊球—陶瓷和焊球—PCB板之间产生良好的连接。图10(c)、(d)分别是中间焊点和最右侧焊点的放大结构图,相比于中间焊球,边缘的焊球发生了微小的变形,但焊点界面未产生裂纹,表明此时积累的热应力还没损坏焊点界面,裂纹并未萌生,可靠性较高。

图10 双频段四通道变频SiP器件温循100次DPA切片图

3 结束语

本文研制了一款基于CBGA封装技术的双频段四通道变频SiP模块。采用CBGA射频信号传输形式,缩短了信号传输路径,降低了信号传输驻波,一体化HTCC可伐隔金围框封装提高了通道间隔离度,又增强了结构稳定性,各项电性能测试结果满足设计要求,产品的一致性、可靠性、批量可制造性较高,适合工程大批量应用。随着三维高密度封装技术的发展,未来SiP的集成度水平将会继续提升。

[1] AFZAL M U, QURESHI A A, TARAR M A, et al. Analysis, Design, and Simulation of Phased Array Radar Front-End[C]∥ International Conference on Emerging Technologies, Islamabad, Pakistan:IEEE,2011:1-6.

[2] 邵正途, 朱和平, 郭建明,等. 多功能相控阵雷达在反导预警系统中的应用[J]. 火力与指挥控制, 2008, 33(S2):5-7.

[3] 吴曼青.数字阵列雷达的发展与构想[J]. 雷达科学与技术,2008,6(6):401-405.

WU Manqing. Development and Future Design of Digital Array Radar[J]. Radar Science and Technology,2008,6(6):401-405.(in Chinese)

[4] KAMGAING T, ELSHERBINI A A, OSTER S N, et al. Ultra-Thin Dual Polarized Millimeter-Wave Phased Array System-in-Package with Embedded Transceiver Chip[C]∥2015 IEEE MTT-S International Microwave Symposium, Phoenix, AZ :IEEE,2015:1-4.

[5] YU D C H. New System-in-Package (SiP) Integration Technologies[C]∥Proceedings of the IEEE 2014 Custom Integrated Circuits Conference, San Jose, CA,USA:IEEE,2014:1-6.

[6] HU L L, JIN Z, LIAO X J, et al. Study of 3D SiP (System-in-Package) Module for Package-on-Package Application Using Multi-Layer PCB Manufacturing Process[C]∥2014 15th International Conference on Electronic Packaging Technology, Chengdu, China:IEEE, 2014:109-112.

[7] YEO S K, CHUN J H, KWON Y S. A 3-D X-Band T/R Module Package with an Anodized Aluminum Multilayer Substrate for Phased Array Radar Applications[J]. IEEE Trans on Advanced Packaging, 2011, 33(4):883-891.

[8] 吴喆. 基于SIP的射频宽带收发前端关键技术研究[D]. 成都:电子科技大学, 2018.

[9] 武红玉, 厉志强, 汪江涛. 系统级封装的S频段射频收发模块研制[J].电讯技术, 2016, 56(5): 581-584.

[10] 张成敬, 王春青. 陶瓷阵列封装的两种形式及其接头可靠性[J]. 电子工业专用设备, 2006, 35(8):10-17.

[11] IPC SM-785. Guidelines for Accelerated Reliability Testing of Surface Mount Technology[S]. US:Institute for Interconnection and Packaging Electronic Circuits, 1992.