0 引 言

工作在W波段的毫米波成像雷达和通信系统因其高分辨率和高数据传输速率而受到越来越多的关注。2018年2月,联邦通信委员会(FCC)通过了在95 GHz以上的各种频段(包括 95~109.5 GHz 之间的4个频段)使用千兆赫兹频谱的固定点对点(PTP)应用的提议,这表明工业界和学术界对W波段毫米波雷达和通信系统的需求非常迫切。

近年来,国内外研究人员围绕W波段毫米波相控阵收发机开展了多项工作[1-6]。其中,加州大学伯克利分校的研究团队于2017年发布了一款W波段收发机系统,该工作采用130 nm SiGe BiCMOS工艺实现,实现了9.5 dB的接收通道噪声系数和6.4 dBm的发射通道饱和输出功率(Psat), 并且具有5.9位的有效移相位数,然而该工作没有集成收发开关和衰减器。IBM公司的研究团队于2018年发布了一款W波段收发机前端,同样采用130 nm SiGe BiCMOS工艺实现,具有7.8位的有效移相位数、7 dB的接收通道噪声系数和7.8 dBm的发射通道饱和输出功率。该工作集成了收发开关,但是插入损耗较大,导致噪声和输出功率性能较差,而且只集成了1位的衰减器。对上述工作进行总结可以得到如下的结论:

1) 以上这些团队均没有采用CMOS工艺实现,原因主要在于CMOS工艺较低的特征频率和击穿电压不利于在W波段实现高的增益和输出功率以及CMOS工艺固有的高损耗衬底降低了电路的效率。

2) 目前即使在昂贵的SiGe BiCMOS和InP HBT工艺下,实现高精度的移相仍然是一个巨大的挑战。目前W波段的移相结构比较单一,文献[1-3]采用有源矢量插值,文献[4-5]采用反射式移相结构。这两种结构在W波段均存在较大的局限性,受限于W波段的有源级增益较低,线性度较差,有源矢量差值移相器的增益通常很低,线性度很差,这会大幅度恶化发射通道的功率效率和线性度;受限于无源器件和晶体管开关的品质因子,反射式移相器的移相精度通常较低,并且在各个象限的移相精度相差较大,需要复杂的译码电路,这会增加系统的集成成本。因此这两种结构并不适用于W波段的高精度移相。

3) 国际上W波段的低损耗开关以及高精度衰减器至今仍然是空白。尽管在文献[5]中IBM采用了低毫米波波段经常采用的基于1/4λ的收发开关结构,但该结构在W波段的损耗达到了2.5 dB,这大幅度恶化了发射通道的输出功率和效率。

因此,利用 CMOS 工艺实现集成了高性能收发开关、移相器和衰减器的 W 波段相控阵收发机具有重要的意义。

1 电路架构和系统设计

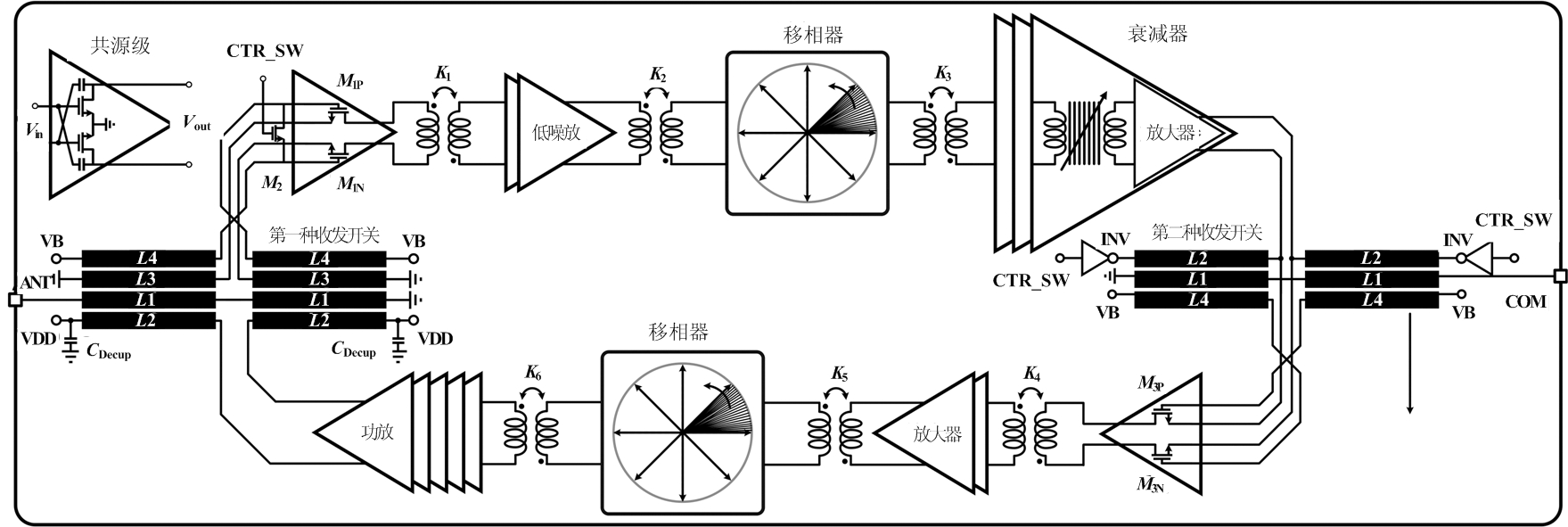

为解决上述难题,我们在本文中提出了一种采用65 nm CMOS工艺的W波段双向相控阵收发机前端,用来支持通信和雷达应用。该收发机前端系统框图如图1所示,它包括收发开关、低噪声放大器、功率放大器、移相器和衰减器等关键模块。本工作解决了高频率毫米波相控阵收发机前端的3个关键问题,第一个是传统收发开关的插入损耗过大,第二个是传统移相器和衰减器的分辨率受限,第三个是传统移相器和衰减器的增益和相位变化过大。本工作在W波段电路设计中多次应用了电磁耦合的概念,并将基于耦合线的收发开关、移相器和衰减器集成在收发机前端中。除此之外,低噪声放大器和功率放大器均采用了带中和电容的差分对这一经典结构。测试结果显示,本次设计的相控阵收发机前端实现了小于1 dB的收发开关插入损耗,在输出功率为15.1 dBm时达到了高于12.3%的峰值功率附加效率,具有小于1°的相位分辨率和小于1 dB的增益分辨率,并且满足小于±2.1 dB的增益波动和小于±6°的相位变化。

图1 收发机前端系统框图

2 各关键模块设计

2.1 收发开关

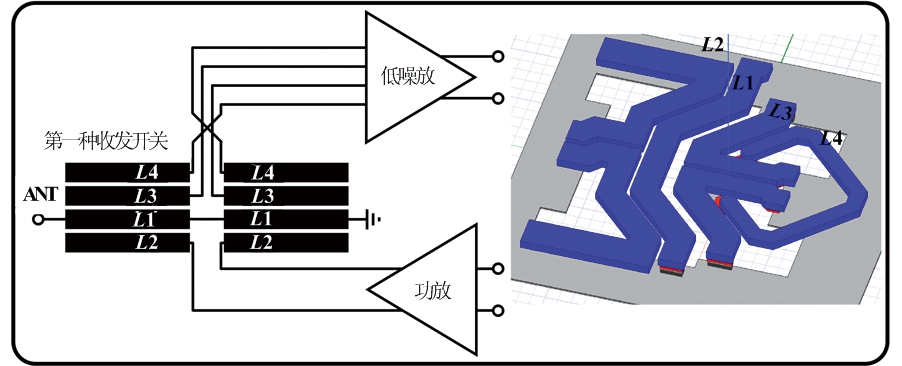

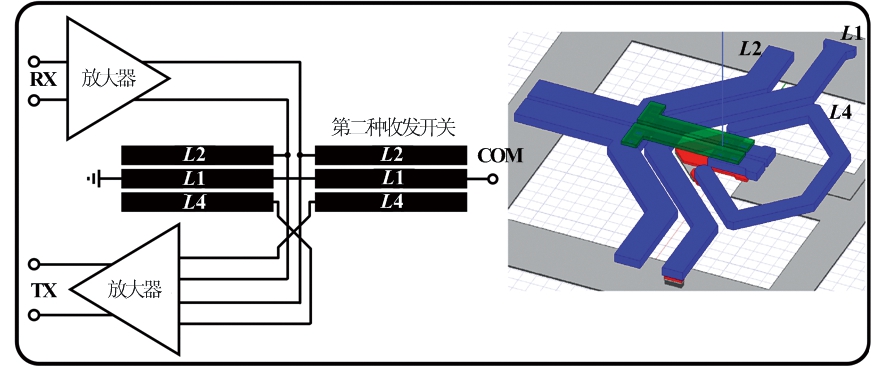

传统的基于四分之一波长传输线的收发开关存在插入损耗过高、占用面积过大和需要额外匹配网络等问题,为了解决上述问题,我们提出了两种类型的基于耦合线的收发开关,如图2(a)和(b)所示。

(a) 第一种收发开关

(b) 第二种收发开关

图2 收发开关原理图

下面将分别阐述两种收发开关的具体结构和创新之处。对于第一种类型的收发开关,该收发开关由4段主耦合线组成。其中耦合线L1将来自耦合线L2的功率放大器差分输出信号耦合到天线端口,而耦合线L3将来自耦合线L1的输入信号耦合到低噪声放大器的输入信号,同时,耦合线L4和耦合线L3一同实现了低噪声放大器中晶体管的跨导提升。此外,我们在低噪声放大器的输入端引入了晶体管M2,该晶体管可以增强接收通道和发射通道的隔离度。除了以上几个功能,这4段耦合线既实现了低噪声放大器的输入阻抗匹配,又实现了功率放大器的输出负载匹配,而且无需额外的匹配网络,有效节省了芯片面积。对于第二种类型的收发开关,该收发开关由3段主耦合线组成。功率放大器的输出和低噪声放大器的输入共用耦合线L2。通过控制VDD和GND之间的耦合线L2上的电压,收发机前端可以分别切换到接收和发射模式。第二种类型的收发开关去除了低噪声放大器输入端的晶体管开关,同时也消除了第一种类型收发开关中L2和L3之间不希望的电磁耦合,因此当作为功率放大器输出负载的晶体管的尺寸不是很大时该种类型的收发开关在插入损耗方面具有天然的优势。

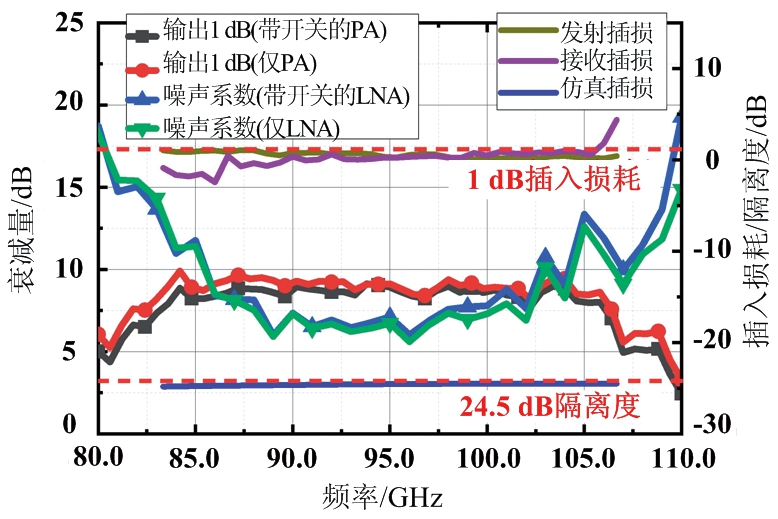

为了定量评估我们提出的基于耦合线的收发开关的性能,以第一种类型的收发开关为例进行单独的流片验证和测试,测试结果如图3所示。从图中可以看出,第一种类型的收发开关在80~106 GHz频率范围内实现了小于1 dB 的插入损耗和大于24.5 dB的收发隔离度,该结果证明本次设计的收发开关相比传统收发开关具有显著的优势。

图3 收发开关主要性能的测试结果

2.2 移相器设计

本文提出的移相器原理图如图4所示。

图4 本文提出的移相器原理图

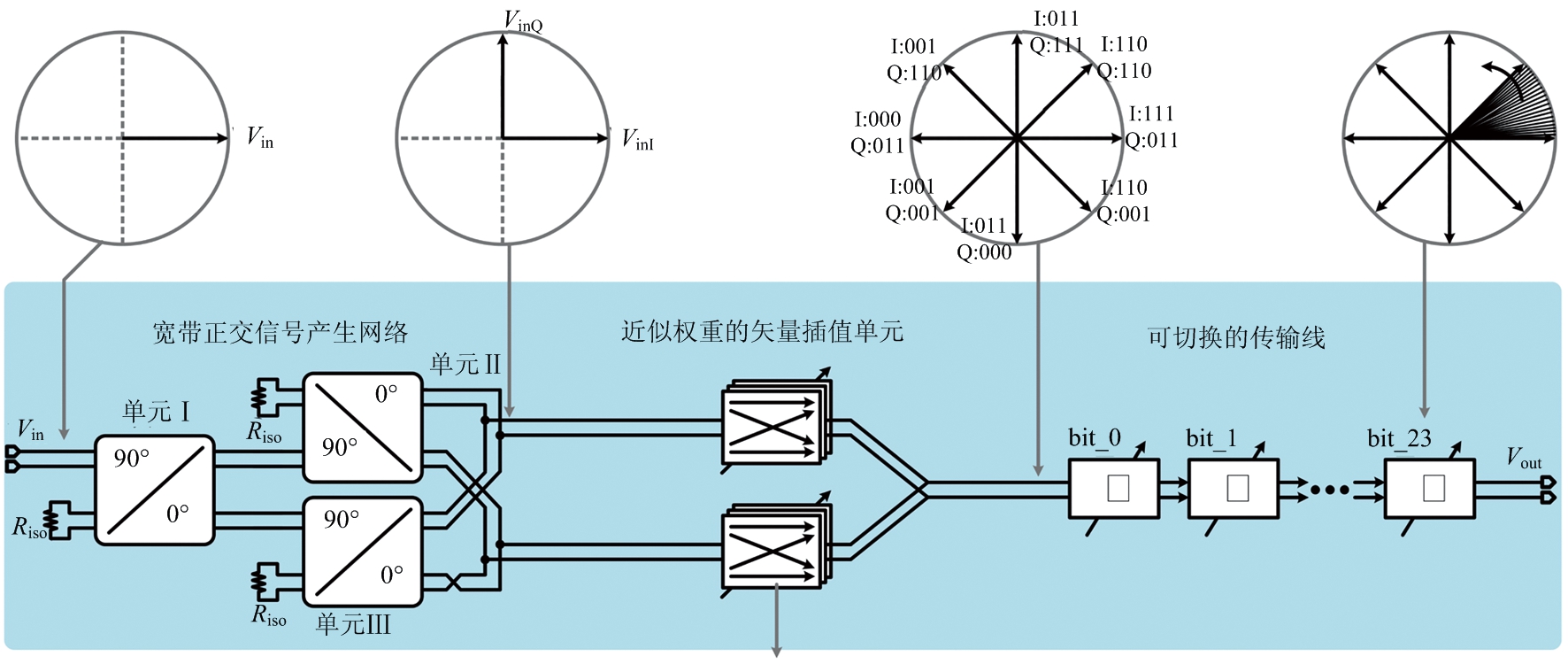

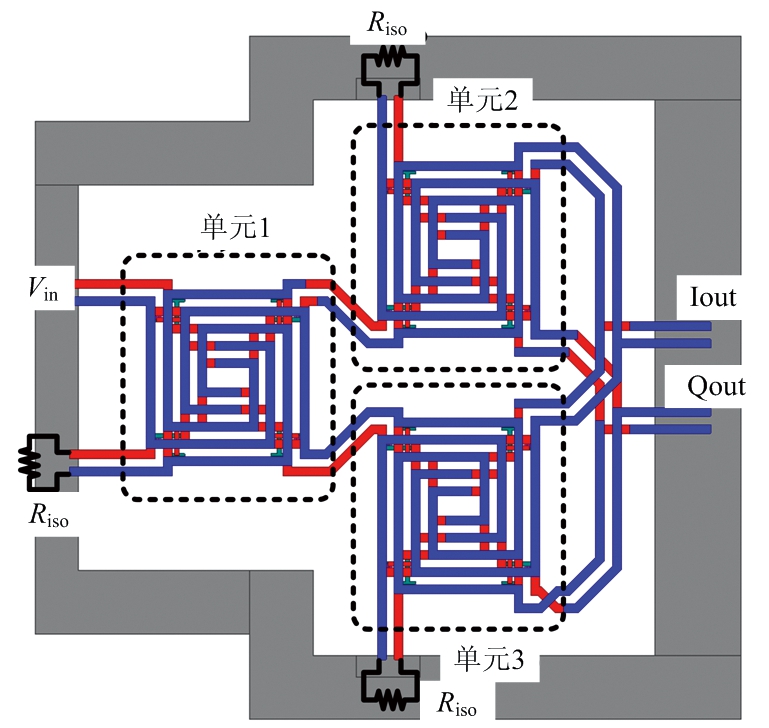

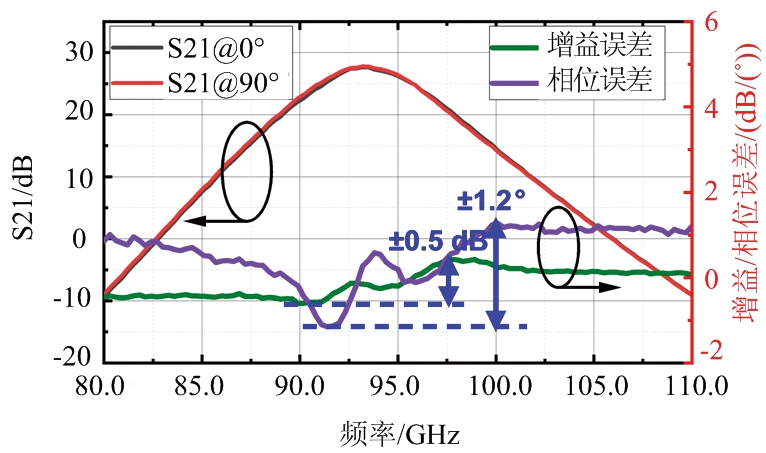

在W波段,随着感性寄生的不断加剧,移相器面临着相位分辨率不足和增益波动过大等主要挑战,要想解决上述挑战,就需要在传统移相器的结构上做出大幅度的改进和创新。该移相器主要由可切换传输线和基于近似加权矢量调制单元的相位内插器组成,从而确保移相器的高相位分辨率和低增益波动。其中,可切换传输线在大约50°的范围内提供小于1°的精细相位分辨率,而基于近似加权矢量调制单元的相位内插器在360°范围内具有45°相移步长,以将高相位分辨率映射到360°,同时有效避免增加芯片面积。为了确保精确的相位映射关系,我们提出了一种基于级联的折叠宽带变压器的正交信号生成网络,从而在极宽的频率范围上生成了稳定且匹配良好的正交关系,如图5所示。该正交信号产生网络是基于两级折叠变压器设计的,仅占用了一个电感大小的面积,非常紧凑。在80~110 GHz频率范围内,测量得到的正交信号幅度不平衡小于±0.5 dB,测量得到的正交信号相位不平衡小于±1.5°,如图6所示。

图5 本文提出的正交信号产生网络版图

图6 正交信号产生网络主要性能仿真结果

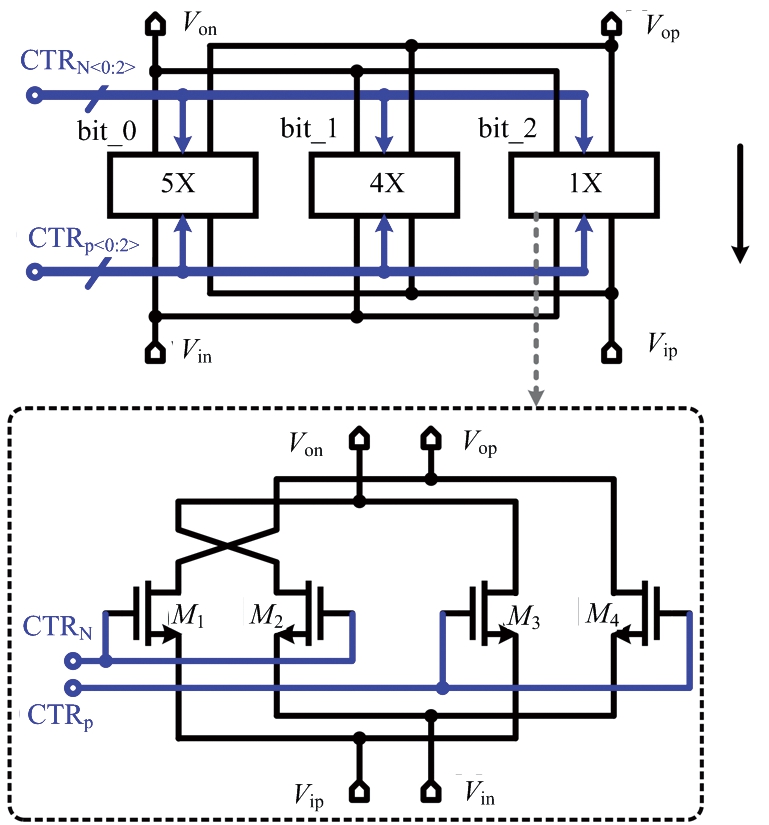

两个近似加权的矢量调制阵列对I路和Q路两路信号进行缩放,从而实现精确的45°相移大小。每个矢量调制阵列由3位矢量调制单元构成,以5∶4∶1的归一化权重并联,这样可以生成 1,0.707 和 0 的归一化增益,从而实现对相位的调节,如图7所示。

图7 本文提出的矢量调制单元示意图

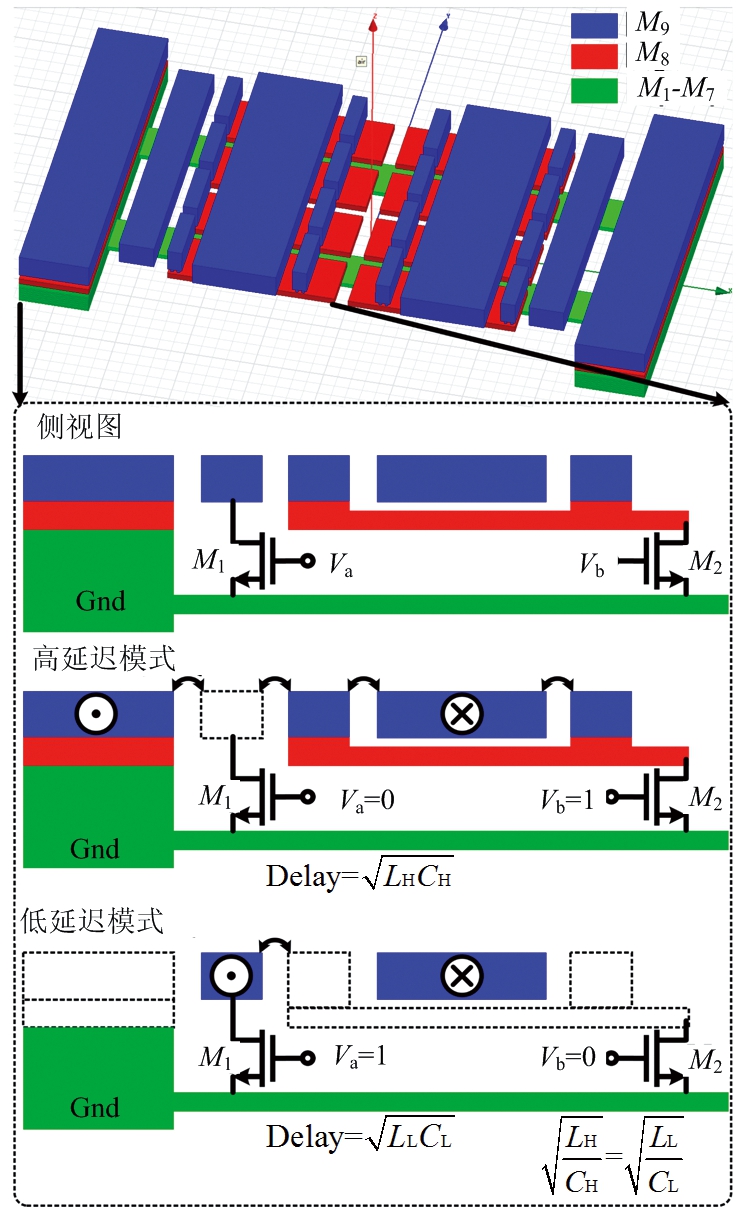

可切换传输线由一系列精心设计的传输线单元级联组成,其版图如图8所示。由于传输线的相位延迟与电感和电容的乘积有关,所以可以通过设计电感与电容的乘积来控制相位变化。需要注意的是,传输线的特征阻抗与电感和电容的比值有关,因此,在设计传输线的时候要使其特征阻抗保持恒定,从而确保在不同的相移大小下有着恒定的增益,尽可能减小移相器整体的增益波动。综上,根据本节所述的几大创新点设计出来的移相器在W波段具备优异的性能,很好地解决了前文所述的几大挑战。

图8 本文提出的传输线单元版图

2.3 衰减器设计

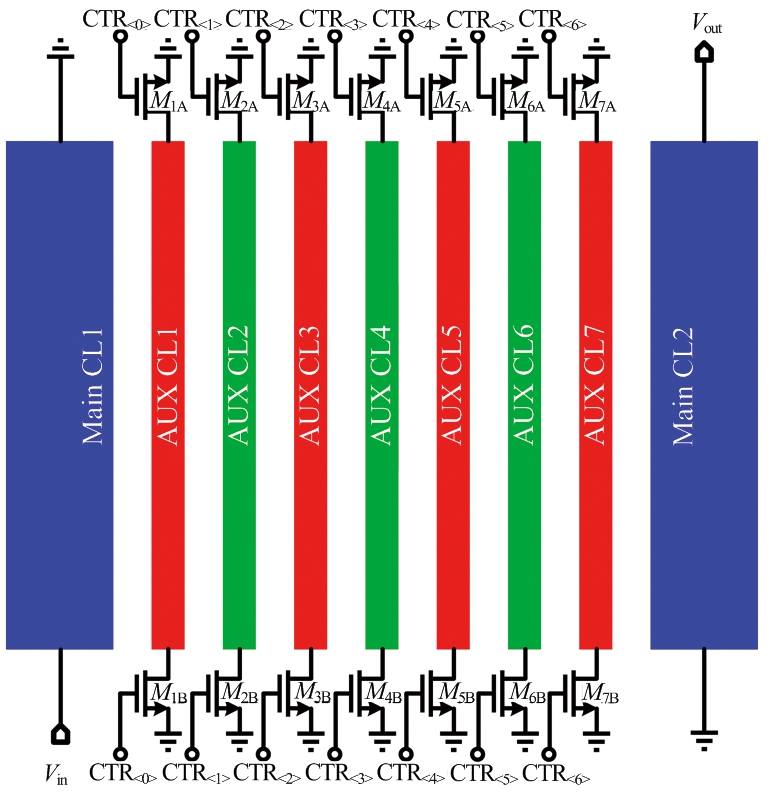

本文提出的衰减器原理图如图9所示。传统的基于开关内嵌式的衰减器在W波段插入损耗过大,这会严重影响系统性能。为了解决该问题,本文提出了一种新型的基于耦合线的衰减器结构,该衰减器由2段主耦合线和7段辅助耦合线组成,开关晶体管M1-6A/B通过调整相邻主耦合线之间的电磁耦合强度来控制增益。

图9 本文提出的衰减器原理图

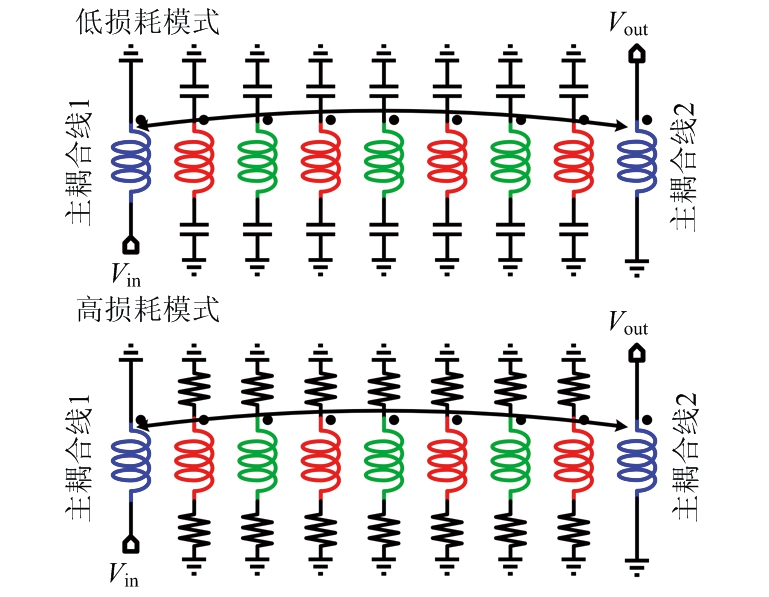

当开关晶体管的控制信号切换为0或者1时,这两种状态之间的主耦合线的耦合强度差异可以近似为主耦合线和辅助耦合线之间的耦合系数的乘积,从而产生信号的衰减。衰减器在上述工作模式下的小信号等效原理图如图 10所示。

图10 衰减器在不同工作模式下的小信号等效原理图

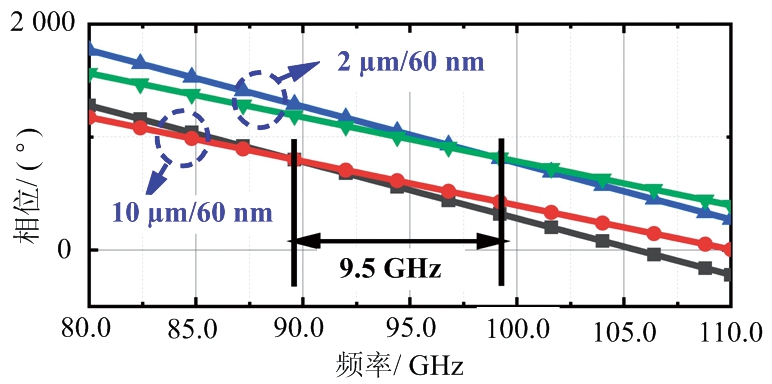

图11中的仿真结果显示,当M1-6A/B的尺寸从2 μm/60 nm变为10 μm/60 nm时,在最小和最大衰减状态下相位保持恒定的频率点偏离了大约9.5 GHz。为了使得衰减器在80~110 GHz的频率范围内的相位变化最小,我们最终将M1-6A/B的尺寸优化为6 μm/60 nm。两个弯折的单端耦合衰减器可以组合成一个带有共模接入点的差分衰减器,因此它可以用作级间匹配网络,即嵌入在系统的级间放大器中,并且不需要占用额外的芯片面积,该衰减器的版图如图12所示。

图11 衰减器不同晶体管尺寸下的相位随频率变化仿真结果

图12 本文提出的衰减器版图

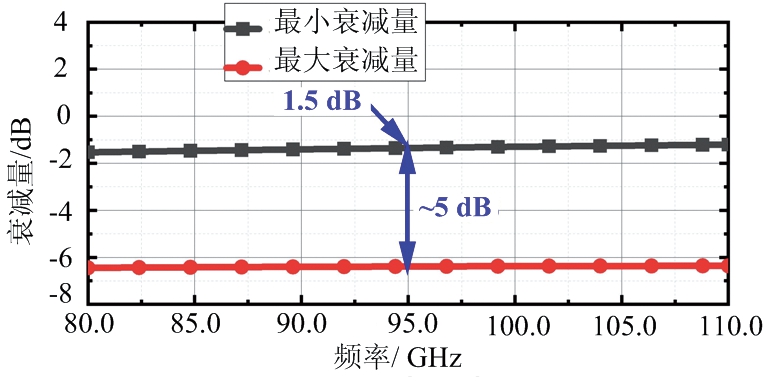

图13中的仿真结果表明,基于差分耦合的衰减器的插入损耗在80~110 GHz频率范围内仅约为1.5 dB,该指标相比于传统的开关内嵌式衰减器有了大幅度的减小。该衰减器的衰减范围约为5 dB,将3个衰减器级联在一起就可以实现约15 dB的衰减范围,从而满足相控阵前端对于幅度控制的要求。

图13 衰减器性能仿真结果

3 测试结果

在前一节所述创新点的基础上,我们设计了整个W波段收发机前端。图14显示了采用65 nm CMOS工艺制造的芯片显微照片,它的面积仅为0.9 mm×1.65 mm,整个芯片面积非常紧凑。

图14 芯片显微照片

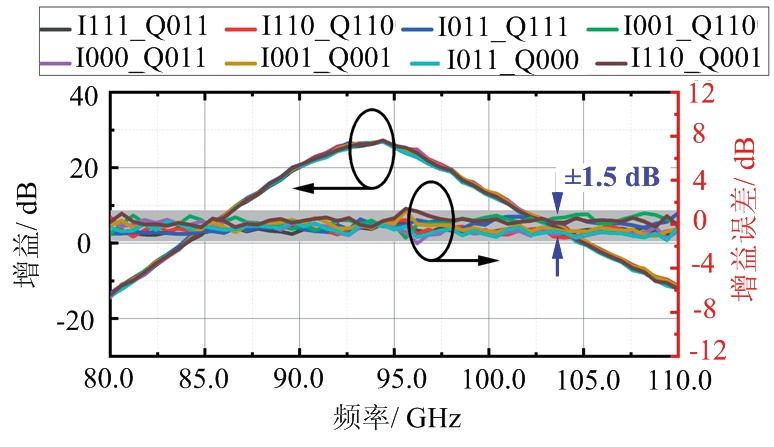

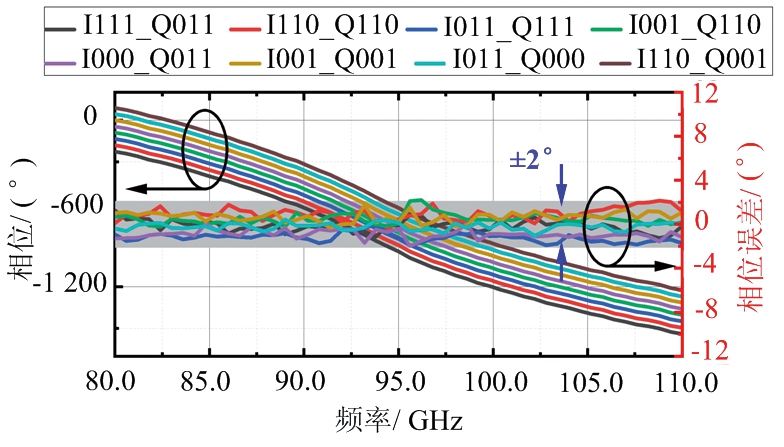

首先表征移相器中的矢量插值单元的增益和相位响应,测试结果如图15所示。移相器中的矢量插值单元在360°范围内实现精确的45°相移大小,在80~110 GHz频率范围内相位误差小于±2°,这表明矢量插值单元具有精确的相位映射能力,同时,它的增益变化在360°频率范围内小于±1.5 dB。

(a) 增益响应

(b) 相位响应

图15 矢量插值单元的测试结果

(a) 增益响应

(b) 相位响应

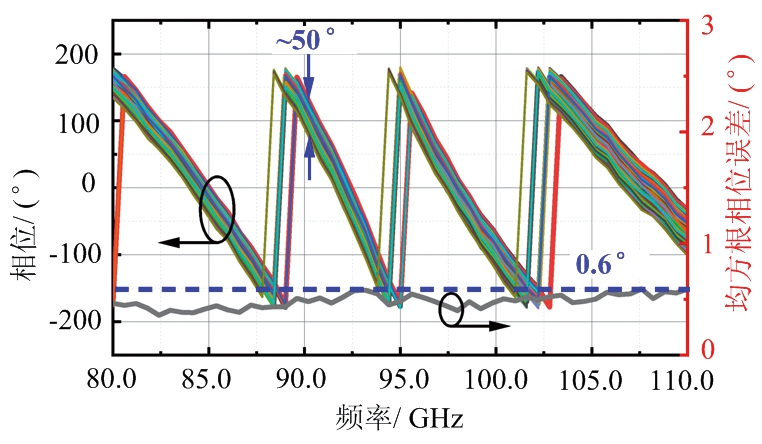

图16 可切换传输线的测试结果

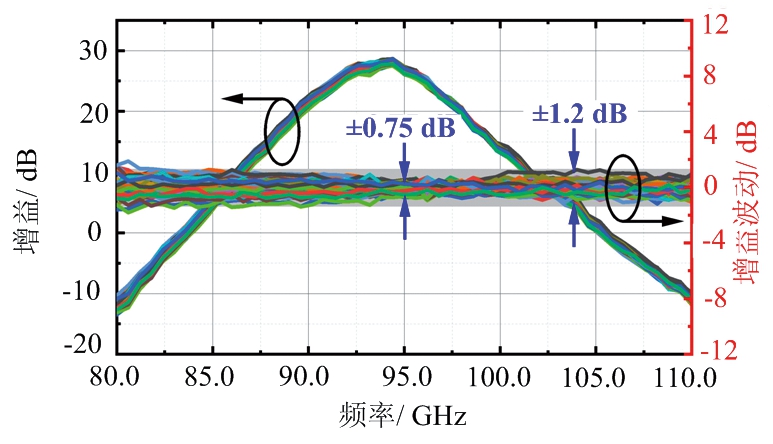

然后表征移相器中的可切换传输线的增益和相位响应,测试结果如图16所示。可切换传输线在80~110 GHz频率范围内实现了约 0.75°的相位分辨率和约为50°的相移范围,均方根相位误差小于0.6°。因此,可切换传输线的高分辨率移相范围可以覆盖矢量插值单元的45°移相步长大小。同时,可切换传输线在大约50°的相移范围内的增益变化小于±1.2 dB,当频率是95 GHz时增益变化的最小值为±0.75 dB。

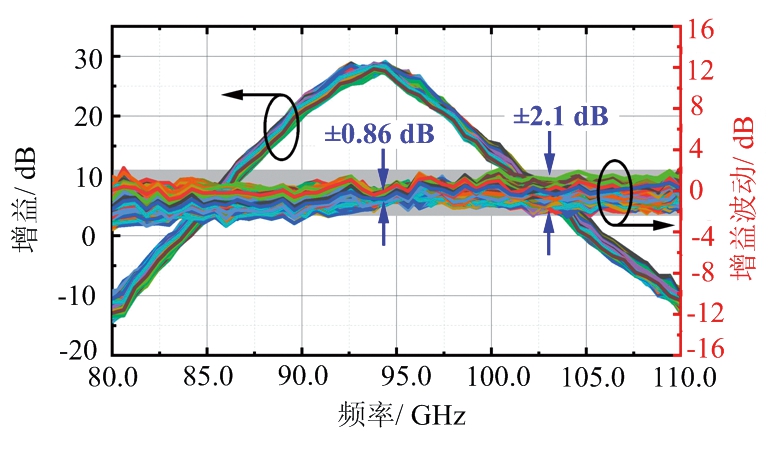

最后,对整个基于耦合线的移相器进行表征,测试结果如图17所示。移相器在80~110 GHz频率范围内实现了大约0.75°的相位分辨率和372°的相移范围,均方根相位误差小于0.7°。在372°相移范围内传输线的增益变化均小于±2.1 dB。

(a) 增益响应

(b) 相位响应

图17 接收通道中移相器的测试结果

(a) 增益误差

(b) 相位误差

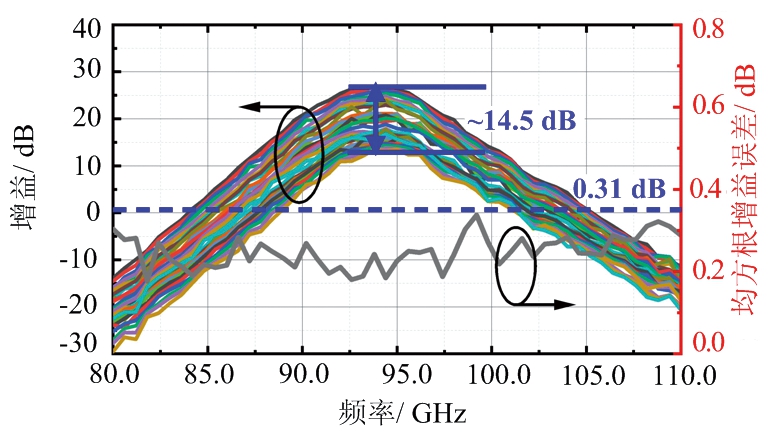

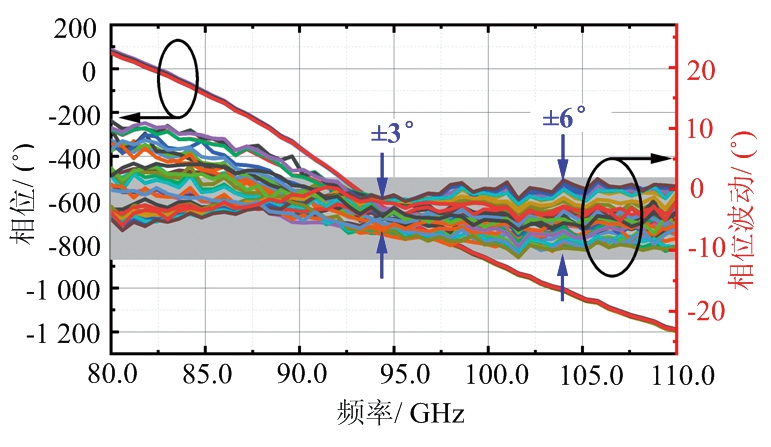

图18 接收通道中衰减器测试结果

该收发机前端的接收通道实现了14.5 dB的增益控制范围,衰减性能的测试结果如图18所示。它在频率是95 GHz时的平均增益步长为0.4 dB,均方根增益误差在80~110 GHz频率范围内小于0.31 dB。

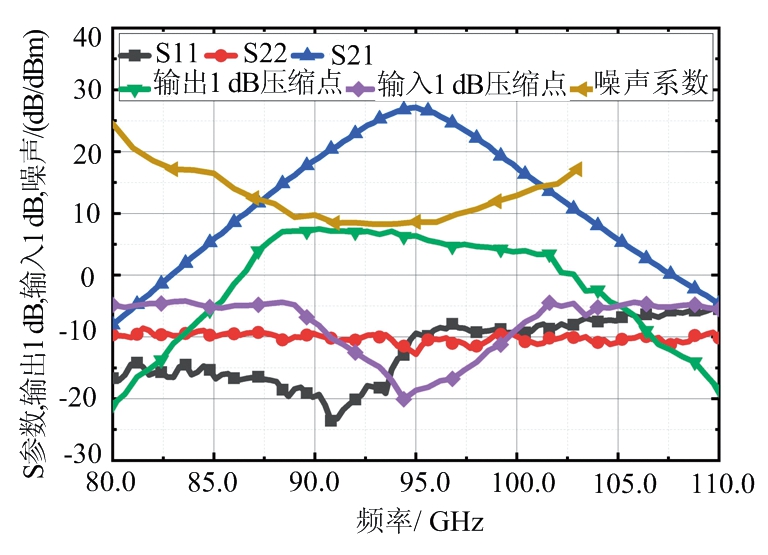

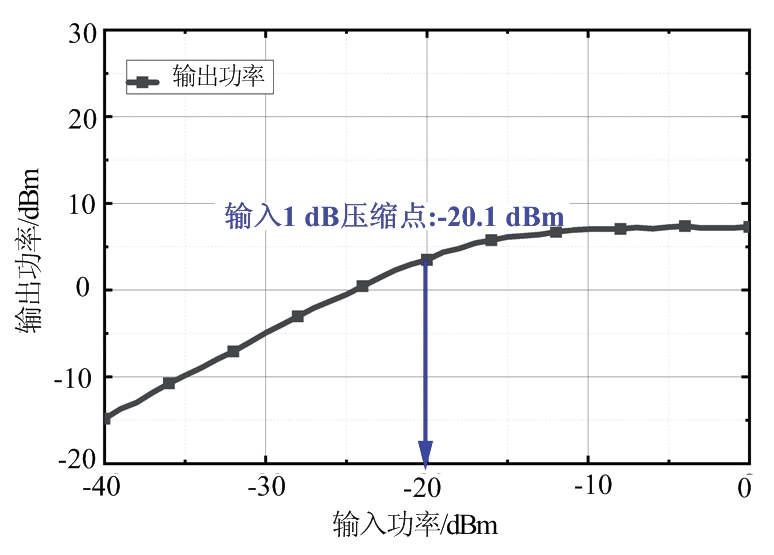

图19展示了接收通道小信号和大信号性能的测试结果。接收通道达到了92~97 GHz的3 dB增益带宽(BW-3dB),其中当频率是94 GHz时实现了27.2 dB的最大增益和8.2 dB的最小噪声系数(NF)。接收通道在95 GHz时的输入1 dB压缩点(IP1dB)为-20.1 dBm。

(a) 小信号性能

(b) 大信号性能

图19 接收通道测试结果

(a) 小信号性能

(b) 大信号性能

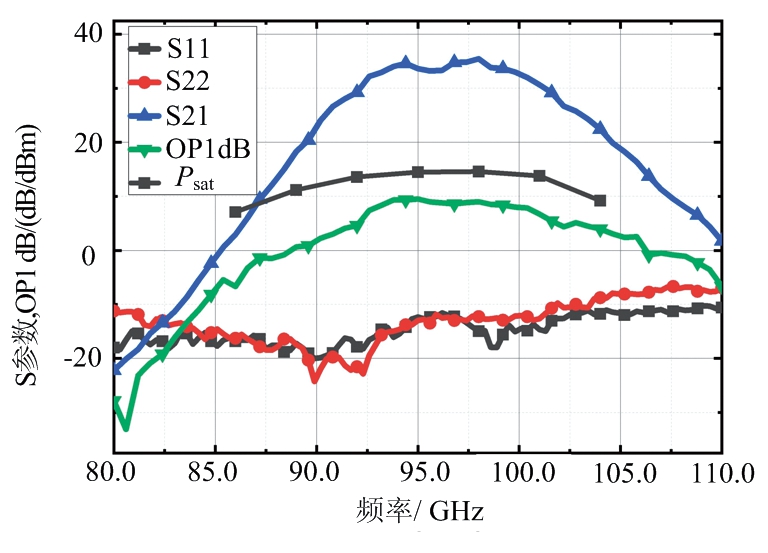

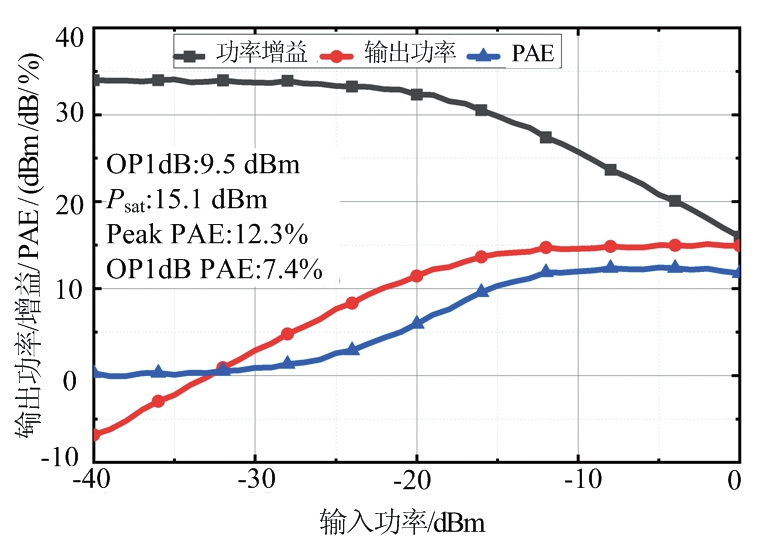

图20 发射通道测试结果

图20展示了发射通道小信号和大信号性能的测试结果。发射通道达到了92.5~100.3 GHz的BW-3dB,它的输出1 dB压缩点(OP1dB)的1 dB带宽(BW-1dB)覆盖了93.4~99.4 GHz的频率范围,其中最大的OP1dB为9.54 dBm。发射通道在频率是95 GHz时达到了15.1 dBm 的饱和功率(Psat),实现了9.5 dBm的OP1dB,具有12.3%的峰值功率附加效率(PAE)和7.4%的OP1dB PAE。

表1展示了这项工作与其他现有最先进工作的性能比较。与先进的SiGe工艺和HBT工艺中的W波段相控阵前端相比,我们提出的相控阵前端是唯一同时集成了收发开关和衰减器的,这将大大提高相控阵系统的性能并降低成本。

表1 本工作与其他现有最先进工作的性能比较

类别文献[1]JSSC’17文献[2]JSSC’19文献[3]JSSC’17文献[4]JSSC’18文献[5]TMTT’15文献[6]JSSC’15本工作工艺130 nmSiGeBICMOS180 nmSiGeBiCMOS130 nmInP HBT130 nmSiGeBICMOS130 nmSiGeBICMOS65 nmCMOS65 nmCMOS集成度收发系统收发系统收发前端收发系统收发前端收发系统收发前端是否集成收发开关否否是否是否是收发开关插入损耗--2-发射2.5接收0.5-<1频率/GHz9480~100949488~9687.8~98.992~9780~110移相移相位数5.953.67.8578.9均方根相位误差/(°)N/AN/AN/A0.331.3<0.7增益波动/dB<1.4N/A<40.5(均方根)<±10.74 (均方根)<±2.1衰减是否集成衰减器否否否是否否是衰减位数---1--6衰减范围/dB---12--14.5均方根衰减误差/dB------<0.31相位波动/(°)------<±6接收接收增益/dBN/AN/A2121~413026~4025.2接收噪声/dB9.56.5~8<9.3<7<8.510<9输入1 dB压缩点/dBmN/AN/A-23-44.5-37N/A-20.1发射发射增益/dBN/A142235.5>251734.9输出1 dB压缩点/dBmN/AN/AN/A4.60.8N/A9.54饱和功率/dBm6.46~857.83.2 915.1峰值PAE/%<12N/AN/A N/AN/A10.212.3输出1 dB压缩点PAE/%N/AN/AN/AN/AN/AN/A7.4接收通道功耗/mW912253970~120809080芯片面积/mm22.043.032.71.250.951.890.99

4 结束语

由于我们提出的基于耦合的收发开关、移相器和衰减器这三个重要模块具有突出的优势,所以我们设计的收发前端相比其他工作达到了最小的收发开关插入损耗(IL),具有最高的相位/增益分辨率和最高的OP1dB/Psat,同时实现了高达7.4%的OP1dB PAE和12.3%的峰值PAE,证明了该项工作具备的突出优势。

[1] TOWNLEY A, SWIRHUN P, TITZ D, et al. A 94-GHz 4TX-4RX Phased-Array FMCW Radar Transceiver with Antenna-in-Package[J]. IEEE Journal of Solid-State Circuits, 2017, 52(5):1245-1259.

[2] SHAHRAMIAN S, HOLYOAK M J, SINGH A, et al. A Fully Integrated 384-Element, 16-Tile, W-Band

Phased Array with Self-Alignment and Self-Test[J]. IEEE Journal of Solid-State Circuits, 2019,54(9):2419-2434.

[3] KIM S K, MAURER R, SIMSEK A, et al. An Ultra-Low-Power Dual-Polarization Transceiver Front-End for 94-GHz Phased Arrays in 130-nm InP HBT[J]. IEEE Journal of Solid-State Circuits, 2017, 52(9):2267-2276.

[4] LEE W, PLOUCHART J O, OZDAG C, et al. Fully Integrated 94-GHz Dual-Polarized TX and RX Phased Array Chipset in SiGe BiCMOS Operating up to 105 °C[J]. IEEE Journal of Solid-State Circuits, 2018, 53(9):2512-2531.

[5] NATARAJAN A, VALDES-GARCIA A, SADHU B, et al. W-Band Dual-Polarization Phased-Array Transceiver Front-End in SiGe BiCMOS[J]. IEEE Trans on Microwave Theory and Techniques, 2015, 63(6):1989-2002.

[6] CHEN Pengning, PENG Penjui, KAO C, et al. A 94 GHz 3D-Image Radar Engine with 4TX/4RX Beamforming Scan Technique in 65nm CMOS Technology [C]∥2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA:IEEE,2013:146-147.