0 引 言

W波段频率高、波长短,能够获得很高的分辨率,又具有透射率高的大气窗口和大带宽,使得W波段相控阵雷达在汽车雷达、回程通信和毫米波成像等领域得到了广泛应用。

片上雷达指的是将雷达收发机集成到单个芯片上的技术,早期的片上雷达大多由GaAs工艺实现。近年来,硅基工艺下晶体管的特征频率与最高振荡频率显著提升,基于硅基工艺的射频相控阵系统集成技术已经成为高性能毫米波雷达的一个重要的研究方向[1-5]。针对二维集成来说,从最早的单片4通道、8通道阵列,很快发展为单片16通道、32通道与64通道阵列。最早的芯片相控阵大多不包含天线,因此在单元硅芯片与平面天线阵之间有传输线馈电网络[6]。这就需要在硅芯片与馈电网络之间有毫米波转换:通常采用倒装焊技术结合多层基板,或者采用在硅芯片表面的聚酰亚胺(Polyimide, PI)再布线层(Redistribution Layer, RDL)实现晶圆级封装(Wafer-Level Package, WLP)或芯片级封装(Chip-Scale Package, CSP)[7]。然而,转换以及馈电网络附加了较大的损耗,在60~80 GHz的16通道损耗约为2~4 dB,又容易引入电磁耦合从而降低天线方向图性能[8]。并且,由于多余损耗和复杂的馈电网络使得通道数不易扩展。多层特氟隆和低温共烧陶瓷(Low Temperature Co-fired Ceramic, LTCC)基板在毫米波频段价格与硅芯片差不多,会使前端系统价格翻倍[9]。三维集成晶圆级相控阵可解决复杂的分布网络问题,晶圆级天线层直接覆盖在硅基片上,每个天线均由相对应的相控阵单元直接激励,这种方式可使有源部分和天线单元在空间分布上属于层叠结构,所占面积可约等于硅芯片面积,从而可以扩展至更大规模数量的单元[10]。另外,具有N通道的相控阵系统能够让天线的等效全向辐射功率(Equivalent Isotropically Radiated Power, EIRP)增加至20logN dB,削弱了相控阵系统整体对单通道的输出功率依赖。因此,大规模集成相控阵微系统能够充分发挥硅基芯片集成度高、成本低的优势,也很大程度上弥补了硅基多功能芯片功率低的短板,展现出了低成本和高性能的解决方案。

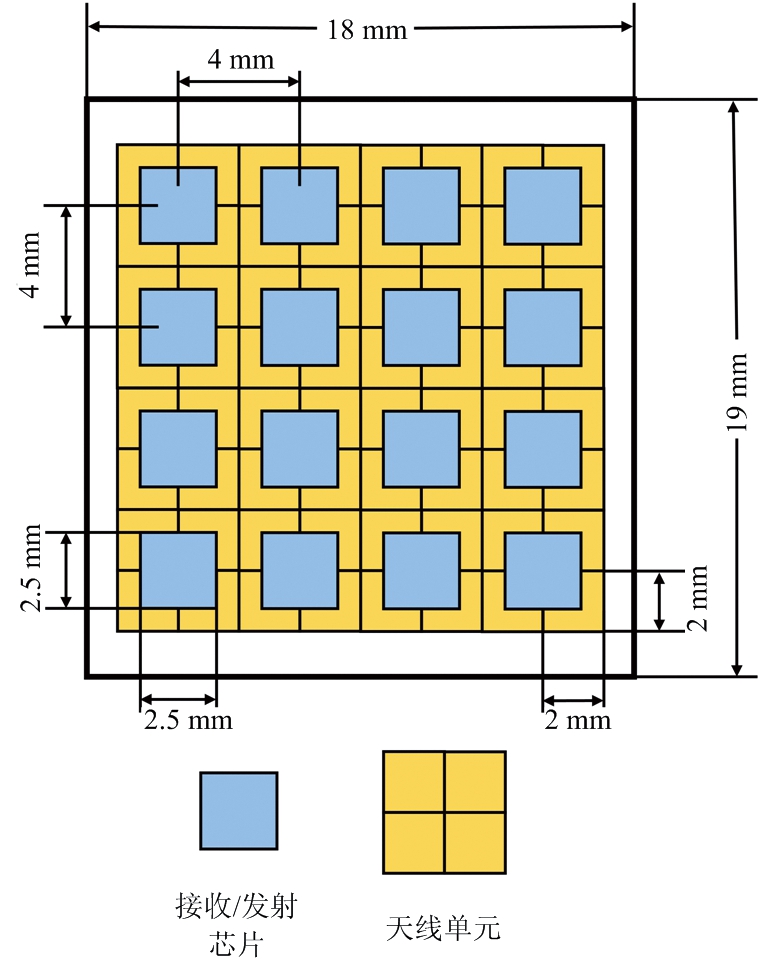

本文介绍了一款W波段的片上封装天线相控阵微系统模块。该相控阵天线系统采用硅基三维集成的方式将16个四通道多功能芯片与64个天线单元集成在一个微系统模块中,具有高集成度、高性能、低成本的特点,可满足无人机等平台对小型化、高分辨率通信、成像设备的需要。

1 毫米波收发芯片设计

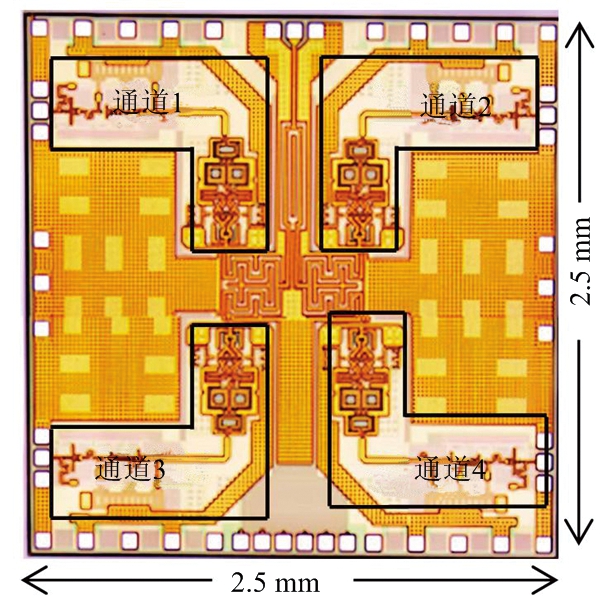

图1、图2分别是W波段四通道接收/发射芯片的系统框图和芯片照片,每个芯片包含4个通道;对于接收芯片,接收到的信号由低噪声放大器放大并抑制噪声,再由移相器处理获得相移并产生相对延迟。功率合成器将四路信号进行合成处理;对于发射芯片,射频输入信号先由功率分配器将一路信号分配到四路,信号经移相器进行相移处理后,再由功率放大器对其进行放大。此外,还集成了具有高低温温度补偿功能的偏置电路和串行外设接口(Serial Peripheral Interface, SPI),以分别提供所需要的偏置电压和数字控制信号。为提升毫米波收发芯片的性能,采用了如下关键技术:

(a) 系统框图

(b) 芯片照片

图1 四通道接收芯片

(a) 系统框图

(b) 芯片照片

图2 四通道发射芯片

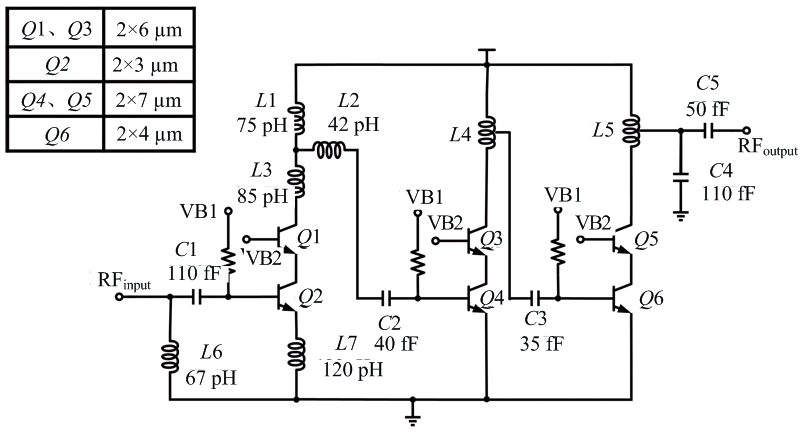

1) 电感峰化型低噪声放大器设计:低噪声放大器是接收前端天线之后的第一个模块,其噪声系数对接收系统整体噪声系数起着最主要的影响。本设计采用三级级联的共射共基结构。第一级通过电感L7引入射级负反馈,配合电感L6,实现输入阻抗和噪声的同时匹配。并采用T型电感做负载,在工作带宽上引入了两个谐振点,拓展了带宽;第二、三级采用了不对称抽头电感做负载,不对称抽头电感的抽头端等效为负值电感,负值电感将第二、三级频带上的谐振点往工作频率上牵引,提升了放大器整体的增益和带宽。电路结构图如图3(a)所示。

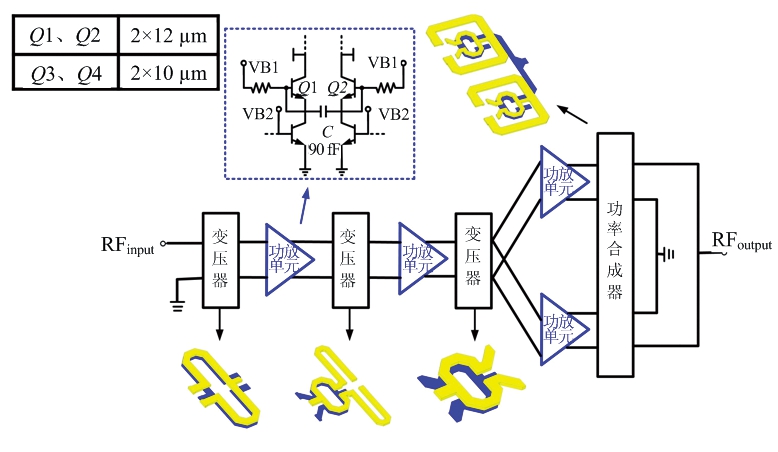

2) 基于功率合成结构的功率放大器设计:作为发射前端的最后一个有源级,决定了整个系统的输出功率、效率和线性度。所提出的功率放大器采用三级伪差分共射共基放大器级联。输入端采用变压器巴伦实现信号的单端到差分以及阻抗匹配。级间变压器及差分传输线实现级间的阻抗匹配。输出端采用基于变压器的四路并联功率合成器,其结构对称性好,输出端表现出更好的幅相一致性,提升了功率合成的效率。三级放大器晶体管尺寸的选择符合功率放大器的推动比要求,有效避免了功率被前一级放大器压缩的同时保证了功率的最佳传输。每一级放大器采用伪差分结构,降低了毫米波频段地平面非理想因素的干扰,提高了放大器的稳定性。电路结构图如图3(b)所示。

3) 高精度有源移相器设计:移相器管控着相控阵收发芯片中的波束控制,它必须以高相移分辨率覆盖整个360°相移范围。提出了采用大规模数字校准的有源移相器,实现了6位高精度、低误差移相。设计采用了变压器巴伦以产生差分信号,Lange耦合器产生正交信号,二者级联匹配能产生低幅度误差和相位误差的正交信号。可变增益放大器给予正交信号不同的增益,并将四路信号矢量合成为一路,以获得所需的增益和相移。本设计中的4个可变增益放大器由4个5位数字模拟转换器(Digital-to-Analog Convertor, DAC)独立控制,配合自动化校准脚本,64(26)个最终的移相态从1 048 576(220)个中间移相态中选定,极大程度上克服了工艺误差,有效地提升了移相器的精度。电路结构图如图3(c)所示。

4) 高低温温度补偿设计:为了保证低噪声放大器能够具有较好的温度特性,其偏置电压由可进行高低温温度补偿的偏置电路提供,可补偿低温时异质结双极晶体管(Heterojunction Bipolar Transistor, HBT)增益的下降、高温时HBT增益的上升。在-45~125 ℃的工作范围内可以极大地提升增益的平坦度。温度补偿电路如图3(d)所示,利用两个串联的二极管接法的HBT,形成负温度系数电压,作为放大管的偏置电压。

(a) 电感峰化型低噪声放大器

(b) 基于功率合成结构的功率放大器

(c) 高精度有源移相器

(d) 温度补偿偏置电路

图3 收发芯片各模块电路结构

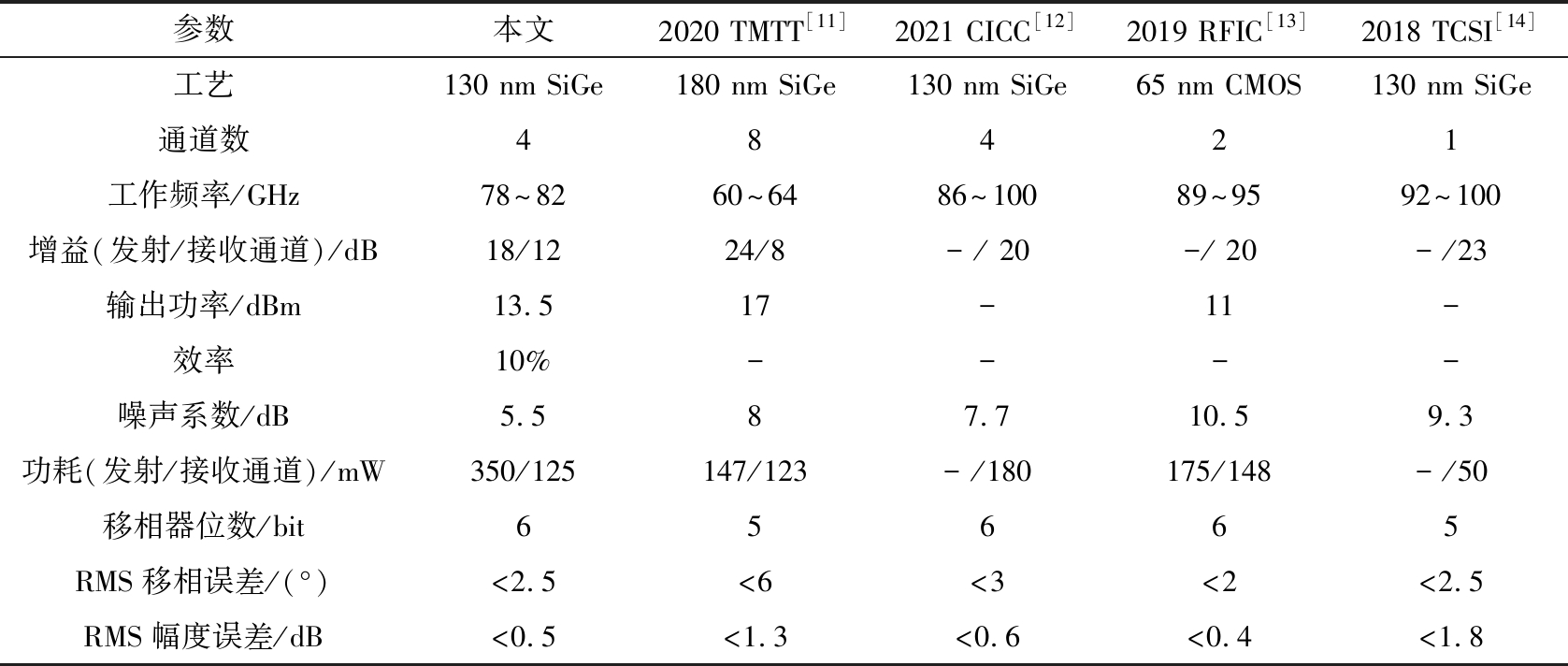

在片测试采用矢量网络分析器加扩频模块实现,测试环境如图4所示,其关键性能参数总结于表1中。相较于砷化镓工艺的多功能芯片,所设计的硅基工艺的芯片在集成度、功耗、成本、幅相控制精度等方面展现出了明显的优势。

表1 多功能收发芯片测试结果总结与对比

参数本文2020 TMTT[11]2021 CICC[12]2019 RFIC[13]2018 TCSI[14]工艺130 nm SiGe180 nm SiGe130 nm SiGe65 nm CMOS130 nm SiGe通道数48421工作频率/GHz78~8260~6486~10089~9592~100增益(发射/接收通道)/dB18/12 24/8- / 20-/ 20- /23输出功率/dBm13.517-11-效率10%----噪声系数/dB5.587.710.59.3功耗(发射/接收通道)/mW350/125147/123- /180175/148- /50移相器位数/bit65665RMS移相误差/(°)<2.5<6<3<2<2.5RMS幅度误差/dB<0.5<1.3<0.6<0.4<1.8

图 4 芯片在片测试环境

2 相控阵封装天线设计

图5为相控阵阵列剖面图。其包含了16颗4通道发射/接收芯片,可实现微波信号的相位配置和放大。16颗芯片分别与64个天线单元(8×8排列)相连接,天线单元间距为2 mm。此外,集成了电源控制与数字控制网络,提供给相控阵芯片所需的电源和控制指令。考虑天线指标要求和硅基工艺制作特点,应用了以下关键技术完成了相控阵封装天线设计。

图5 相控阵阵列剖面图

1) 多元法旋转馈电与圆极化天线单元设计

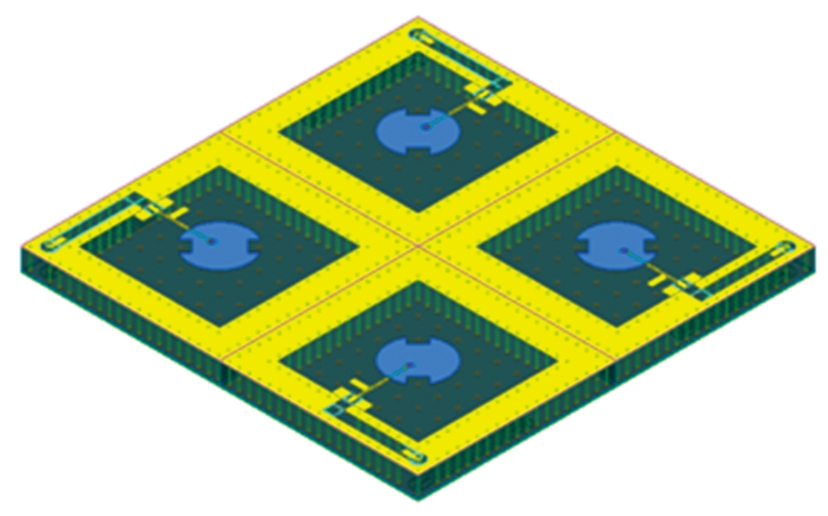

本文所研制的79~81 GHz二维电扫描相控阵,天线为圆极化形式。微带贴片天线模型简单易于实现,在实现圆极化方面有着天然的优势。通常可以用单馈法和多馈法来实现圆极化天线。此外,还可以用多个线极化的微带天线单元构成一个天线系统来实现圆极化功能,这种方法称为多元法;圆极化波的场是等幅旋转场,有左旋向和右旋向之分。任意圆极化入射波都可以看作两个在空间和时间上都正交化的幅度相同的线极化波的叠加。要获得圆极化波,叠加的两线极化波的电场必须满足:两电场矢量幅度相等,两电场矢量空间上相互垂直,两电场矢量相位差π/2。所以实现圆极化的方法可以是构造两个空间正交等幅度的线极化波,同时保持相位差为 90°。综合天线指标要求和硅基工艺制作特点,本文采用多元法旋转馈电实现圆极化:4个依次旋转的线极化单元,以等幅、相位依次相差90°馈电来获得圆极化。

由于旋转布阵大大降低了交叉极化电平,使阵面在法向方向具备优良的圆极化性能。同时,旋转馈电方式还能提升天线带宽。但是,当波束指向逐渐偏离阵面法向时,天线轴比会恶化,线极化单元形式的旋转圆极化阵列天线宽角扫描时增益下降,后瓣电平增大,限制了旋转圆极化阵列天线形式在相控阵领域的应用。圆极化单元同样适用于旋转圆极化阵列天线形式,与线极化单元形式旋转圆极化阵列天线相比,该形式在天线扫描时具备更加优异的圆极化性能。为了增加带宽同时还能改善波束扫描引起的天线增益下降和后瓣电平增大现象,本文采用圆极化天线单元作为旋转馈电圆极化阵列天线阵元。所提出的多元法旋转馈电与圆极化天线单元,结构如图6所示。

图6 2×2天线单元结构图

考虑到微带贴片天线表面波,在馈电线周围和天线单元四周进行模式消除过孔设计。模式消除过孔技术可以使天线扫描时,在较大的扫描范围消除盲点。

2) 硅基三维高密度微系统叠层结构设计

如图7所示为提出的硅基三维微系统高密集成结构示意图。三维微系统采用硅基三维堆叠方案,一共由3层200 μm高阻硅基转接板结构组成。通过RDL将微带天线制作在晶圆1上的PI层内部。PI层作为天线罩隔绝了部分外界环境的影响;晶圆1和晶圆2采用晶圆级键合工艺,设计了深度250 μm的深腔,为接收/发射芯片和键合线提供了空间,并增强了射频信号路径之间的隔离;接收/发射芯片采用引线键合的方式组装在底部硅基晶圆3上,实现芯片间以及芯片与天线间的电气互连。晶圆3的下表面还设计有BGA阵列,可以与底板实现互连。为了保证互连高频性能,三维微系统采用电阻率相对较低的高阻硅材料进行制备。为了降低垂直互连的损耗,采用深度较低的TSV互连,并且转接板间采用低矮的Cu-Sn凸块进行互连。

图7 收发芯片与天线一体化封装(单颗芯片)结构示意图

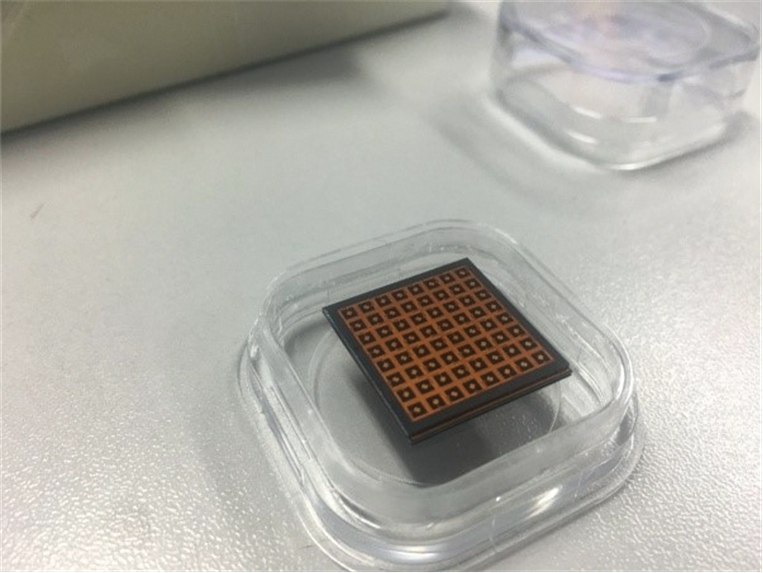

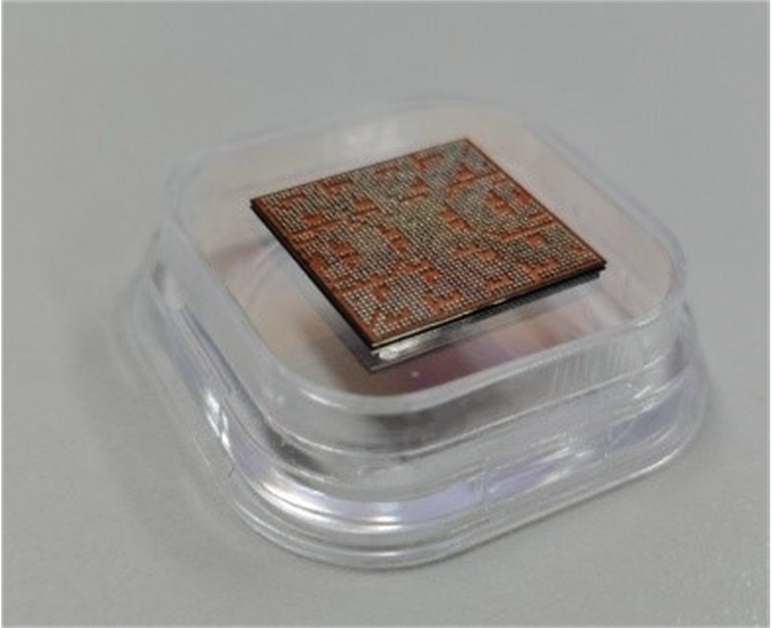

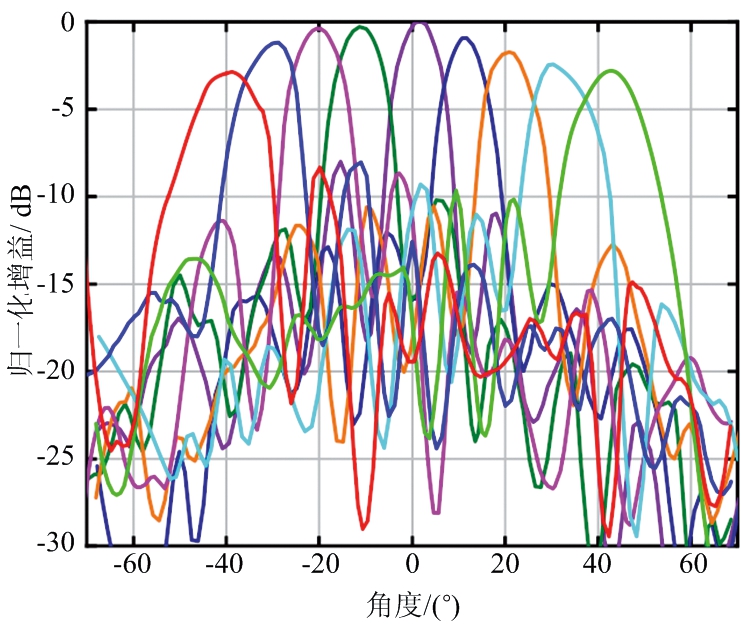

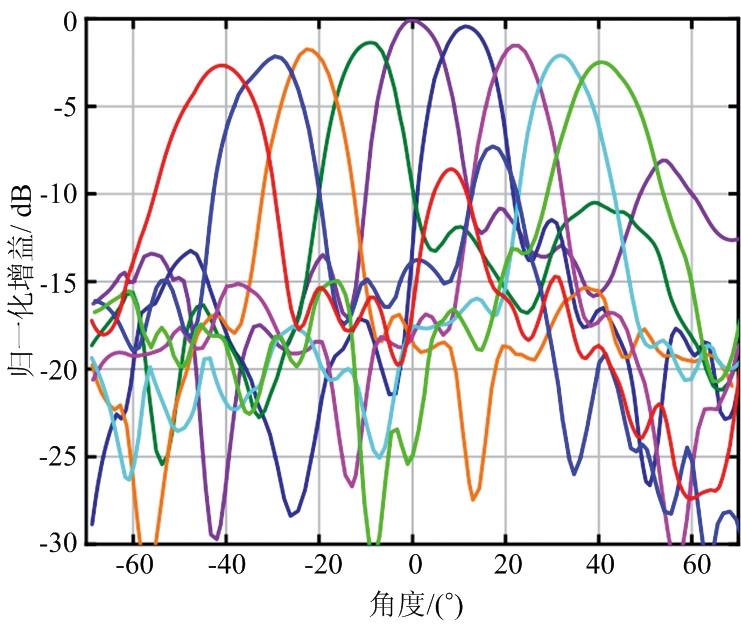

64通道相控阵实物如图8所示。其通过BGA与波控母板进行连接,波控母板不仅实现波束控制和供电功能,同时也通过底部的散热翅片将相控阵产生的热量及时带走以确保系统正常工作。整个相控阵微系统体积为16 mm×15 mm×1.4 mm。在微波暗室进行近场校准后,在远场测试了64通道相控阵方位面和俯仰面波束扫描方向图。接收微系统模块在80 GHz频点处的波束在±40°、±30°、±20°、±10°和法向的方向图如图9所示,根据测试结果可以得到,在扫描角度为±20°时,天线增益降低小于1.8 dB,在扫描角度为±40°时,天线增益降低小于3.0 dB。完整的测试结果总结在表2中。性能指标满足实际工作的需求。

(a) 相控阵正面实物照片

(b) 相控阵背面实物照片

图8 64通道发射相控阵

(a) 80 GHz方位面方向图测试结果

(b) 80 GHz俯仰面方向图测试结果

图9 64通道相控阵方位面和俯仰面波束扫描方向图

表2 相控阵测试结果总结及对比

参数本文文献[11]文献[15]工作频率/GHz79~8160~6470~100通道数646416方位面/俯仰面扫描平面/(°)±40/±40±50/±50±30/±30EIRP/dBm273834旁瓣电平/dB≤-7.5≤-12≤-10极化方式左旋圆双极化双极化轴比/dB0.2@90°--半功率波束宽度/(°)5@90°12@90°30@90°

3 结束语

针对目前相控阵天线阵列和毫米波收发芯片存在的集成度低、成本高等问题。本文通过采用电感峰化型低噪声放大器设计、基于功率合成结构的功率放大器设计、高精度有源移相器设计、高低温温度补偿设计等创新技术,研制了一款高性能毫米波收发芯片。并通过多元法旋转馈电与圆极化天线单元设计、硅基三维高密度微系统叠层结构设计,将多功能芯片、天线阵列集成在一个微系统模块中。该微系统具有高集成度、高性能、低成本的特点,可以为高精度探测和成像等应用提供一个较优的技术路径。

[1] 赵涤燹, 陈智慧, 尤肖虎. CMOS毫米波芯片与4096发射/4096接收超大规模集成相控阵设计实现[J]. 中国科学:信息科学, 2021, 51(3):505-519.

[2] CHO Y , LEE W , PARK H C , et al. A 16-Element Phased-Array CMOS Transmitter with Variable Gain Controlled Linear Power Amplifier for 5G New Radio[C]∥ 2019 IEEE Radio Frequency Integrated Circuits Symposium(RFIC),Boston,MA,USA:IEEE, 2019:247-250.

[3] WANG Y, WU R, PANG J, et al. A 39-GHz 64-Element Phased-Array Transceiver with Built-In Phase and Amplitude Calibrations for Large-Array 5G NR in 65-nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2020, 55(5):1249-1269.

[4] PAN D F, DUAN Z M, WU B W, et al. A 76-81-GHz Four-Channel Digitally Controlled CMOS Receiver for Automotive Radars[J]. IEEE Trans on Circuits and Systems I:Regular Papers,2021,68(3):1091-1101.

[5] ZHAO D X, GU P, ZHONG J C, et al. Millimeter-Wave Integrated Phased Arrays[J]. IEEE Trans on Circuits and Systems I: Regular Papers, 2021, 68(10):3977-3990.

[6] KU B H, CHANG M, INAC O, et al. A High-Linearity 76-85-GHz 16-Element 8-Transmit/8-Receive Phased-Array Chip with High Isolation and Flip-Chip Packaging[J]. IEEE Trans on Microwave Theory and Techniques, 2014,62(10):2337-2356.

[7] GU X X, LIU D X, BAKS C, et al. An Enhanced 64-Element Dual-Polarization Antenna Array Package for W-Band Communication and Imaging Applications [C]∥2018 IEEE 68th Electronic Components and Technology Conference(ECTC), San Diego, CA, USA:IEEE, 2018:197-201.

[8] GOETTEL B, WINKLER W, BHUTANI A, et al. Packaging Solution for a Millimeter-Wave System-on-Chip Radar[J].IEEE Trans on Components,Packaging, and Manufacturing Technology,2017,8(1):73-81.

[9] FRANK M , REISSLAND T , LURZ F , et al. Antenna and Package Design for 61-and 122-GHz Radar Sensors in Embedded Wafer-Level Ball Grid Array Technology[J]. IEEE Trans on Microwave Theory and Techniques, 2018, 66(12):5156-5168.

[10] MOSTAJERAN A , CATHELIN A , AFSHARI E . A 170 GHz Fully Integrated Single-Chip FMCW Imaging Radar with 3-D Imaging Capability[J]. IEEE Journal of Solid-State Circuits, 2017, 52(10):2721-2734.

[11] KODAK U, RUPAKULA B, ZIHIR S , et al. 60-GHz 64-and 256-Element Dual-Polarized Dual-Beam Wafer-Scale Phased-Array Transceivers with Reticle-to-Reticle Stitching[J]. IEEE Trans on Microwave Theory and Techniques, 2020, 68(7):2745-2767.

[12] LI H B, CHEN J X, HOU D B, et al. A 94GHz Scalable 2×2 Phased-Array Receiver in SiGe BiCMOS for High Data-Rate Communication [C]∥2021 IEEE Custom Integrated Circuits Conference(CICC), Austin,TX,USA:IEEE,2021:71-73.

[13] HUANG D , ZHANG L , ZHU H B, et al. A 94GHz 2×2 Phased-Array FMCW Imaging Radar Transceiver with 11dBm Output Power and 10.5dB NF in 65nm CMOS[C]∥ 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC),Boston, MA, USA:IEEE, 2019:47-50.

[14] AFROZ S, KOH K J. W-Band (92-100 GHz) Phased-Array Receive Channel with Quadrature-Hybrid-Based Vector Modulator[J]. IEEE Trans on Circuits & Systems I Regular Papers, 2018,65(7):2070-2082.

[15] SHAHRAMIAN S , HOLYOAK M J , BAEYENS Y . A 16-Element W-Band Phased-Array Transceiver Chipset with Flip-Chip PCB Integrated Antennas for Multi-Gigabit Wireless Data Links[J]. IEEE Trans on Microwave Theory and Techniques, 2018,66(7):3389-3402.