0 引 言

随着21世纪无线通信技术的飞速发展,人们对于无线通信的需求越来越大。我们所熟知的WLAN、Bluetooth、个人移动通信、遥控模型等工作频段全集中在8 GHz以下,最新的5G NR通信技术已经向着毫米波发展,其Frequency Range 2(FR2)频率范围为24.25~52.6 GHz。然而随着通信制式的增多,有限的频谱资源问题越来越凸显出来[1]。因此,为了追求更高的通信速率、更大的信道容量,朝着毫米波频段进军是无线通信发展的必然趋势。目前,依托于相控阵(Phased Array,PA)技术的各类有源、无源相控阵雷达(Phased Array Radar,PAR)发展较为成熟,已经可以应用于毫米波无线通信。其中,雷达片上系统(RoC,Radar-on-Chip)是一种新兴的雷达传感器技术,RoC装置将整个毫米波 RF组件(无线收发机)、DSP和MCU集成在一个芯片上,可以显著降低雷达的价格和尺寸。

无线收发机(Transceiver)是无线接收机和无线发射机系统的总称,它们是组成相控阵雷达的核心部件。其中,无线接收机包括低噪声放大器(Low Noise Amplifier, LNA)、混频器(Mixer)、中频放大器(IF Amp)以及各类滤波器等。由于天线接收到的射频信号微弱且干扰严重,为了保证传输到接收端后级电路的信号有较高的完整性,需要在天线之后接入高性能的低噪声放大器。低噪放作为无线接收机中第一级有源电路,既要抑制输入端噪声的干扰,又需有效放大从天线接收到的微弱信号,同时,根据级联系统噪声系数公式,LNA很大程度上决定了整个接收机的噪声性能。因此,LNA自身的噪声系数应该很小,并且要有足够高的增益。一个具有低噪声、高增益的LNA可以保证后级电路的低噪声性能,从而提高整个接收系统的灵敏度。综上所述,高性能的低噪声放大器是无线接收机中不可或缺的一部分。

对LNA的一般要求是具有尽量低的噪声系数、一定的增益及带宽、端口的匹配和低功耗等。毫米波LNA相对于低频段的LNA更难同时兼具以上特性。本文以毫米波无线通信为背景,针对W波段硅基工艺电路面临的功率增益低、效率低以及噪声差等挑战,设计了一款基于0.13 μm SiGe BiCMOS工艺的W波段高增益低噪声放大器。相较于同工艺LNA,该设计在W波段具有较高的增益以及较低的噪声,具有一定的参考意义。

1 电路设计

1.1 电路拓扑结构

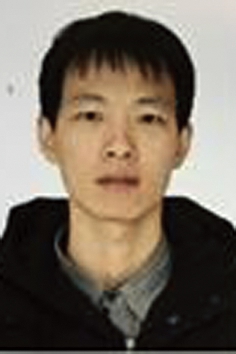

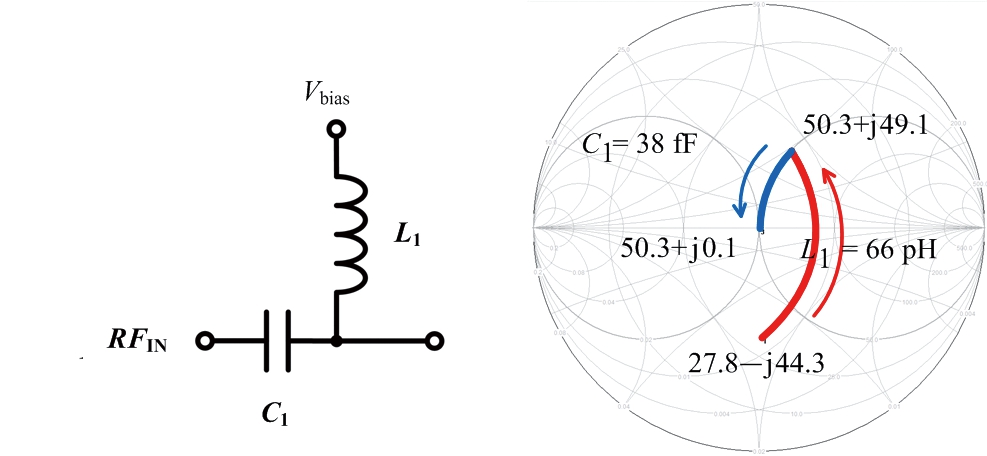

在毫米波频段,电路中元器件产生的寄生参数对电路指标影响比较大,因此在电路设计中电路结构遵循从简原则。本文设计的LNA采用带射极电感负反馈的共射极放大器的拓扑结构[2-3],如图1所示。其中,输入匹配网络(L1、C1)将LNA的输入阻抗进行最小噪声匹配,保证电路的最小噪声,晶体管Q1发射极到地通过电感LS进行信号反馈,进一步优化放大电路的噪声和输入匹配,输出匹配网络(L2、C2)将LNA的输出阻抗进行最大功率传输匹配,提供足够的增益。用于匹配网络的电容(C1、C2)同时还具有隔离直流的作用,用于匹配网络的电感(L1、L2)同时还具有扼制交流的作用。

图1 LNA拓扑结构

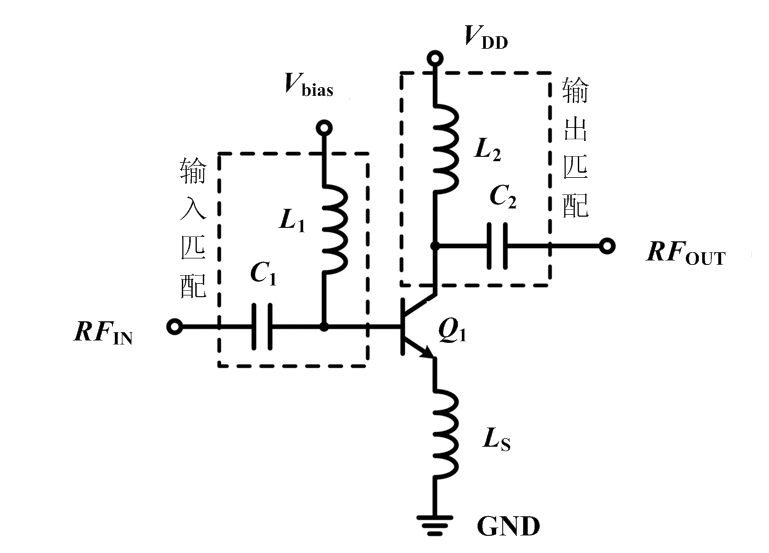

射极电感反馈结构是LNA的常用结构之一[4],如图2所示,该结构利用射极电感Le和基极电感Lb,与高频下晶体管Q1基极与发射极的寄生电容产生谐振完成输入匹配。

图2 射极反馈结构

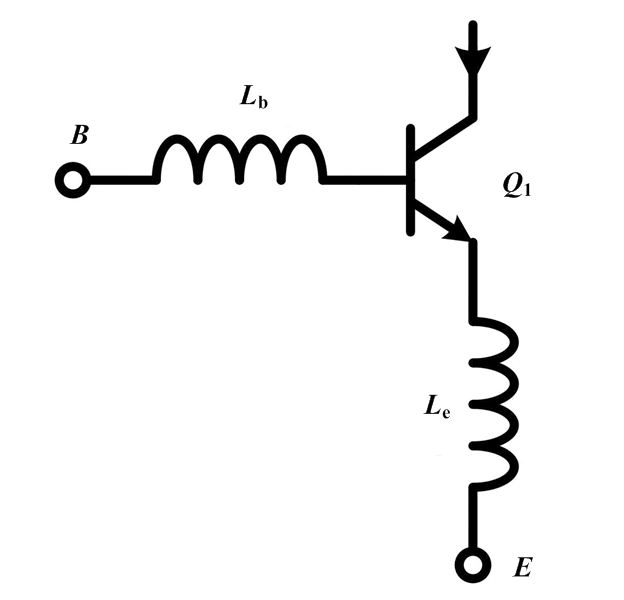

为了进一步分析,带有射极电感反馈的晶体管小信号电路如图3所示。其中,Cπ为基极与发射极之间寄生电容,Ccs为集电极到衬底的寄生电容[5]。

图3 射极反馈小信号电路

基于上述结构,从基极看入的输入阻抗ZIN表示为

ZIN=![]()

(1)

式中,

(2)

(3)

ωT≈ωβ·β0≈β(ω)ω

(4)

该结构仅通过电感消除了晶体管在高频时的主要寄生。在本文设计中,为了电路结构的简化,省略了基极电感Lb的设计。

1.2 晶体管设置

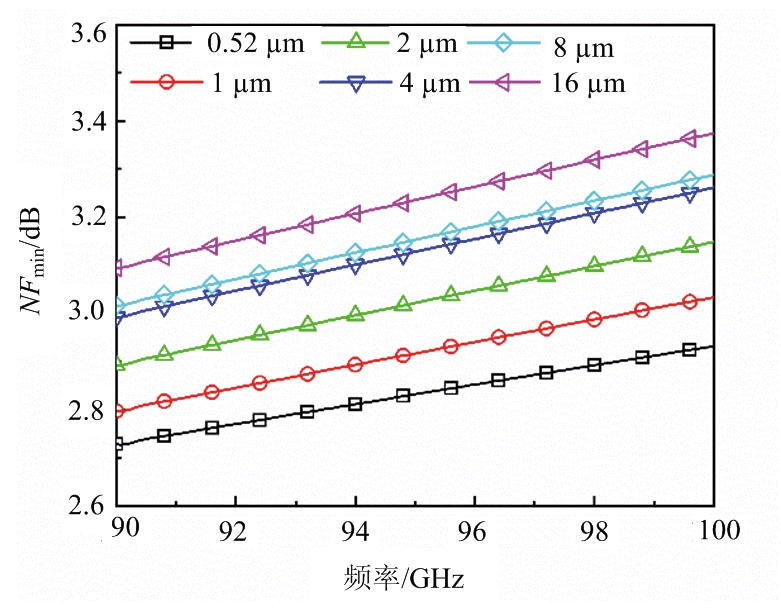

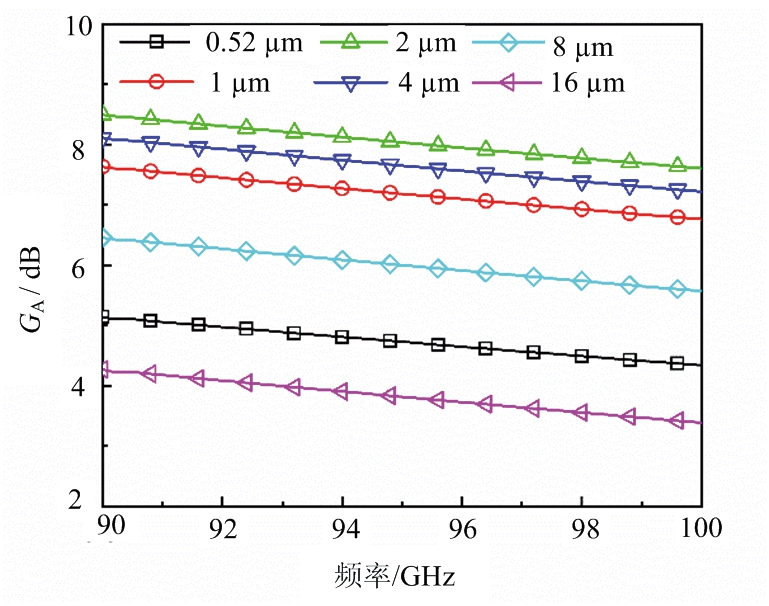

在0.13 μm SiGe BiCMOS工艺库中,射频晶体管的发射极长度范围为0.52~18 μm。为获得94 GHz时共射结构下的晶体管在不同发射极长度的最小噪声系数(NFmin)与可获得增益系数(GA),本文分别取发射极长度为0.52, 1, 2, 4, 8和16 μm进行仿真,同时电源电压VDD设为1.5 V,偏置电压Vbias设为850 mV。NFmin仿真结果如图4所示,可以看出晶体管发射极尺寸越长,噪声越大,因此在LNA的设计中,晶体管优先选用最小尺寸。但从图5可以看出过小的尺寸导致增益过低,折中选择晶体管发射极长度为2 μm。

图4 最小噪声NFmin与晶体管尺寸的关系

图5 可获增益GA与晶体管尺寸的关系

图6 Smith圆图NC与GAC

图7 GA、NFmin与Vbias的关系

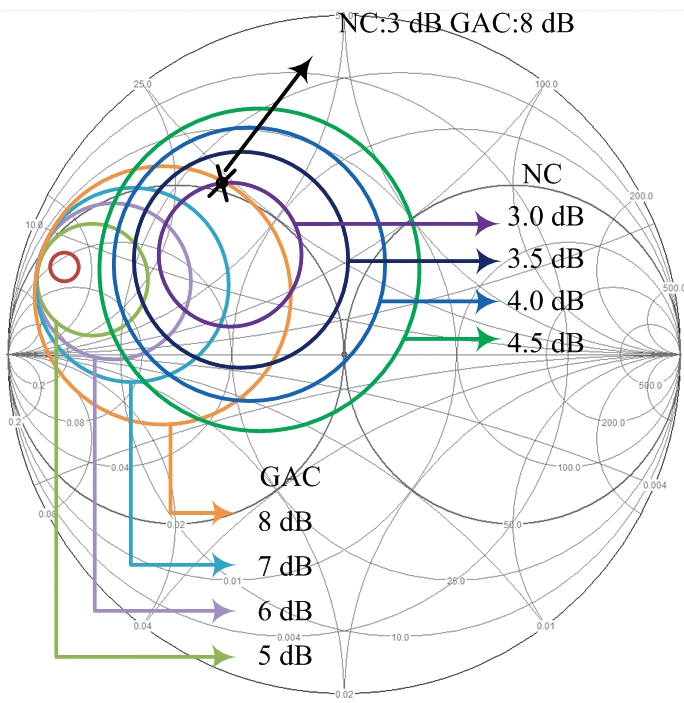

为了使电路的噪声和增益性能更直观表现,测得94 GHz时晶体管发射极2 μm尺寸下的电路噪声系数圆(Noise Circles)与可获得增益系数圆(Gain Available Circles),如图6所示。对于已设定好的晶体管尺寸,单级电路的最小噪声系数为3 dB,可获得增益系数为8 dB。如图7所示为94 GHz时晶体管发射极在2 μm尺寸下,GA、NFmin与Vbias的关系。为了电路的低噪声性能,第一级偏置电压Vbias1选择850 mV,为了电路的高增益性能,后级偏置电压Vbias2选择880 mV。

1.3 阻抗匹配

为了最小化电路的噪声,需要对输入端进行最小噪声匹配,即经过匹配网络阻抗变化之后的输入阻抗,应与放大器最小噪声系数的最佳噪声源阻抗一致。值得注意的是,在最小噪声匹配情况下,电路输入端口的反射系数会比较大,因此输入阻抗需要在噪声系数与输入反射系数两者进行折中,在尽可能保证电路低噪声的同时,满足输入端的反射系数要求。在本次设计中输入匹配网络如图8(a)所示,LNA输入阻抗匹配主要的参考指标为最佳噪声反射系数Gmin和输入端反射系数S11。匹配前射频输入端的阻抗为27.8-j44.3,通过调节输入匹配网络中无源器件的电抗值使Gmin阻抗值尽量接近50 Ω,在Smith圆图中变化如图8(b)所示。用于输入阻抗变换的串联电容C1大小为38 fF,并联电感L1的大小为66 pH。

(a) (b)

图8 输入匹配网络及Gmin阻抗变化

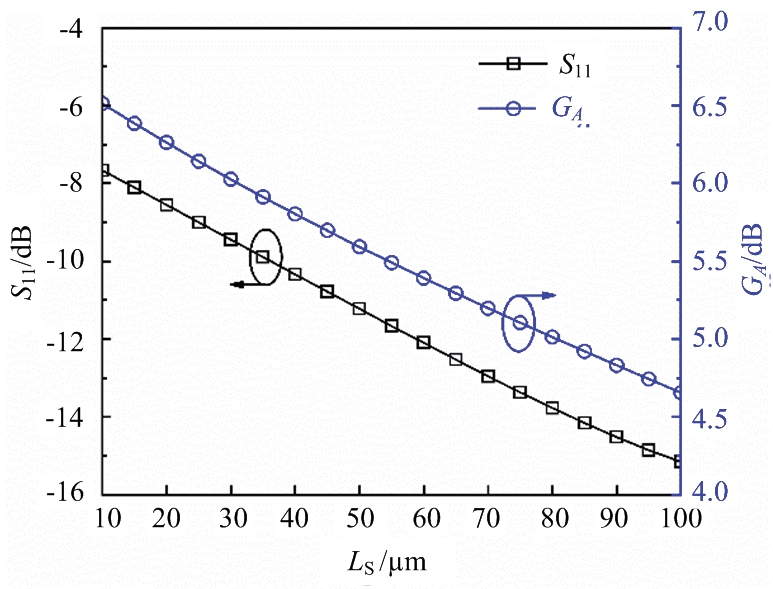

输入端最小噪声匹配完成后,通过调节射极反馈电感进一步优化输入匹配。如图9所示为S11、GA大小随射极反馈电感LS大小的变化。LS采用微带线的形式,以微带线的长度作为自变量(线宽设为8 μm),随着微带线长度的增加,反馈电感LS的电感量增加,S11显著减小。同时,因为有反馈的加入,会导致放大器的可获增益GA也随之下降。在本文设计中,为了折中考虑S11和GA的值,最终选择微带线LS的长度为60 μm,对应的电感量为23 pH。

图9 射极电感LS对S11、GA的影响

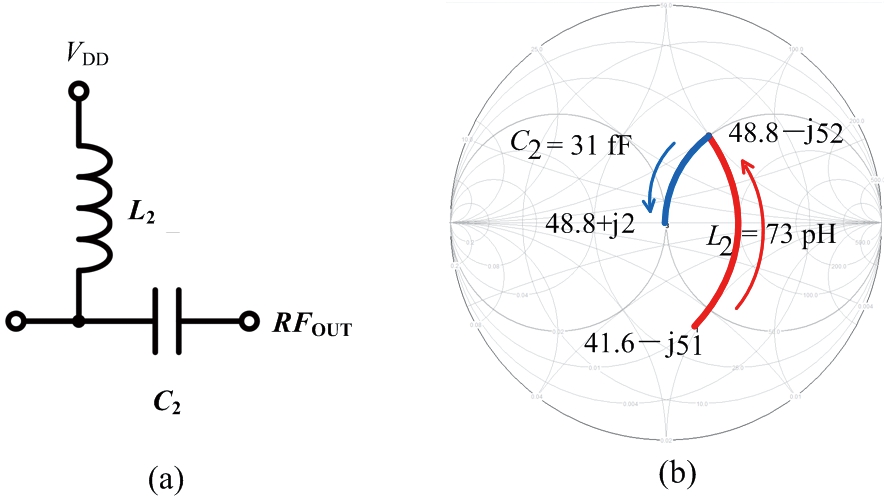

电路输出匹配结构如图10(a)所示,用并联电感L2和串联电容C2组成L型匹配网络。匹配前射频输出端的阻抗为41.6-j51,通过调节输出匹配,使得经过匹配网络阻抗变换的输出阻抗应尽量接近50 Ω。在Smith圆图中变化如图10(b)所示,确定用于输出阻抗变换的并联电感L2为73 pH,串联电容C2为31 fF。

图10 输出匹配网络及S22阻抗变换

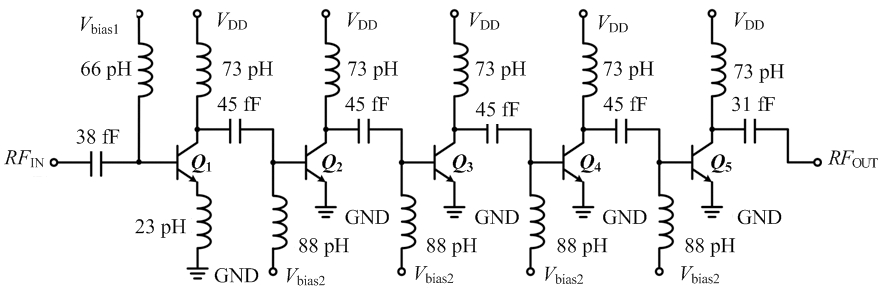

1.4 整体电路

为了保证电路的高增益,电路设计采用五级共发射极放大器级联,如图11所示。每级晶体管发射极尺寸相同,均为2 μm,保证了整体结构上的统一。第一级电路采用提供最小噪声的偏置电压850 mV,并在发射极并联反馈电感对噪声以及输入阻抗进行调谐。后级电路采用提供最大增益的偏置电压880 mV,以最大化单级电路的增益。各级之间通过级间共轭匹配保证信号的最大功率传输。

图11 LNA电路原理图

2 版图设计

射频电路版图的设计与传统电路版图绘制不同,射频电路的版图不仅要遵循版图设计规则(DRC、LVS等),还要考虑到各器件之间电磁场的相互影响。通过电磁仿真来确定电路的走线方式以减少各元件的电磁场对信号的相位以及准确性的影响。因此在布局布线过程中,应尽量减少不必要的走线。

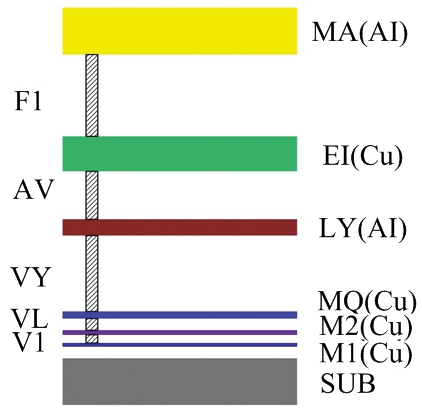

本文所使用的0.13 μm SiGe BiCMOS 8XP工艺包括六层金属,结构如图12所示。从底层到顶层分别为M1-M2-MQ-LY-E1-MA,V1、VL、VY、AV、F1分别表示为M1与M2、M2与MQ、MQ与LY、LY与E1、E1与MA之间的金属通孔。层数越高的金属层越厚,且距离衬底的距离也越远,有效降低了到衬底的损耗。在相同频率、相同电流大小时,厚金属层受趋肤效应所产生的寄生电阻影响也相对较小。因此在不考虑金属层材料的情况下,顶层金属在版图布局布线中有绝对的优先级。但是,顶层金属MA材料为Al,次顶层金属E1材料为Cu,考虑到Cu与Al导电性能的差异,折中选用次顶层E1作为主布线金属层。

图12 工艺金属层结构示意图

图13 LNA电路整体版图

LNA电路整体版图如图13所示,电路主体从左到右分别为第一级电路到第五级放大电路,SIN为射频信号输入端,SOUT为射频信号输出端。射频通路布线主要使用线宽为8 μm的次顶层金属E1,且为了降低电磁耦合与其他支路至少保持20 μm的间距。由于电路中用于匹配的电感量较小,因此版图中采用接地共面波导(Grounded Coplanar Waveguides,GCPW)的结构,其占用了版图中大部分的面积。同时,GCPW中信号线选用次顶层金属E1,地线选用最底层金属M1,较远的距离减小了信号与地之间的寄生电容,使得相同长度下的共面波导具有更高的电感量。另外,版图中还应用底层金属M1进行了大面积的铺地,使所有元器件共用一个地信号,降低了高频下地信号的寄生电感。版图总面积为500 μm×960 μm。

3 后仿结果

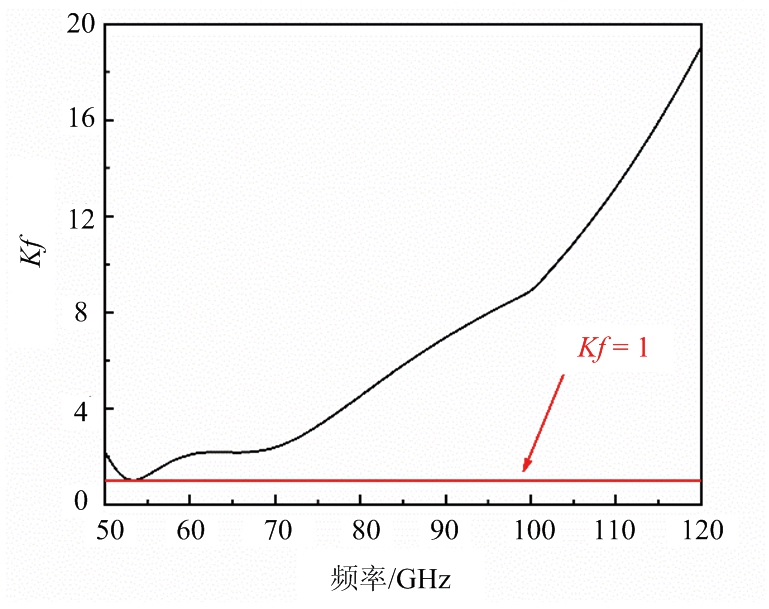

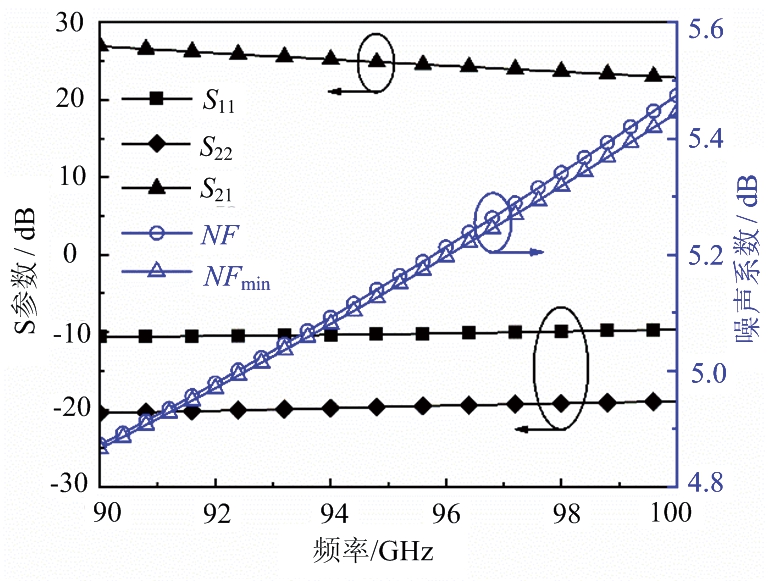

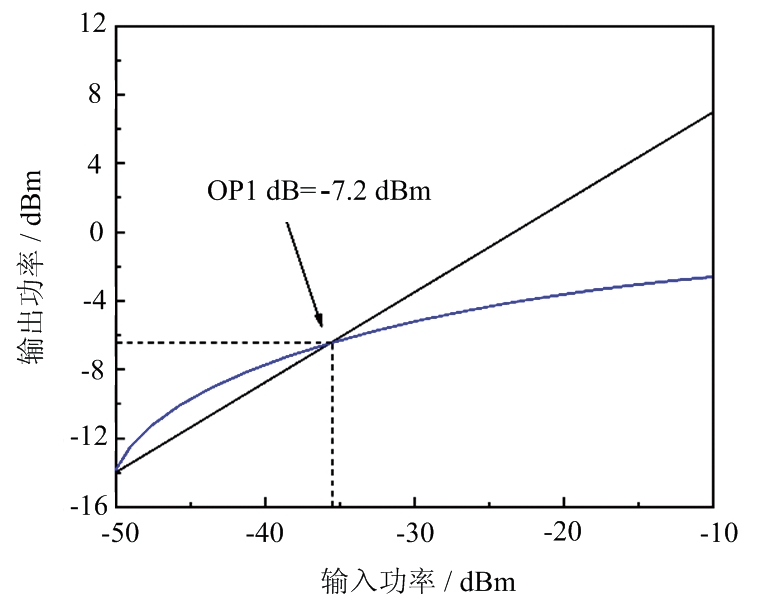

为了保证仿真结果的准确性,本文采用有源电路通过Calibre仿真、无源电路通过Momentum仿真的联合仿真的方式。稳定因子Kf后仿结果如图14所示,放大器稳定因子Kf在50~120 GHz时恒大于1,电路无条件稳定。S参数与噪声系数的仿真结果如图15所示,在中心频率94 GHz时,噪声系数NF为5.1 dB,且与最小噪声系数NFmin差距小于0.1 dB,功率增益S21为25.2 dB。在90~100 GHz内,输入反射系数S11小于-10 dB,输出反射系数S22稳定在-20 dB左右。电路的线性度指标输出1 dB压缩点(Output 1 dB Gain Compression Point,OP1dB)如图16所示,为-7.2 dBm。将本文与部分文献中低噪声放大器的性能参数进行对比,结果如表1所示。表中的对比文献均采用SiGe BiCMOS工艺。可以看出,本文设计的低噪声放大器在噪声和增益性能比较均衡,具有一定的优势。

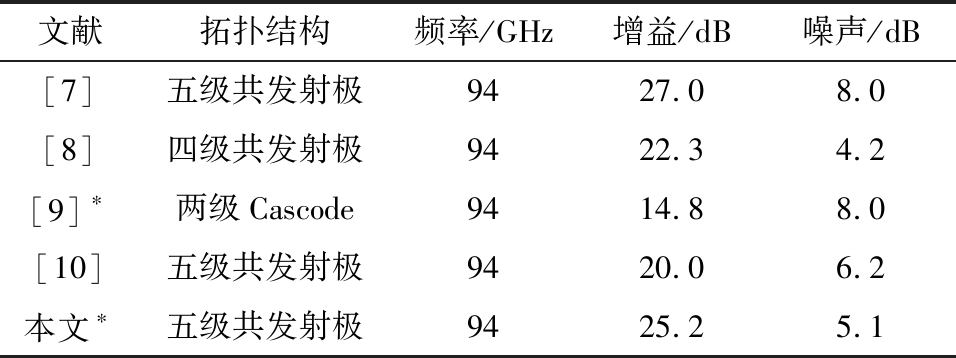

表1 与部分文献中低噪声放大器性能参数的对比

文献拓扑结构频率/GHz增益/dB噪声/dB[7]五级共发射极9427.08.0[8]四级共发射极9422.34.2[9]∗两级Cascode9414.88.0[10]五级共发射极9420.06.2本文∗五级共发射极9425.25.1

*表示仿真结果。

图14 稳定因子Kf后仿结果

图15 S参数与噪声系数后仿结果

图16 OP1dB后仿结果

4 结束语

本文基于0.13 μm SiGe BiCMOS工艺,设计了一款工作在W波段的高增益低噪声放大器,芯片面积为500 μm×960 μm。仿真结果表明,低噪声放大器在中心频率94 GHz处的增益S21达到25.2 dB,噪声系数NF小至5.1 dB。在90~100 GHz频段内,输入反射系数S11小于-10 dB,输出反射系数S22稳定在-20 dB左右。相较于同类工艺,整体电路具有高增益、低噪声的特点,对W波段低噪声放大器的研究具有一定的参考价值。

[1] 王晓海. 毫米波通信技术的发展与应用 [J]. 电信快报, 2007(10):19-21.

[2] KATZ O, BEN-YISHAY R, CARMON R,et al. High-Power High-Linearity SiGe Based E-Band Transceiver Chipset for Broadband Communication [C] ∥ IEEE Radio Frequency Integrated Circuits Symposium, Montreal, QC, Canada:IEEE , 2012:115-118.

[3] SONG P, ULUSOY A, SCHMID R, et al. A High Gain, W-Band SiGe LNA with Sub-4.0 dB Noise Figure [C] ∥ IEEE MTT-S International Microwave Symposium (IMS2014), Tampa, FL, USA:IEEE, 2014:1-3.

[4] 赵君鹏, 吴凯翔, 曹军,等. 一种SiGe D波段高增益低噪声放大器 [J]. 微电子学, 2020, 50(1):36-40.

[5] SHAEFFER D, LEE T. A 1.5-V, 1.5-GHz CMOS Low Noise Amplifier [J]. IEEE Journal of Solid-State Circuits, 1997, 32(5):745-759.

[6] XU L J, WANG Z G, XIA J, et al. Design of 60-GHz LNA in 0.13-μm SiGe BiCMOS [C] ∥ Global Symposium on Millimeter Waves, Nanjing, China:IEEE, 2008:306-309.

[7] MAY J, REBEIZ G. Design and Characterization of W-Band SiGe RFICs for Passive Millimeter-Wave Imaging [J]. IEEE Trans on Microwave Theory and Techniques, 2010, 58(5):1420-1430.

[8] USTUNDAG B, TURKMEN E, BURAK A, et al. Front-End Blocks of a W-Band Dicke Radiometer in SiGe BiCMOS Technology [J]. IEEE Trans on Circuits and Systems II:Express Briefs, 2020, 67(11):2417-2421.

[9] 庞东伟, 陈涛, 施雨,等. 120 nm SiGe BiCMOS 90-100 GHz低噪声放大器 [J]. 微电子学, 2018, 48(2):173-177.

[10] CHENG X, HAN J, LUO X, et al. A Chip Set of LNA, PA, Octupler, Mixer and Transceiver at W-Band in SiGe BiCMOS Technology for FMCW Applications [C] ∥ IEEE MTT-S International Wireless Symposium, Shanghai, China:IEEE, 2020:1-3.