0 引 言

随着无线通信领域新兴技术的发展,人们对数据传输速度的需求迅速提升,给诸如第五代移动通信系统(5G)带来了许多挑战[1-2]。许多新的波段,包括毫米波和6 GHz 以下的波段,特别是C 波段,分配给5G 通信来满足高数据传输速度的要求。因此,需要采用大规模多输入输出技术来提高频谱效率。同时,功率放大器(PA)的数量通常也达到64 或128 个。因此,大大降低了单位功率放大器的功率要求。此外,单位PA 小型化来确保系统保持合理的尺寸[3]。基于高功率密度和高效率的GaN 技术的单片微波集成电路(MMIC)在这些应用中非常有前景。

具有大峰值平均功率比(PAPR)的频谱高效调制技术用来提高5G 网络速度,这对功率放大器的功率回退效率(PBO)提出了严格的要求。因为功率放大器的平均效率主要由其回退时的性能决定。Doherty 类功率放大器(DPA)是目前提高回退效率最常用的结构[4]。目前科研人员已经报道了许多类型的DPAs[5-15]。文献[10]和[11]中的DPA设计实现了大带宽,但是放大器的增益和输出功率相对较低。文献[12]设计了三路的DPA 可以实现在大回退时的高效率,但是比传统设计多一路的DPA 意味着有更大的功率损耗和版图面积。文献[13]和[14]设计的用于5G 通信的DPA 展现了卓越的性能,但是饱和功率低于10 W,只在窄带下实现了高回退效率。在文献[15]中,通过调制主路和辅路晶体管的输出网络维持低的阻抗转换比来达到拓宽频带的目的。然而,因为漏极偏置电感是使用键合线实现的,所以这个DPA不是全集成的。

本文采用了一种新型的电路拓扑结构,去除了主路分支和两路合成后的后匹配网络阻抗转换网络。同时采用新型的功率分配器电路,达到了降低版图面积的目的,同时降低主路的阻抗转换比来达到拓宽频带的目的。设计了一款C 波段高效率、高增益的GaN MMIC Doherty 功率放大器。采用大尺寸晶体管来满足输出功率大于10 W,这会在一定程度上减小功率增益。

1 Doherty类功率放大器基本原理

1.1 Doherty类功率放大器拓扑结构

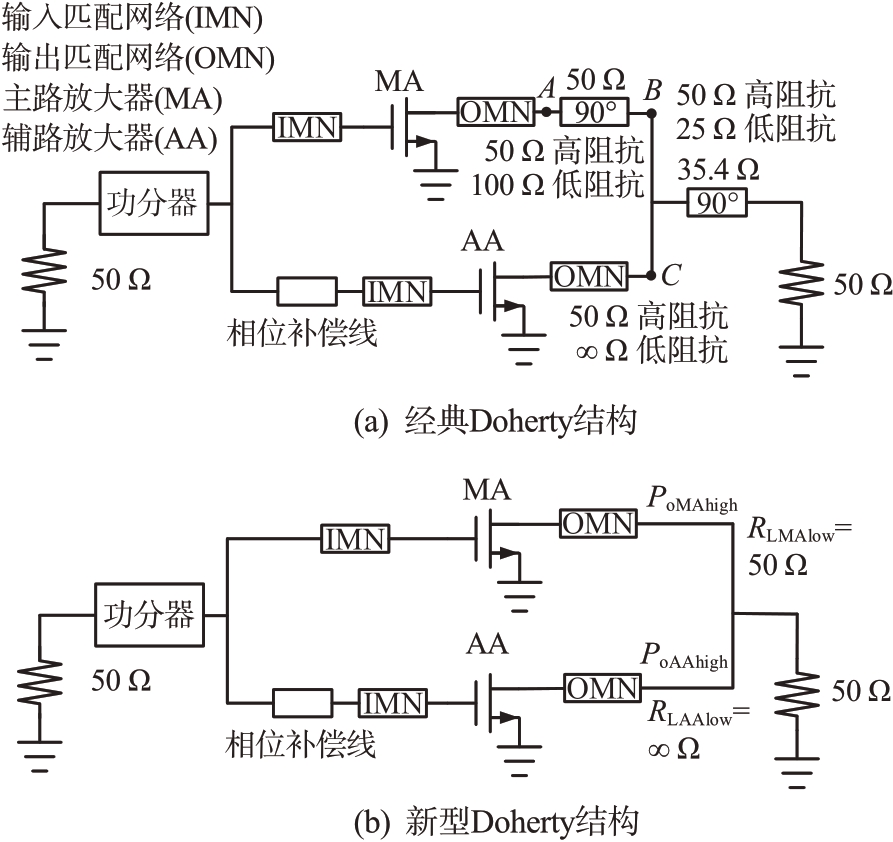

1936 年W. H. Doherty 提出了Doherty 功率放大器的结构[16]。Doherty类传统电路拓扑结构如图1(a)所示,输入信号通过功率分配器分成两路,分别通过主路放大器(载波放大器)和辅助放大器(峰值放大器),最后合并成一路输出。根据设计需求不同,功率分配器可以采用等分和不等分功率输出,主路和辅助功率放大器也可以采用不同尺寸晶体管进行设计。

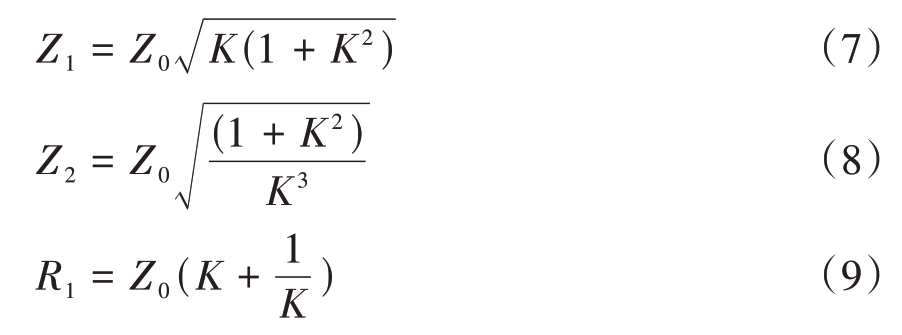

图1 Doherty类功率放大器结构

通常主路晶体管工作在AB 类,辅路晶体管工作在C 类工作状态。在图1(a)中主路放大器经过输出匹配后经过90°(λ/4,λ为波长)阻抗变换器,之后两路合路后再经过一段90°的阻抗变换器将阻抗变换为常用的50 Ω。阻抗变换器的公式由式(1)给出,其中ZA为A点的低阻抗,ZB为B点的低阻抗,最后计算结果如图1(a)所示,A 点低阻抗为100 Ω,B 点低阻抗为25 Ω,所以,阻抗转换器的阻抗转换比为100∶25=4∶1。

图1(a)中的两段50 Ω和35.4 Ω的阻抗变换线是将输出阻抗匹配到50 Ω。图1(b)为本次设计所采用的新型Doherty 功率放大器拓扑结构,可以直接将输出阻抗匹配到50 Ω,因此可以去除主路放大器中的阻抗变换器和两路合路之后的阻抗变换器,这样减少了电路设计中的组件,可以减小版图的面积,同时,因为在输出匹配中加入了负载调制的功能,所以,输出匹配电路的设计成为重点。

在Doherty 类功率放大器中,主要有两种工作模式:一种是只有主放大器工作的回退状态,另外一种是主放大器(MA)和辅助放大器(AA)共同工作的饱和状态。在这里,我们定义“低阻抗”(只有MA工作)和“高阻抗”(MA和AA共同工作)。

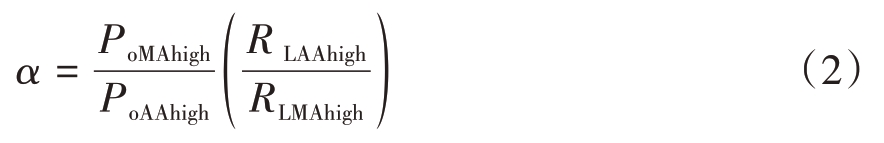

MA 和AA 的输出功率在“高阻抗”可以定义[17]为

另外,输出功率回退(OBO)值可以由下式得出:

MA和AA的负载阻抗满足以下关系:

1.2 新型功率分配器的设计

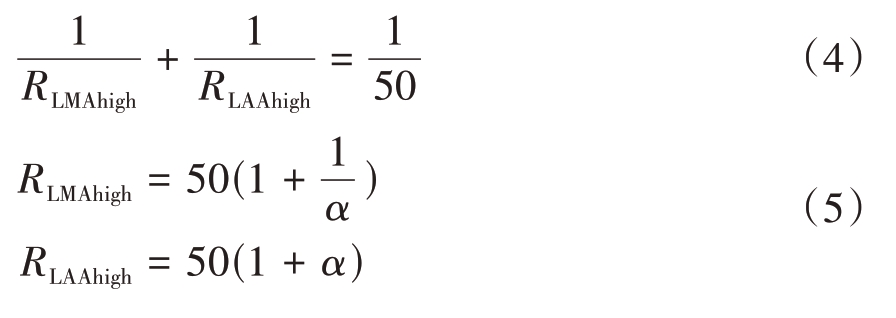

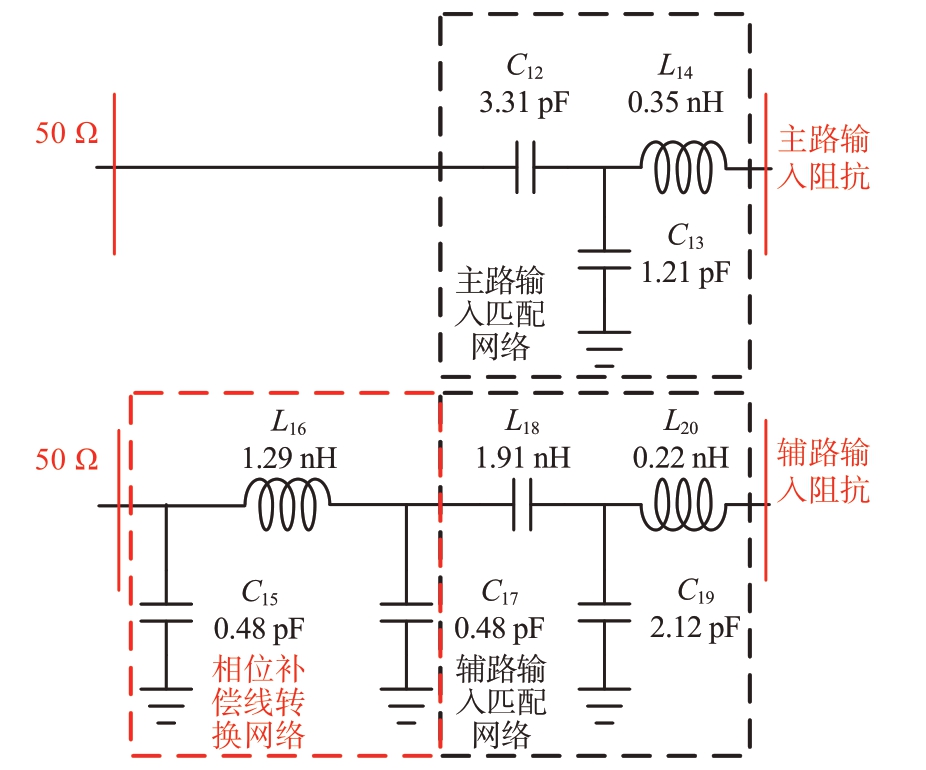

图2(a)为传统传输线形式的功率分配器的拓扑图,图中的值由下列公式给出。

图2 微带线功分器设计方法

首先假设输出端口2 和输出端口3 的输出功率分别为P2和P3。则定义K值为

由此给出其他数值:

传输线可以转化成电感和电容组成的图2(b)中的π 型网络,并且在C 波段的传输线(Z 和θ 确定)的版图面积大于其所转化的π 型网络的版图面积。所以我们采用图2(b)中的转换网络(ω为角频率)将传输线转换为π 型网络。其中参数由下式给出:

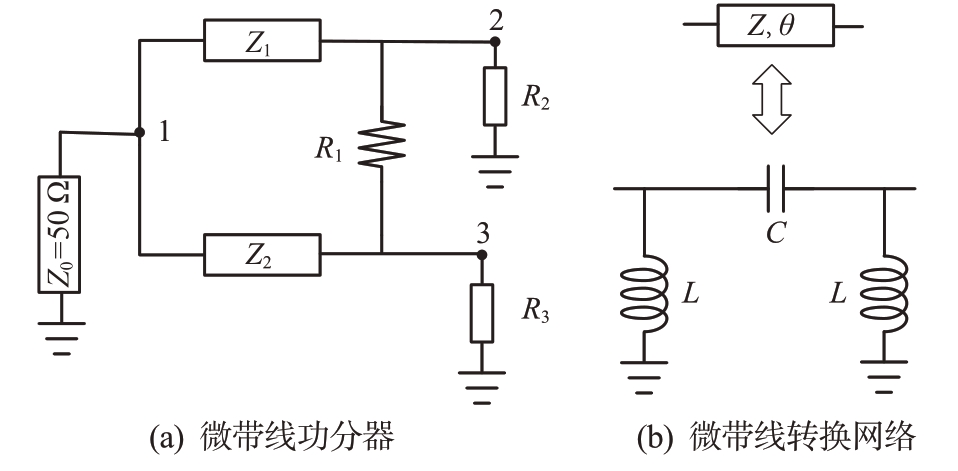

经过上述公式计算,可以得出图3(a)中的集总参数的功率分配器,这样可以减小因传输线带来的版图面积过大的问题,同时图3(a)中因为存在较多电感元件,所以本设计采取图3(b)新型等功率输出功分器,参数求解由下式给出[18]:

图3 集总参数功分器设计方法

采用的图3(b)的新型输出网络可以减小版图的面积,其中f0为频率。本次设计的Doherty 类功放的中心频率为5 GHz。根据图3(b)的拓扑结构和公式(11)~(13)计算得到L2=1.59 nH,C2=0.64 pF,R2=50 Ω。

2 Doherty类功率放大器的电路设计

2.1 输出匹配电路的设计

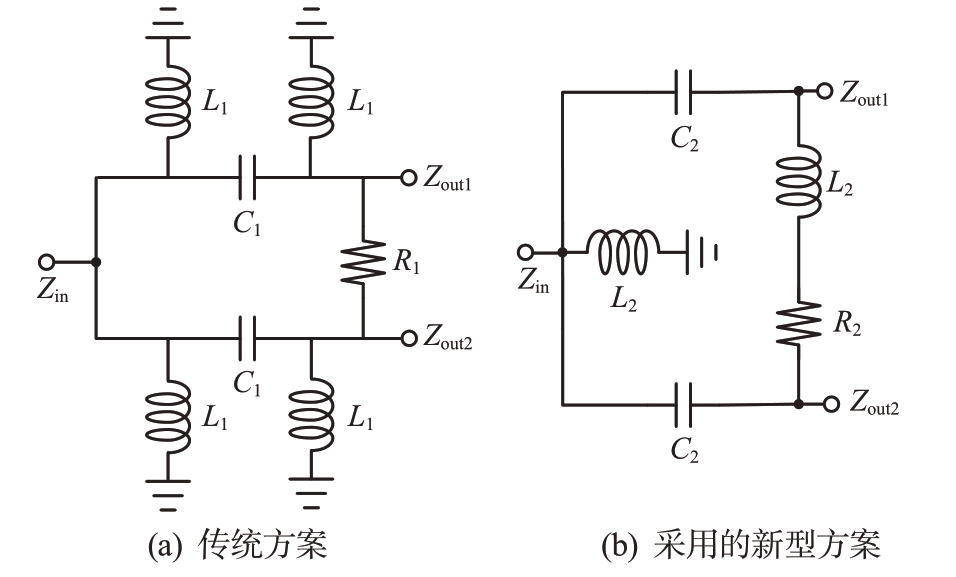

根据第1节的分析,进行输出匹配的设计。图4为新型输出匹配电路的设计,包括主路输出网络(OMN main),辅路输出网络(OMN aux),辅助放大器的补偿电感L7。本文设计的是6 dB 回退功率放大器,由公式(3)求得α=1,同时由公式(4)~(5)求得饱和时主路和辅路的输出阻抗为100 Ω,此时两路并联阻抗为50 Ω,主路放大器在回退时输出阻抗为50 Ω。很明显,该匹配网络的阻抗转换率为100∶50=2∶1,与传统结构DPA 的4∶1 的转换率相比,具有频带宽和低插入损耗的优点。补偿电感L7使得低输入功率时的辅助放大器处于开路状态,确保此时只有主路放大器工作。

图4 新型输出匹配网络

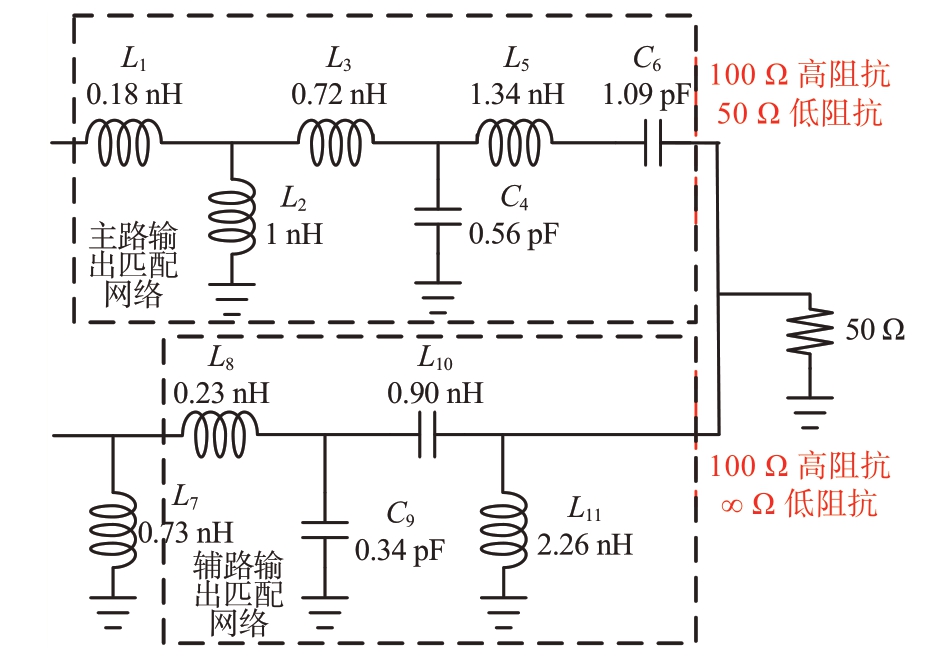

2.2 输入匹配电路的设计

图5为输入匹配网络设计,包括主路输入匹配网络、辅路输入匹配网络和相位补偿网络。值得注意的是,在输入网络设计中没有加稳定性网络,这是因为在电路设计最终网络中,整体电路在全频带内达到了稳定状态。相位补偿电路的作用是将主辅电路调节到相同的相位,减少电路因不同相位而导致损耗。

图5 输入匹配网络

2.3 Doherty类功率放大器的整体设计

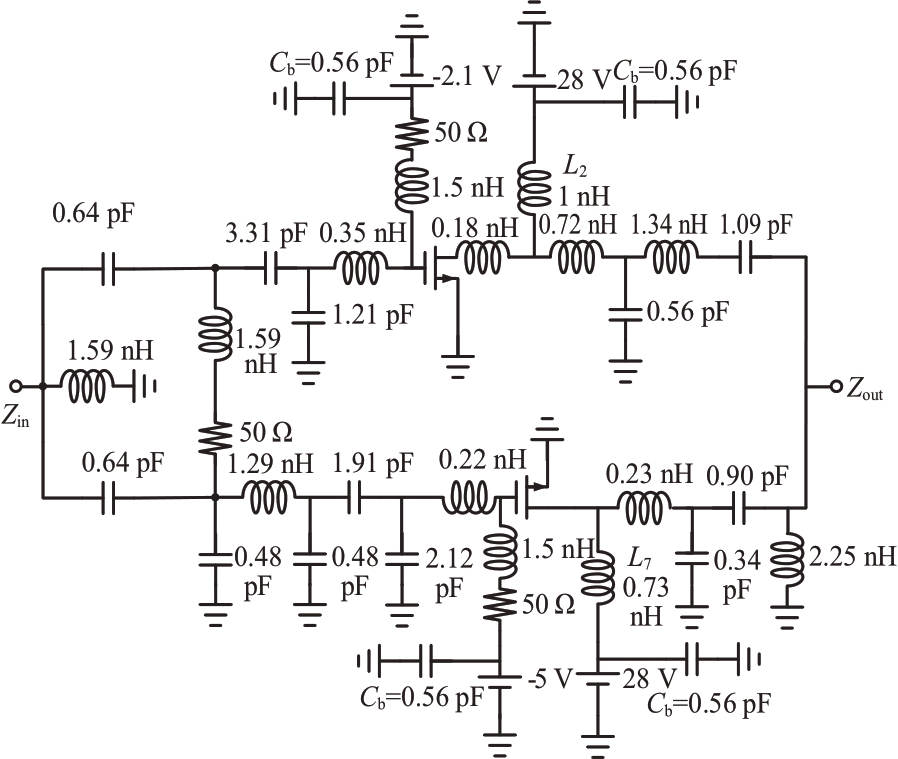

Doherty 功率放大器的整体电路原理图如图6所示。本文采用0.25 μm GaN HEMT 工艺,通过安捷伦的先进设计系统(Advanced Design System)进行仿真。主放大器采用6×300 μm 晶体管,辅助放大器采用10×300 μm 晶体管。为了减小版图尺寸,实现小型化的目的,采取集成电感和电容来设计电路,避免大量使用传输线导致版图面积的增大。值得注意的是,为了保证漏极电路能通过足够大的电流,电感L2和L7要转换为传输线,传输线的宽度所通过的电流一般为漏极通过静态电流的两倍。

图6 Doherty功率放大器的整体设计原理图

主路和辅助电路栅极电压分别为-2.1 V和-5 V,确保主路和辅路分别工作在AB 类和C 类模式,辅助支路电压的选取要保证在主路功率回退3 dB(整体DPA 回退6 dB)时辅助支路刚好开启。辅助电路开启得过早或者过晚,都会影响整体的电路性能。主路和辅路的漏极电压为28 V,同时在栅极和漏极电源处添加隔直电容Cb,来减少电源带来的杂波影响。

3 仿真结果和分析

Doherty 类功率放大器电路原理图设计完成后进行版图的设计,进而进行版图后仿真。Doherty类功率放大器的芯片版图如图7 所示,其面积为2.4 mm×1.1 mm。

图7 Doherty功放芯片版图

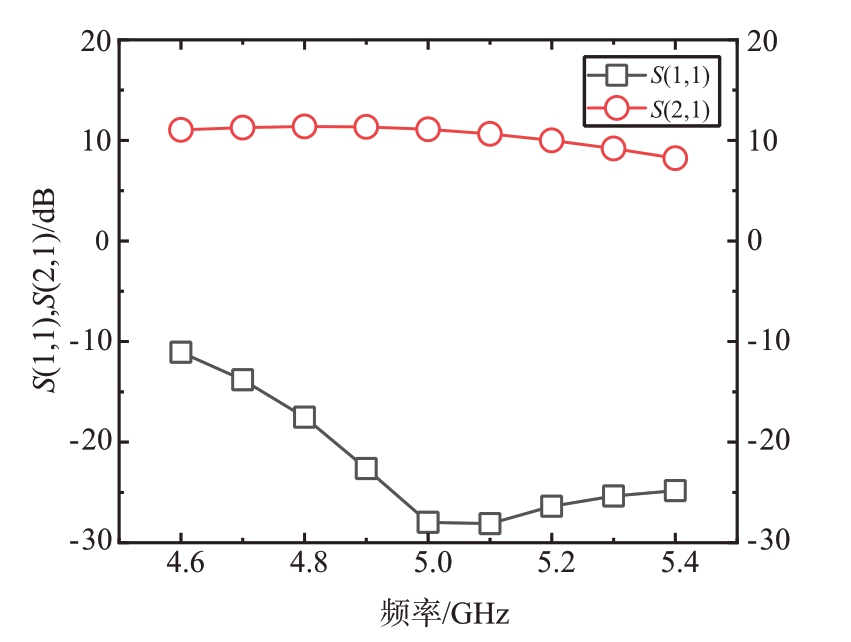

图8 为DPA 的S 参数版图后仿真结果,在4.6~5.4 GHz 的800 MHz 带宽内,小信号增益高于8.2 dB,输入回波损耗优于-10 dB。

图8 DPA的S参数

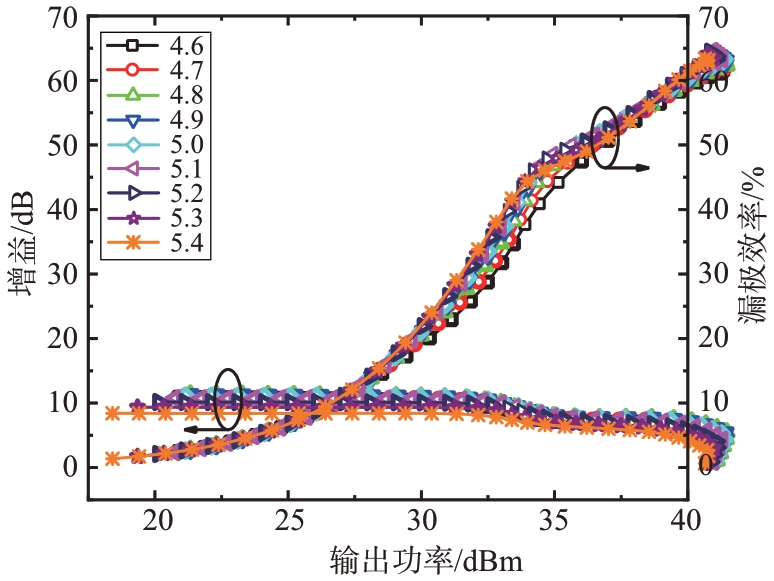

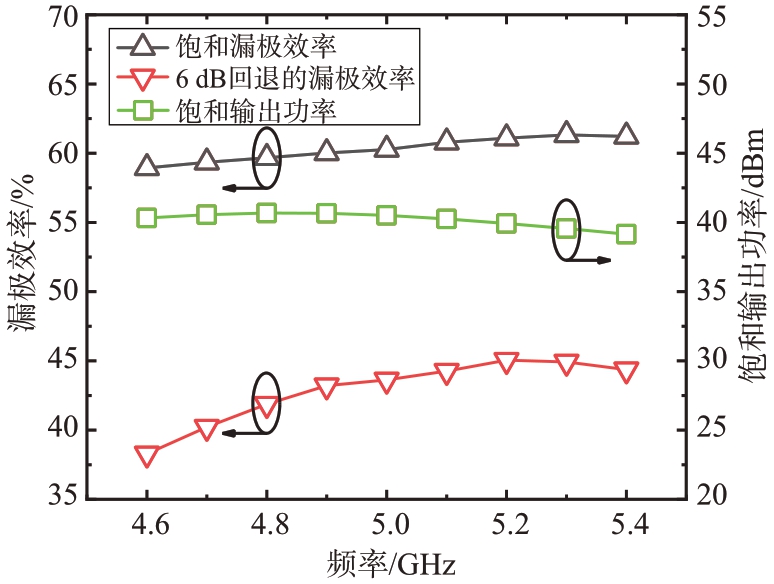

Doherty 类功率放大器的增益和漏极效率DE版图后仿真结果分别如图9 和图10 所示。图中显示了DPA 的饱和输出功率为40 dBm,在4.6~5.4 GHz 带宽内,饱和时的漏极效率(DE)为58.9%~61.3%,6 dB 回退后的漏极效率为38.3%~45.1%,增益为8.4~11.3 dB。

图9 DPA的增益和漏极效率

图10 4.6~5.4 GHz内DPA的性能

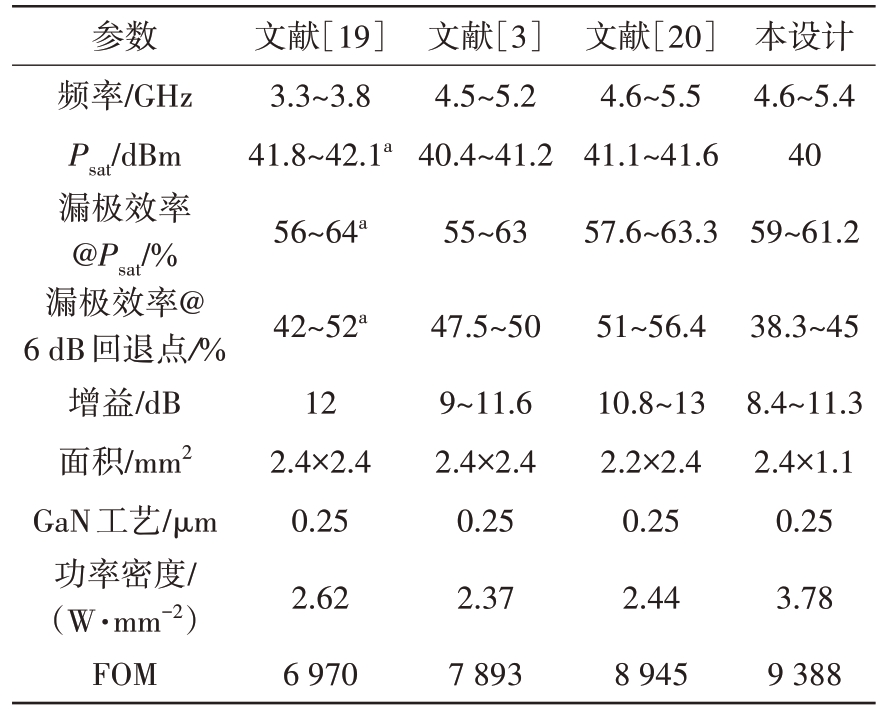

表1 给出本文设计的Doherty 类功率放大器与同类型功放的参数对比,我们定义了FOM 来评价功放的整体性能。与其他文献相比,本设计的版图面积具有较大优势,具有较高的功率密度,这对于芯片的小型化至关重要。

表1 本设计与其他Doherty功放参数对比

注:a:由图推测得到的值

FOM=(f02×AE1×AE2×AP×AG)0.5×PD

AE1:平均饱和漏极效率

AE2:平均回退漏极效率

AP:最大和最小输出功率的平均值

AG:最大和最小增益的平均值

PD:功率密度

参数频率/GHz Psat/dBm漏极效率@Psat/%漏极效率@6 dB回退点/%增益/dB面积/mm2 GaN工艺/μm功率密度/(W·mm-2)FOM文献[19]3.3~3.8 41.8~42.1a 56~64a文献[3]4.5~5.2 40.4~41.2 55~63文献[20]4.6~5.5 41.1~41.6 57.6~63.3本设计4.6~5.4 40 59~61.2 42~52a 12 2.4×2.4 0.25 2.62 6 970 47.5~50 9~11.6 2.4×2.4 0.25 2.37 7 893 51~56.4 10.8~13 2.2×2.4 0.25 2.44 8 945 38.3~45 8.4~11.3 2.4×1.1 0.25 3.78 9 388

4 结束语

随着信息化时代的到来,越来越多的便携式设备得到了广泛的应用。功率放大器作为便携式设备的重要组成部分,其性能和尺寸成为重要的指标。本文采用新型的Doherty类拓扑结构和功分器架构以及较小的阻抗转换比设计了一款工作在4.6~5.4 GHz 的新型Doherty 类功率放大器,同时验证了理论的可行性。设计的功放在相近的性能下具有更小的尺寸,更适用于便携式设备的应用。

[1]ZHAO Xiaoyin, LIU Guiqing, LI Peng, et al. Multi-Independent Logical Cells under 5G Radio Access Network Sharing of Mobile Operators[C]//Proceedings of 2022 IEEE International Symposium on Broadband Multimedia Systems and Broadcasting,Bilbao,Spain:IEEE,2022:1-5.

[2]QIAN Peng, HUYNH V S H, WANG Ning, et al. Remote Production for Live Holographic Teleportation Applications in 5G Networks[J]. IEEE Trans on Broadcasting,2022,68(2):451-463.

[3]LV Guansheng, CHEN Wenhua, LIU Xin, et al. A Fully Integrated C-Band GaN MMIC Doherty Power Amplifier with High Efficiency and Compact Size for 5G Application[J].IEEE Access,2019,7:71665-71674.

[4]SHI Wen, HE Songbai, SHI Weimin, et al. Design of a CBand High-Efficiency Doherty Power Amplifier with Harmonic Control[J]. IEEE Microwave and Wireless Components Letters,2022,32(7):875-878.

[5]童富,刘海文,曹锐,等.Doherty功率放大器的研究进展[J].雷达科学与技术,2008,6(5):378-382.

[6]SEIDEL A, WAGNER J, ELLINGER F. 3.6 GHz Asymmetric Doherty PA MMIC in 250 nm GaN for 5G Applications[C]//2020 German Microwave Conference, Cottbus,Germany:IEEE,2020:1-4.

[7]LV Guansheng, CHEN Wenhua, ZHANG Yu, et al. A Highly Linear GaN MMIC Doherty Power Amplifier Based on Phase Mismatch Induced AM-PM Compensation[J].IEEE Trans on Microwave Theory and Techniques, 2022,70(2):1334-1348.

[8]CHENG Peisen,WANG Quan,LI Wei,et al.A Broadband Asymmetrical GaN MMIC Doherty Power Amplifier with Compact Size for 5G Communications[J]. Electronics,2021,10(3):311.

[9]GIOFRÈ R, COLANTONIO P, GIANNINI F. A Design Approach to Maximize the Efficiency vs Linearity Trade-Off in Fixed and Modulated Load GaN Power Amplifiers[J].IEEE Access,2018,6:9247-9255.

[10]GUSTAFSSON D, CAHUANA J C, KUYLENSTIERNA D, et al. A Wideband and Compact GaN MMIC Doherty Amplifier for Microwave Link Applications[J]. IEEE Trans on Microwave Theory and Techniques, 2013, 61(2):922-930.

[11]GUSTAFSSON D, CAHUANA J C, KUYLENSTIERNA D, et al. A GaN MMIC Modified Doherty PA with Large Bandwidth and Reconfigurable Efficiency[J]. IEEE Trans on Microwave Theory and Techniques, 2014, 62(12):3006-3016.

[12]KONG Wa,XIA Jing,ZHOU Xinyu,et al.Bandwidth Extension of Three-Way Doherty Power Amplifier with Reactance Compensation Using Parallel Peaking Amplifiers[J].IEEE Access,2021,9:91661-91669.

[13]ISHIKAWA R, TAKAYAMA Y, HONJO K. Fully Integrated Asymmetric Doherty Amplifier Based on Two-Power-Level Impedance Optimization[C]//2018 13th European Microwave Integrated Circuits Conference, Madrid,Spain:IEEE,2018:253-256.

[14]LI Sihan, HSU S S H, ZHANG Jie, et al. Design of a Compact GaN MMIC Doherty Power Amplifier and System Level Analysis with X-Parameters for 5G Communications[J]. IEEE Trans on Microwave Theory and Techniques,2018,66(12):5676-5684.

[15]JEE S, LEE J, SON J, et al. Asymmetric Broadband Doherty Power Amplifier Using GaN MMIC for Femto-Cell Base-Station[J]. IEEE Transactions on Microwave Theory and Techniques,2015,63(9):2802-2810.

[16]DOHERTY W H.A New High Efficiency Power Amplifier for Modulated Waves[J]. Proceedings of the Institute of Radio Engineers,1936,24(9):1163-1182.

[17]ISHIKAWA R,TAKAYAMA Y,HONJO K.Doherty Amplifier Design Based on Asymmetric Configuration Scheme[J].IEICE Trans on Electronics,2021(10):496-505.

[18]LV Guansheng,CHEN Wenhua,CHEN Xiaofan, et al.A Fully Integrated 47.6% Fractional Bandwidth GaN MMIC Distributed Efficient Power Amplifier with Modified Input Matching and Power Splitting Network[J].IEEE Trans on Microwave Theory and Techniques,2021,69(6):3132-3145.

[19]LV Guansheng, CHEN Wenhua, LIU Xin, et al. A Dual-Band GaN MMIC Power Amplifier with Hybrid Operating Modes for 5G Application[J]. IEEE Microwave and Wireless Components Letters,2019,29(3):228-230.

[20]LIU Ruijia, ZHU Xiaowei, XIA Jing, et al. Highly Efficient Wideband GaN MMIC Doherty Power Amplifier Considering the Output Capacitor Influence of the Peaking Transistor in Class-C Operation[J]. IEEE Trans on Circuits and Systems I: Regular Papers, 2022, 69(5):1932-1942.